Навигация

Анализ и синтез JK - триггера

1.2 Анализ и синтез JK - триггера

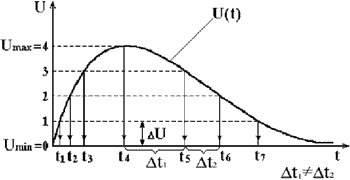

Триггер - это устройство последовательного типа с двумя устойчивыми состояниями равновесия, предназначенное для записи и хранения информации. Под действием входных сигналов триггер может переключаться из одного устойчивого состояния в другое. При этом напряжение на его выходе скачкообразно изменяется.

Как правило, триггер имеет два выхода: прямой и инверсный. Число входов зависит от структуры и функций, выполняемых триггером. По способу записи информации триггеры делят на асинхронные и синхронизируемые (тактируемые). В асинхронных триггерах информация может записываться непрерывно и определяется информационными сигналами, действующими на входах в данный момент времени. Если информация заносится в триггер только в момент действия так называемого синхронизирующего сигнала, то такой триггер называют синхронизируемым или тактируемым. Помимо информационных входов тактируемые триггеры имеют тактовый вход, вход синхронизации. На примере рассмотрим анализ и синтез JK триггера.

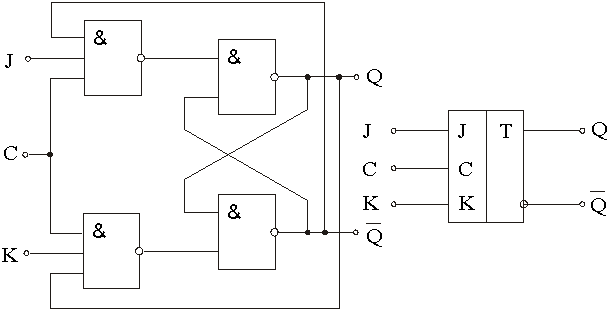

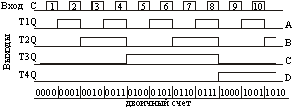

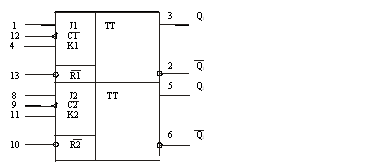

JK–триггер является одним из универсальных триггеров и имеет два информационных входа J и K. Для установки триггера в “1” необходимо подать синхроимпульс при наличии на входе J сигнала “1”, а на входе К – “0”. Поступление синхроимпульса при J = “0”, К = “1” приводит к переключению триггера в нулевое состояние. Схема JK–триггера и временная диаграмма представлены на рисунке 3.

Рисунок 3. JK- триггер

При одновременной подаче сигнала “1” на входы J и K по каждому синхроимпульсу JK–триггер изменяет свое состояние на противоположное, т.е. работает в счетном режиме.

JК-триггеры подразделяются на универсальные и комбинированные. Универсальный JК -триггер имеет два информационных входа J и К. По входу J триггер устанавливается в состояние Q = 1, ![]() = 0, а по входу К – в состояние Q = 0,

= 0, а по входу К – в состояние Q = 0, ![]() = 1.

= 1.

JК-триггер отличается от RS-триггера прежде всего тем, что в нем устранена неопределенность, которая возникает в RS-триггере при определенной комбинации входных сигналов.

Универсальность JK-триггера состоит в том, что он может выполнять функции RS-, Т- и D-триггеров.

Комбинированный JК-триггер отличается от универсального наличием дополнительных асинхронных входов S и R для предварительной установки триггера в определенное состояние (логической 1 или 0).

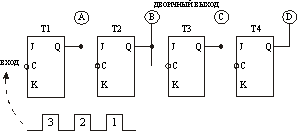

Простейший JК-триггер можно получить из синхронного RS-триггера, если ввести дополнительные обратные связи с выходов триггера на входы, которые позволяют устранить неопределенность в таблице состояний. Если входы J, К и С объединить, то получим Т-триггер, который переключается каждым входным импульсом.

При входных сигналах J = К = 0 состояние триггера не изменяется, так как напряжение низкого уровня на одном входе элемента И-НЕ отменяет прохождение сигналов от других его входов и удерживает выходной сигнал на высоком уровне. Если на входы J и К подать взаимно противоположные уровни, то при подаче перепада напряжения на вход С выходы JК-триггера устанавливаются такие же состояния. При подаче на входы J и К одновременно напряжении высокого уровня триггер переключается в состояние, противоположное предыдущему, если на вход синхронизации С подать перепад напряжения.

2. Анализ и синтез счетчика

2.1 Анализ счетчика

Один из методов проектирования счетчиков с заданным коэффициентом счета заключается в построении таблицы переходов, в первых столбцах которых будут отражены текущие состояния триггеров счетчика, а в последующих - следующие за ними состояния. Анализ таблицы позволяет установить те переходы, которые должны быть “сделаны” триггерами, входящими в состав счетчика. Затем с помощью управляющей таблицы соответствующего триггера находятся значения логических функций на управляющих входах триггеров, позволяющие осуществить эти переходы.

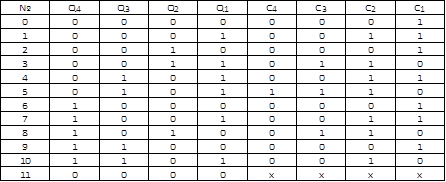

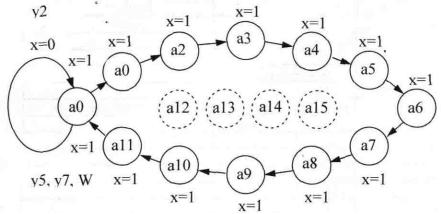

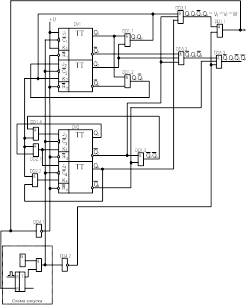

Синтезируем суммирующий асинхронный счетчик с Ксч=11, работающий в коде 6-3-2-1 на JJJJ триггерах.

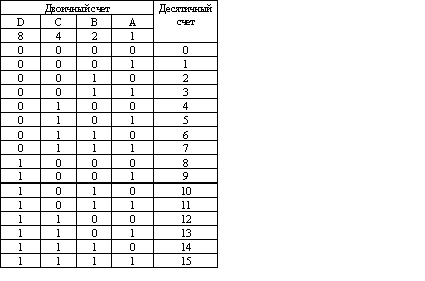

Число разрядов, необходимое для возможности подсчета Ксч импульса определяется по формуле:

M=[log2(Kсч+1)]

Следовательно:

M=log2(12+1)=4

Определим число избыточных комбинаций:

42=16;

16-12=2.

Таблица 1

Таблица содержит номер комбинации, которое соответствует числу в десятичной системе счисления(N), используемый код и соответствующие ему выходы, а также разрешающие сигналы для каждого триггера (С4,С3,С2,С1).Столбец Q1 соответствует двоичному разряду единиц или самой младшей значащей цифре (младший разряд). Столбец Q4 соответствует двоичному разряду семерок или старшей значащей цифре (старший разряд).

Столбцы с разрешающими сигналами (С1,С2,С3,С4) заполняются по принципу: 1 ставится в том случае, если в соответствующем разряде Q происходит переход из1 в 0 либо из 0 в 1, если же разряд сохраняется, то разрешающий сигнал отсутствует.

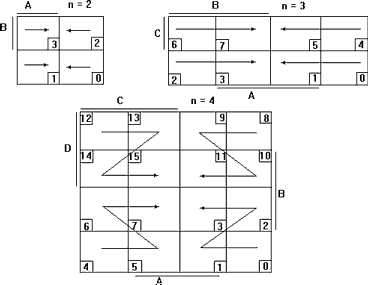

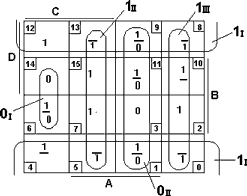

Составляем прикладные карты Карно, которые отображают переход функции из одного такта в другой:

Для функции Q1: при переходе данной функции из нулевого такта в первый она меняет свое значение с нуля на единицу. По этому в клеточке Q2Q3Q4 мы пишем 11. Если функция не меняет своего значения (например, при переходе функции из второго такта в третий значение сохраняется: 00), то мы пишем в соответствующей клеточке «Х».

Аналогично заполняются прикладные карты Карно для функций Q1n+1, Q2 n+1,Q3 n+1,Q4 n+1.

Похожие работы

... . Импульс 1 — строка 2 табл.13.2. Переключается только триггер T1, поскольку только у него на входах J и K действует уровень логической 1. T1 переходит из состояния 0 в состояние 1. Результат: на выходе счетчика 001. Импульс 2 — строка 3. Переключаются два триггера T1 и T2, поскольку на входах J и K этих триггеров действует уровень логической 1. T1 переходит из состояния 1 в состояние 0, T2 — ...

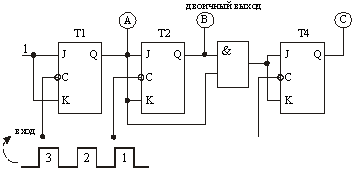

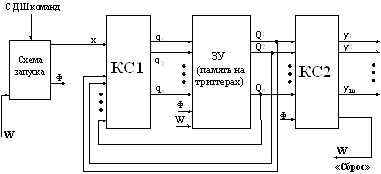

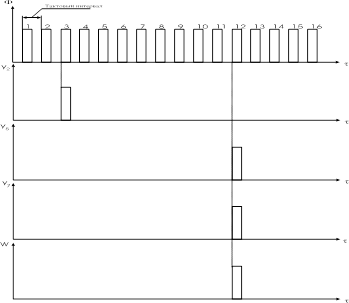

... реализацию в микропроцессоре заданной операции. Выполнение индивидуального задания позволит понять суть процессов, протекающих в устройстве управления, и самостоятельно провести анализ и синтез несложных узлов и блоков ЭВМ. 1. Порядок синтеза конечного автомата для устройства управления ЭВМ Обобщенная структурная схема конечного автомата КА (рис.1) содержит запоминающее устройство ЗУ ( ...

... показана на рисунке 8.4 Величина резистора R выбирается из условия [12] 240 Ом < R < 1,5 кОм.(8.5) Рисунок 8.4 Период генерируемых импульсов (8.6) 9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ 9.1 Комбинационные цифровые устройства (КЦУ) Логические устройства, выходные сигналы которых однозначно определяются комбинацией входных логических ...

... . с динамическим инверсным входом синхронизации несинхр. RS – триггер Т – триггер синхр. D – триггер Рис 1.14.8Регистры. Регистром называют последовательное устройство предназначенное для хранения небольшого объёма цифровой информации (числа). Один из типов регистров, последовательный регистр, позволяет производить над этим числом арифметические операции умножения и деления. ...

0 комментариев