Навигация

Корпус SoC-памяти

2.8 Корпус SoC-памяти

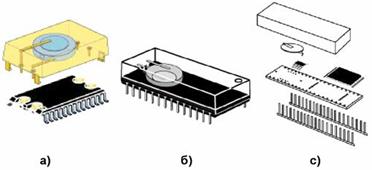

Микросхемы NVRAM доступны в различных корпусах. Основным корпусом для поверхностного монтажа (SMT) является корпус SNAPHAT (рис. 2.4 а). Микросхема в корпусе SOH 28 имеет стандартное расположение выводов SRAM, а батарея крепится сверху на застежках, что обеспечивает ее легкую замену. Корпус типа CAPHAT (рис. 2.4 б) имеет неотсоединяемую батарею. Он рекомендуется для приложений, использующих монтаж "через отверстие ".

Рисунок 2.4 – Типы корпусов SoC-памяти

Для решений с монтажом "через отверстие" и высокой плотности ОЗУ предлагается гибридный корпус DIP, в котором LPSRAM и супервизор – отдельные микросхемы, установленные на общей печатной плате вместе с батареей (рис. 2.4 с). В настоящее время доступны плотности ОЗУ до 16 Mбит.

С учетом потребностей разработчиков, одним из последних ZEROPOWER NVRAM является микросхема M48Z32V в низкопрофильном корпусе. Микросхема M48Z32V имеет LPSRAM c плотностью памяти 32 Kx8 при питании 3,3 В. Низкопрофильный корпус SOIC с 44 штырьками, возвышается над монтажной платой всего на 0.12" (3,05 мм), что предоставляет пользователям большую гибкость при компоновке платы и снимает для проектировщиков проблемы габарита по высоте.

Микросхема M48Z32V имеет встроенный коммутатор аварийного батарейного питания и цепи защиты от записи при сбоях питания совмещенные с 256 кбит маломощной SRAM. Время доступа для этих микросхем составляет 35 нс для M48Z32V-35MT1 и 70 нс для M48Z32V-70MT1.

Потребляя только 200 нА (при 40° C), M48Z32V может сохранять данные в течение десятилетнего срока службы батареи с емкостью 18 мА/ч. Эта микросхема совместима с системами, уже содержащими литиевые батареи на плате. Сочетание низкопрофильного корпуса со стоимостью M48Z32V позволяет использовать ее как удачное решение NVRAM во многих приложениях.

При использовании своих контактов для подключения к любому батарейному питанию, микросхема M48Z32V может использоваться как обыкновенное асинхронное статическое ОЗУ для любого микропроцессора или микроконтроллера.

Микросхема M48Z32V производится в корпусе SO44, который аналогичен корпусу ST типа SOH44 SNAPHAT, но без верхней батареи. Она питается от источника 3,3 В (±10%) и работает в коммерческом диапазоне температур (от 0 до 70°C).

2.9 Система реального времени в SoC-памяти

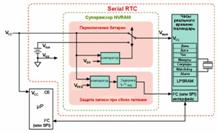

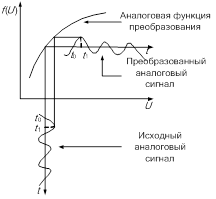

Микросхемы TIMEKEEPER NVRAM основаны на использовании базовой технологии NVRAM. Так как в микросхемах ZEROPOWER NVRAM применяется батарейное питание, то добавление часов реального времени существенно расширяет возможности микросхем NVRAM и области их применения. Свое название TIMEKEEPER такие микросхемы получили именно из-за наличия часов реального времени с календарем, которые выдают в систему точное время, день и дату даже при отсутствии внешнего системного питания (рис. 2.5).

Рисунок 2.5 – Схема системы реального времени SoC-памяти TIMEKEEPER

Микросхемы TIMEKEEPER NVRAM изготавливаются на базе ZEROPOWER NVRAM, к которым добавляется схема часов / календаря реального времени, включая кварцевый генератор на 32 кГц. Схема переключения аварийного питания, используемая для сохранения данных в LPSRAM, используется также и для RTC. Аналогично, в интересах защиты записи RTC, применяется и схема защиты записи NVRAM. Генератор RTC оптимизирован по питанию и его потребление не превышает 40 nA.

Принцип работы часов реального времени состоит в использовании генератора 32 кГц с последующим делением частоты несколькими счетчиками. Первый счетчик делит частоту генератора на 32,768 и на его выходе получается сигнал с частотой в один герц. Следующий счетчик считает количество секунд, и раз в минуту выдает сигнал на счетчик минут. Следующие последовательные счетчики продолжают деление частоты вниз вплоть до выдачи одного импульса в столетие. Для управления числом дней в каждом месяце и учета високосного года используется дополнительная логика.

Данные на выходах счетчиков соответствуют текущему времени и дате. Эти параметры переносятся в область распределенной памяти NVRAM и фигурируют как обыкновенные адреса ячеек ОЗУ. Пользователи считывают / записывают время и дату путем чтения / записи этих адресов в пространстве NVRAM.

Буферы обеспечивают "бесшовное" чтение / запись данных RTC. При чтении RTC, кадр захваченных данных о текущем состоянии реального времени сохраняется в буферах, откуда и производится считывание данных микропроцессором. Наличие кадра данных гарантирует неизменность времени в процессе очередного цикла считывания микропроцессором. Аналогично в течение цикла записи, буфера задерживают данные, поступающие от микропроцессора, и ждут конца цикла записи информации "день-дата-время" для одновременной передачи поступивших данных счетчикам часов.

РеГАСтры RTC отображаются в памяти LPSRAM. Для этого задействуется от 8 до 16 байт LPSRAM. День, дата, и время считываются и записываются в виде обыкновенных адресов ОЗУ. Имея в своем составе ZEROPOWER NVRAM, микросхемы TIMEKEEPER NVRAM сохраняют и все их основные особенности, включая отсутствие дополнительных внешних схем. При плотности памяти до 256 кбит, часы реального времени и супервизор NVRAM интегрированы на одном кристалле с LPSRAM. Для более высоких плотностей памяти используется отдельная микросхема LPSRAM. В зависимости от технологии исполнения, компоненты, составляющие микросхему, могут размещаться в одном "гибридном" корпусе, или же на одной подложке в отдельном корпусе ИС (развивающаяся технология упаковки TIMEKEEPER).

Подобно микросхемам TIMEKEEPER NVRAM последовательные часы реального времени (Serial RTC) отслеживают текущее реальное время даже при отсутствии внешнего системного питания. Вместо стандартного асинхронного параллельного интерфейса SRAM, последовательные RTC используют последовательную шину.

Данные микросхемы изготавливаются на основе TIMEKEEPER NVRAM путем уменьшения количества NVRAM до нескольких байт и изменения интерфейса к одному из стандартов, перечисленных выше.

Большинство устройств Serial RTC содержат в себе переключатель батареи, цепи защиты записи и многие другие современные функции микропроцессорного супервизора, например, сброса питания и сторожевого таймера (рис. 2.6).

Рисунок 2.6 – Схема микропроцессорного супервизора в SoC-устройствах Serial RTC

Для приложений, не требующих резервирования или нуждающихся только в краткосрочном резервировании с использованием конденсатора, выпускаются более простые и дешевые устройства Serial RTC, например, M41T0 и M41T80.

Микросхемы полнофункциональных последовательных часов реального времени имеют много функций микропроцессорного супервизора. Например: M41T81 – это Serial RTC с интерфейсом I2C 400 кГц, Alarm, программируемым Watchdog, программируемым генератором меандра, в корпусе SO8 или SOX28 типа SOIC (с встроенным в корпус кварцем). Микросхема M41T94 является первым устройством Serial RTC ST c интерфейсом SPI. В ней имеются интегрированные схемы PОR / LVD, программируемый Watchdog, Alarm, возможность подключения кнопки сброса. Микросхема выпускается в корпусах SO16 и SOH28 SNAPHAT. Микросхема Serial RTC M41ST84 с интерфейсом I2C 400 кГц выделяется расширенными возможностями микропроцессорного супервизора. Кроме функций PОR / LVD, программируемого Watchdog и Alarm она обеспечивает функцию раннего предупреждения о сбое питания (PFI / PFO) и сброс по входу. Производится в корпусе SO16.

Современные микросхемы NVRAM достигли такого уровня интеграции, что некоторые из них (M41ST85, M41ST87 и M41ST95) можно классифицировать и как Serial RTC и как TIMEKEEPER супервизоры. Достигнутый уровень интеграции позволяет теперь размещать кварц непосредственно в монолитном корпусе микросхемы рядом с кристаллом, а не выносить его к верхней батарее. Примером такого решения, обеспечивающего повышение надежности и безопасности, является микросхема М41СТ85МХ6.

Наряду с высоко интегрированными микросхемами Serial RTC, выпускаются устройства, содержащие минимум необходимого для непрерывной выдачи в систему реального времени. К таким устройствам относятся микросхемы M41T0 и M41T80. Они содержат полный набор счетчиков времени и учитывают особенности високосных лет. К дополнительным возможностям этих устройств относятся программируемый сигнал аварии с функцией обработки прерываний, программируемый выходной меандр и отдельный вывод сигнала с частотой 32 кГц, используемый как эталонный входной сигнал для тактовых генераторов других микросхем. Имея такие возможности, данные микросхемы покрывают потребности приложений в значительной части потребительского рынка.

Микросхемы M41T0 и M41T80 имеют последовательный интерфейс промышленного стандарта I2C 400 кГц и работают в индустриальном интервале температур от -40º C до +85º C. Производимые в корпусах для поверхностного монтажа, оба устройства работают от источника питания с напряжением от 2 В до 5,5 В при малом потреблении тока. Например, M41T0 потребляет только 900 нА в дежурном режиме и 35 мкА в активном режиме (при типовом питании 3,0 В). M41T80 потребляет 1,5 мкА в дежурном режиме (при типовом питании 3,0 В) и только 30 мкА в активном режиме (при максимальном напряжении питания 3,0 В).

В дополнение к основной задаче хронометрирования, в микросхеме M41T0 есть опция стопового бита генератора для обнаружения ухода частоты тактового генератора из-за уменьшения питающего напряжения. Что касается M41T80, его свойства хронометрирования дополнены программируемым прерыванием по сигналу Alarm с режимами повтора, специальным выводом частоты 32 кГц и программируемым выходным меандром с частотой от 1 Гц до 32 кГц. Специализированный вывод частоты 32 кГц может использоваться для управления микропроцессорами и микроконтроллерами со схемой фазовой синхронизации тактового генератора, которая требует 32 кГц в качестве эталона. Кроме того, этот же вывод может использоваться для тактовой синхронизации микросхем при их работе на режимах с малой мощностью. Вывод 32 кГц рассчитан для условий постоянной работы, но он может быть заблокирован программным обеспечением пользователя.

Функция аварийного сигнала (Alarm) микросхемы M41T80 имеет режим с повторением Alarm от одного раза в год до одного раза в секунду. Функция программирования меандра позволяет программировать его частоту от 1 Гц до 32 кГц с множителем 2.

Похожие работы

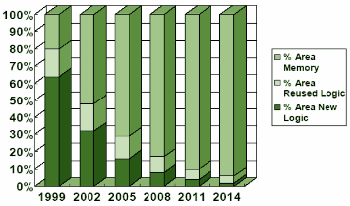

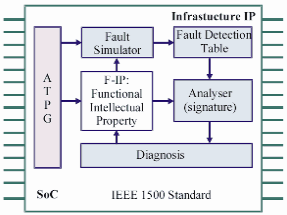

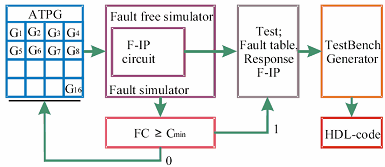

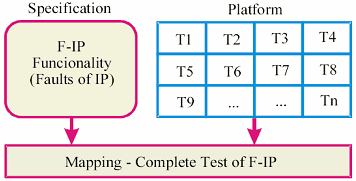

ть алгоритмическое и программное обеспечение для тестирования пакета кристаллов ГАС, в соответствии со стандартом IEEE 1500. Объект исследования – пакет кристаллов ГАС. 1. Анализ технического задания 1.1 Состояние рынка технологий сервисного обслуживания SoC Проблема диагностирования и ремонта памяти связана с тенденцией на постоянное уменьшение площади кристалла, отводимой для ...

... рисунков в формате А0-А1 со скоростью 10-30 мм/с. Фотонаборный аппарат Фотонаборный аппарат можно увидеть только в солидной полиграфической фирме. Он отличается своим высоким разрешением. Для обработки информации фотонаборный аппарат оборудуется процессором растрового изображения RIP, который функционирует как интерпретатор PostScript в растровое изображение. В отличие от лазерного принтера в ...

... также невысока и обычно составляет около 100 кбайт/с. НКМЛ могут использовать локальные интерфейсы SCSI. Лекция 3. Программное обеспечение ПЭВМ 3.1 Общая характеристика и состав программного обеспечения 3.1.1 Состав и назначение программного обеспечения Процесс взаимодействия человека с компьютером организуется устройством управления в соответствии с той программой, которую пользователь ...

... SunSoft. Кроме непосредственно разработки, в его функции также входило обеспечение лицензиями на ПО дистрибьюторов, OEM-партнеров и конечных пользователей. 8 июля 1987 г. — официальное рождение новой RISC/UNIX платформы: Sun представила компьютерному сообществу одновременно и открытую архитектуру SPARC, и первую базирующуюся на ней систему Sun-4/260, и ОС, и обширный набор прикладного ПО. ...

0 комментариев