Навигация

1 ТЕОРЕТИЧНА ЧАСТИНА

1.1 Динамічна пам’ять, принципи її організації і роботи

Однією з головних задач субмікронної технології ВІС є формування структур швидкодіючих запам’ятовуючих пристроїв (ЗП) з інформаційною ємністю більше 1 М на кристалі. Саме підвищення ступені інтеграції ВІС супроводжується зменшенням площі комірки пам’яті та споживаної потужності. Проведене моделювання дозволяє зробити висновок, що при зменшенні розмірів елементів в 1/n раз, степінь інтеграції зростає в n2 разів. Мінімальним елементом для формування структур ЗП ємністю 1М є розмір 0,8-1 мкм. Подальше зменшення розмірів елементів обмежується наступними факторами:

1) при рівності нулю напруги на затворі ключового транзистора повної відсічки не проходить, бо це вимагає подачі нульової порогової напруги (UT 0), яка залежить тільки від ступені легування підкладки і температури;

2) при зниженні напруги живлення виникають проблеми, зв’язані з явищем „короткого” каналу і інжекції гарячих електронів в під затворний діелектрик;

3) рівень порогової напруги обмежується напругою плоских зон UFB, величина якої визначається матеріалом електрода затвора та постійним зарядом в підзатворному діелектрику транзистора;

4) при співударі однієї α- частинки заряд на затворі змінюється на 0,03 пКл і для того, щоб цей заряд не змінював потенціала динамічних конденсаторів пам’яті більше, ніж на 1 В, необхідно ємність такого конденсатора зробити не меншою 0,03 пФ. Тому для подальшого підвищення ступені інтеграції ВІС простого зменшення елементів недостатньо і треба також удосконалювати як технологію формування елементів структур пам’яті, так і конструкцію самої комірки структури. Проте дане питання недостатньо висвітлене в літературі і потребує певних уточнень.

Відомо, що важливі параметри ЗП - швидкодія і споживана потужність визначаються часом доступу до даних, а в більшості ЗП використовується тільки адресний доступ. Такі ЗП є найбільш проробленими і широко використовуються в мікропроцесорних системах управління. Тому в даній статті розглянемо їх конструкторсько-технологічні особливості в рамках субмікронної технології формування їх структур. Всі адресні ЗП діляться на RAM i ROM або їх ще називають оперативними ЗП (ОЗП) і постійними ЗП (ПЗП). Оперативні ЗП зберігають дані, які приймають участь в обміні при виконанні текучої програми, і можуть бути змінені в любий момент часу. В ПЗП така вже зміна не передбачається і її використовують як пам’ять для читання. Якщо такі дані в ПЗП міняються, то її вже називають репрограмованою (РПЗП) або перепрограмованою ППЗП.

RAM (ОЗП) діляться в свою чергу на статичні і динамічні. В першому варіанті запам’ятовуючим елементом є тригер, який зберігає свій стан (0,1) доки схема знаходиться під живленням і немає нового запису даних. Для другого типу дані зберігаються у вигляді заряду конденсатора (Q0, QI), що забезпечується динамічною коміркою пам’яті, побудованою на МОН структурі (транзисторі та конденсаторі). Саморозряд конденсатора веде до знищення даних, а тому такі конденсатори повинні мати високі електричні характеристики (низькі струми втрат, високі пробивні напруги і питому ємність) і періодично регенеруватись. Регенерація даних в ОЗП здійснюється з допомогою спеціальних контролерів, які також зменшують ступінь їх інтеграції. Такі ОЗП називають квазістатичними.

Статичні ОЗП називають ще SRAM, а динамічні DRAM. В свою чергу статичні ОЗП поділяються на:

1) асинхронні, в яких управляючі сигнали задаються як рівнями, так і імпульсами;

2) синхронні, в яких управляючі сигнали представляються тільки імпульсами;

3) конвеєрні , коли такі передачі даних синхронізовані з тактовою частотою мікропроцесора.

Статичні ОЗП, маючи високу швидкодію, є основою кеш-пам’яті.

Динамічні ОЗП характеризуються максимальною інформаційною ємністю і використовуються як основна пам’ять в ЕОМ чи в мікропроцесорних системах. Одним із варіантів швидкодіючої ОЗП є пам’ять типу FPM, тобто із сторінковим режимом доступу до даних і визначається її структурою.

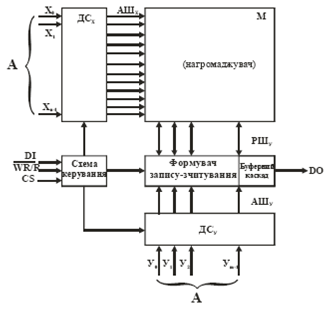

Адресні ЗП представляються статичними і динамічними ОЗП (RAM) та постійного типу ROM. Вони мають багато спільного з точки зору використання структурних схем. Це відноситься до статичних ОЗП (SRAM) та ПЗП типу ROM. Структура динамічних ОЗП має свою специфіку і будується на транзисторно-конденсаторних елементах пам’яті (одно і багато транзисторних). Типова структура для статичного ОЗП подана на мал. 1.

Малюнок 1. Структура схем пам’яті статичної ОЗП

На схемі адрес А є номером комірки нагромаджувача (матриці), до якого проводиться звертання. Тому розрядність адреса зв’язана з числом зберігаючих слів N співвідношенням n = log2N або N = 2n. Якщо ЗП ємністю 64 К має n = 16 розрядні адреси, то адрес виражається набором А = А15А14...А0. Сигнал CS-Chip Select або СЕ (Chip Enable) - сигнал, який дозволяє або забороняє роботу даної схеми. Сигнали WR/RD – Write/Read- сигнал запису-читання, який видає сигнал „1” на зчитування і „0” на запис. Сигнали DI, DO – Date input, Date output – шини вхідних і вихідних даних, розрядність яких визначається розрядністю ЗП (розрядністю його комірок). Запис в вибраний ЕП або зчитування з вибраного ЕП здійснюється з допомогою n-розрядних ФЗЗ, кожний із яких підключений до РШ одного із стовпців. Вихідні сигнали ДШу, що визначають конкретний стовпець, в якому проводиться вибірка ЕП, поступають по АШу на ФЗЗ, який і дозволяє роботу одного з них відповідно на режим запису або зчитування. В режимі запису інформації вибраний ФЗЗ формує через підключену до нього розрядну шину сигнал, що встановлює конкретний ЕП, який вже є в заданому рядку і на який подається сигнал, що поступив з дешифратора ДШХ в стані „0” чи „1” в залежності від того, який сигнал поданий на вхід схеми управління DI. В режимі зчитування відповідний ФЗЗ сприймає сигнал, що поступив на РШ від вибраного ЕП. Цей сигнал вказує на стан ЕП (Q = 0 чи 1) підсилюється і передається на вихід даних DO через буферний каскад (БК). Тобто, режим роботи ЗП дозволяє формування сигналу вибірки на АШХ і при сигналі WR/R = 0 схема управління формує сигнал на запис; при цьому вихід DO блокується буферним каскадом. Якщо WR/R = 1, то схема управління перемикає ФЗЗ в режим зчитування, при якому інформація з вибраного ЕП поступає вже на вихід DO, а вхід DI вже не впливає на роботу зчитування інформації. При CS = 1 реалізується режим зберігання, тобто ЕП не змінюється при дії любих сигналів на входах А, DI, WR/R, а DO при цьому відключається. Часова діаграма режимів запису, зчитування і зберігання в ОЗП приведена на мал. 2.

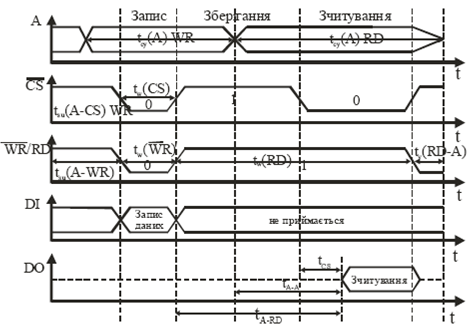

Основними параметрами ЗП є наступні часи:

1) t CY(A)WR – час циклу адреса в режимі запису;

2) t CY(A)RD – час циклу адреса в режимі зчитування;

3) t SU(A-CS) – час установлення сигналу вибірки CS відносно адреса А;

4) t SU(A-WR) – час установлення сигналу запису;

5) WR відносно адреса А;

6) t V(RD-A) – час зберігання адреса після зняття сигналу зчитування;

7) t W(CS) – тривалість сигналу вибірки CS;

8) t W(RD) – тривалість сигналу зчитування RD;

9) t W(WR) – тривалість сигналу запису WR;

10) t CS – час вибірки для зчитування;

11) t CS – час вибірки для зчитування;

Малюнок 2. Часова діаграма статичного ОЗП в режимах: запису, зберігання і зчитування

12) t A-A – час вибірки адреса;

13) t A-RD – час вибірки сигналу зчитування.

Основними часовими параметрами, що визначають швидкодію ЗП є:

1) t A(RD) – час циклу зчитування;

2) t SU(A-CS) – час установлення сигналу вибірки CS;

3) t SU(A-RD) – час установлення сигналу зчитування;

4) t CS – час вибірки для зчитування.

Для статичних ОЗП і пам’яті типу ROM найбільше застосування отримали структури типу 2D, 3D, 2DM. В структурі 2D (мал. 3) запам’ятовуючі елементи організовані в прямокутний нагромаджувач (матрицю) M = kxm, де k- число зберігаючи слів, а m - їх розрядність. Дешифратор DC при сигналі вибірки CS дозволяє одночасний доступ до всіх елементів вибраного рядка, що зберігає задане слово, адрес якого відповідає номеру рядка, а стовпець вибирається через команду RD/WR на зчитування або запис відповідно. В такій структурі число виходів дешифратора є рівним числу зберігаючи слів. Тому їх можна використовувати в ЗП малої інформаційної ємності до 64 К.

Малюнок 3. Структура ОЗП (RАМ) із словарною адресацією типу 2D

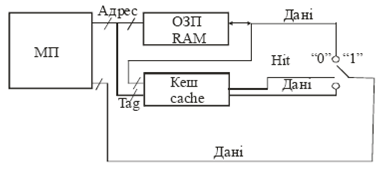

Для збільшення швидкодії запам’ятовуючих пристроїв замість адресного доступу використовують асоціативний, за допомогою якого здійснюється пошук інформації вже по визначеній ознаці (замість адресу), наприклад, по співпадінню певних полів слів, які називають тегами, з ознакою, що задається вхідним словом (теговим адресом). Таку асоціативну пам’ять називають кеш-пам’яттю (cache) або прискорюючою. Вона запам’ятовує копію інформації, що знаходиться в основній ОЗП і забезпечує швидкий доступ до неї по команді мікропроцесора. Таку швидкодіючу пам’ять, як правило, реалізують на тригерних ЕП. При читанні даних спочатку виконується звертання до КП по схемі, що зображена на мал. 4. Якщо в КП є копія даних адресованої комірки основної пам’яті ЗП, то вона виробляє сигнал Hit (співпадіння „1”) і видає дані на загальну шину. Якщо таких даних немає, то не виробляється сигнал Hit („0”) і тоді виконується читання із основної пам’яті і одночасне розміщення даних в КП. МП для прискорення передачі даних може звертатись вже безпосередньо до КП, зчитуючи ці дані і посилаючи їх через шину даних в мікропроцесорну систему. Таке поєднання адресного доступу і асоціативного прискорює роботу (звертання) МП до ЗП, тобто збільшує їх швидкодію. Таким чином, архітектура ЗП визначає не тільки швидкодію, але і значне зменшення споживаної потужності та площі як ЕП, так і ЗП.

Малюнок 4. Структура взаємодії ОЗП з кеш-пам’яттю МП системи

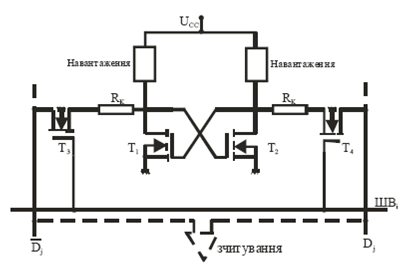

Область застосування статичних ОЗП в системах обробки інформації визначається їх високою швидкодією. Зокрема, вони широко використовуються в кеш-пам’яті, яка при любій ємності завжди має високу швидкодію. Статичну ОЗП (SRAM), як правило, мають структуру 2DM, а частина їх для кеш-пам’яті будується на структурі 2D. Запам’ятовуючим елементом статичних ОЗП є тригер, який має спеціальну установку та скид. Тому статичні ОЗП називають ще тригерними. Нами були розроблені і поставлені на серійне виробництво статичні ОЗП серій К537 РУ6 К-МОН технології і К132 РУ5,8,9 n-МОН технології. ЗЕ на n-МОН транзисторах представляє собою RS-тригер на транзисторах Т1 і Т2 (мал.5) з ключами вибірки Т3 і Т4. При звертанні до даного ЗЕ появляється високий потенціал на шині вибірки ШВі (через і,j позначені номери рядка і стовпця нагромаджувача, на перетині яких розміщений елемент пам’яті ЗЕіj). Цей потенціал відкриває ключі вибірки Т3 і Т4 по всьому рядку, а виходи тригерів рядка з’єднуються із стовбичними (розрядними) шинами запису-зчитування. Одна із цих шин зв’язана з прямим виходом тригера Dj. А друга з інверсним виходом Dj. Через розрядні шини зчитується стан тригера з використанням диференціального підсилювача зчитування. Через них можна записати дані в тригер, подаючи потенціал лог.0 на ту чи другу шину.

Малюнок 5. Схема тригерного ЗЕ на п-МОН транзисторах а) і варіанти навантаження б)

Запам’ятовуючі елементи статичних ОЗП, які виконані по К-МОН технології значно зменшують споживану потужність (як мінімум на порядок) і збільшують швидкодію за рахунок зменшення ємнісних струмів і відпадає необхідність в резисторах Rk та в високочутливих підсилювачів зчитування. Схема такого ЗЕ подана на мал. 6.

Малюнок 6. Схема статичних ОЗП на К-МОН транзисторах а) та схема буферного каскаду на три стани б)

Технологічною особливістю схеми а) є те, що тут використана багатозарядна імплантація для ретроградного формування охоронних областей та n-кишені і юстування порогових напруг UT n- і р-канальних транзисторів. Це дає можливість забезпечити перехідну характеристику інверторів з високою крутістю для збільшення швидкодії ЗП і їх високої завадозахищеності. Низький рівень сигналу CS і високий рівень сигналу W/R, що означають дозвіл виконання операції зчитування, створюють на виході елемента АБО-НЕ високий рівень лог.1, що відкриває транзистори Т3 і Т4 і, тим самим, забезпечує роботу інвертора на транзисторах Т1 і Т2, через який дані передаються на вихід DO. При інших комбінаціях сигналів CS і W/R вихід елемента АБО-НЕ має низький лог.0, при якому транзистори Т3 і Т4 є закритими і вихід DO вже знаходиться у відключеному стані. Схема передбачає також інверсний вихід DO.

В протилежність SRAM в динамічних ЗП (DRAM) дані зберігаються у вигляді зарядів ємностей МОН структур і основою ЗЕ таких схем є конденсатор певної ємності. Такий ЗЕ значно простіший тригерного (що вміщує 4-8 транзисторів) і дозволяє розмістити на кристалі в 4-5 разів більше елементів та забезпечує високу ємність ЗП. Але конденсатор, як втратний елемент, втрачає з часом свій заряд, тому для зберігання даних необхідна їх періодична регенерація (через декілька мс) спеціальними контролерами регенерації. Для збереження високої степені інтеграції ЗП типу DRAM використовують однотранзисторні ЕП, розміри яких настільки малі, що на них стали впливати навіть α-частинки, що випромінюються елементами корпусів ВІС. Тому забезпечення високої радіаційної стійкості динамічних ОЗП є актуальною і важливою задачею. Електрична схема, структура ЗЕ і схема його включення в нагромаджувач подані на мал. 7. Ключовий МОН транзистор відключає ЗЕ у вигляді конденсатора Сз від лінії запису-зчитування або підключає його до неї, тобто відіграє роль комутатора. Стік МОН транзистора не має зовнішнього виходу і утворює одну із обкладок конденсатора, а другою обкладкою конденсатора є сама кремнієва підкладка. Діелектриком такого конденсатора є підзатворний оксид, властивості якого і визначають електричні характеристики динамічного елемента пам’яті Сз.

Малюнок 7. Електрична схема ЗЕ ДОЗП структура та схема його включення

В режимі зберігання напруга на шині рядка Х близька до нуля і ключовий транзистор є закритим і тим самим динамічний конденсатор Сз є відключеним від шини запису- зчитування Y. На конденсаторі зберігається, встановлена при записі, напруга U1 або U0. У випадку зберігання лог. 1 конденсатор С3 буде поступово розряджатись внаслідок існування струмів втрат (як зворотних струмів p-n-переходів) на Si-підкладку. Якщо зберігається лог.0, а напруга на шині Y додатна, то конденсатор Сз буде поступово підзаряджатись передпороговим струмом транзистора. Тому необхідне періодичне відновлення вихідної напруги U1 або U0 на конденсаторі. Цей процес називають регенерацією. Вона здійснюється шляхом зчитування інформації з ЕП, перетворення її в напругу U1, U0 з допомогою підсилювача-регенератора і запис цієї напруги в ЕП. Регенерація проводиться одночасно для всіх елементів одного рядка протягом 1-5 мс[9,10]. Таким чином, важливим параметром динамічних елементів пам’яті є:

1) високі значення напруги пробою конденсатора при малому значенні струмів втрат;

2) малі ТКЕ і tgδ;

3) високе значення діелектричної сталої, бо остання визначає площу нагромаджувача;

4) високу радіаційну стійкість до α-опромінювання. Ясно, що таким вимогам не відповідають ємності, сформовані на основі SiO2, а тільки тонкоплівкові конденсатори на основі легованих РЗМ і вуглецем плівок β-тантала.

У режимі запису на шині Y вибраного стовпця встановлюється напруга U1 або U0, а потім подається позитивний імпульс на шину вибірки рядка Х. При цьому транзистор відкривається і на конденсаторі встановлюється та ж напруга, що на шині Y. В решти запам’ятовуючих елементів вибраного рядка в цей час, як правило, іде регенерація.

Процес зчитування інформації із ЗЕ пояснює мал. 7в, де показаний фрагмент ДОЗП, де ЗЕ представлений у вигляді транзисторного ключа та динамічної ємності Сз, підсилювача запису-зчитування, та умовних ключів К1 і К0, що відповідають за запис 1 чи 0. До лінії запису-зчитування підключені ЗЕ в кількості рядків, що є в нагромаджквальній матриці. Особливе значення має ємність лінії Сd , яка може перевищувати Сз запам’ятовуючого елемента. Перед зчитуванням проводиться перезаряд ЛЗЗ. При цьому використовують 2 варіанти ЗП з перезарядом ЛЗЗ:

1) до рівня напруги живлення.Ucc;

2) до рівня половини напруги живлення 1/2Ucc.

Особливістю динамічних ЗП для підвищення їх швидкодії, як відзначалось раніше, є мультиплексування шини адресу. Адрес відповідно ділиться на два півадреса, один із яких представляє собою адрес рядка, а другий – адрес стовпця нагромаджувача ЗЕ. Півадреса подаються на одні і ті ж виводи корпуса ВІС почергово. Подача адреса рядка супроводжується відповідним стробом RAS, а друга стовпця – стробом CAS. Причиною мультиплексування адресів є зменшення числа виводів корпуса і зменшення площі структури ЗП та збільшення швидкодії. Так, наприклад, ЗП з організацією 16Мх1 має 24 – розрядний адрес, а мультиплексування дозволяє скоротити число ліній на 12. На мал. 8 показана часова діаграма та зовнішня організація динамічних ОЗП з мультиплексуванням. Таким чином, правильне поєднання у виборі архітектури, організації, структури і субмікронної технології формування топології запам’ятовуючих елементів дозволяє зменшити площу, споживану потужність, підвищити швидкодію та радіаційну стійкість ВІС пам’яті адресного типу, понизити час їх вибірки до рівня 10-30 нс, збільшити інтеграцію схем пам’яті до 1-64 М.

Малюнок 8. Часові діаграми динамічного ОЗП з мультиплексуванням шини адресу а) та його зовнішня організація б).

Похожие работы

... . (Абзац другий частини першої статті 16 із змінами, внесеними згідно із Законом N 2949-III від 10.01.2002) РОЗДІЛ 2 МЕТОДИЧНЕ ЗАБЕЗПЕЧЕННЯ НАДАННЯ ПЛАТНИХ ПОСЛУГ ОЗДОРОВЧОГО ХАРАКТЕРУ 2.1 Мета та завдання оздоровчих центрів Сучаснi оздоровчi центри повиннi бути високоорганiзованими саморозвиваючими системами, здатними ефективно розвиватись i в повнiй мiрi враховувати сукупнiсть ...

... і інвестиції, зростаючий попит на туристичні послуги, високий рівень рентабельності і мінімальний термін окупності витрат. РОЗДІЛ 3 ОРГАНІЗАЦІЯ ТА ТЕХНОЛОГІЯ ПРОЦЕСІВ ВИРОБНИЦТВА ТА РЕАЛІЗАЦІЇ ТУРИСТИЧНИХ ПОСЛУГ ТУРИСТИЧНИМИ ФІРМАМИ ТА ТУР-АГЕНСТВАМИ 3.1 Транспортне забезпечення Транспортні подорожі розглядаються як самостійний вид туризму. Транспортні подорожі - це подорожі органі ...

... -профілактичних закладів, які мають на меті не тільки зберегти дитині життя, а й забезпечити її нормальний гармонійний розвиток та потенціал якості життя на майбутнє. Загальні принципи обстеження і догляду за дитиною За висловом професора Г.А. Захар'їна, правильно зібрати та оцінити анамнез хворої дитини – це половина діагнозу. Це велике лікарське мистецтво, яке обумовлює адекватність надання ...

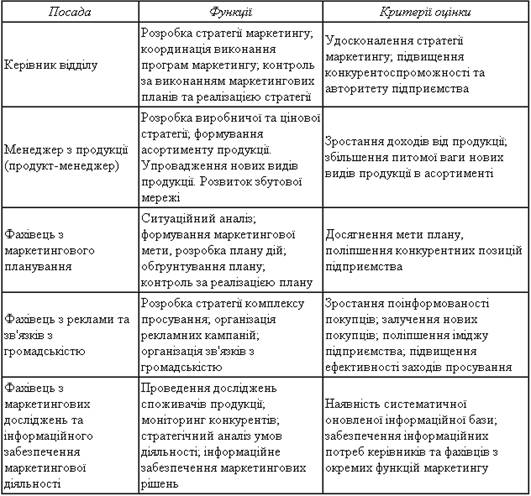

... відображення певної організації роботи на ринку. І формальним розподілом функціональних обов'язків між службами та службовцями проблема ефективної роботи не вичерпується. 2. Організаційні структури управління маркетингом на підприємстві Маркетингові організаційні структури, що "вмонтовуються" в систему управління фірмою, мають задовольняти такі вимоги: незначна кількість рівнів управління; ...

0 комментариев