Навигация

Спряження зовнішніх пристроїв з ПК за допомогою шин та ISA та PCI

Реферат

Спряження зовнішніх пристроїв з ПК за допомогою шин та ISA та PCI

1. Будова шини ISA

Шина ISA (Industrial Standart Arhitecture) є фактично стандартною шиною для персональних комп'ютерів типа IBM PC/AT і сумісних з ними. На основі ISA створено більш сучасні шини (EISA, PCI), які мають подібні принципи роботи.

При описі шини доцільно представити комп'ютер як материнську плату (motherboard) і зовнішні плати, які взаємодіють між собою і ресурсами материнської плати через шину ISA. Всі пристрої шини можна поділити на пасивні і активні (власники шини). У кожний момент часу у шини може бути тільки один власник (центральний процесор, контролер прямого доступу до пам’яті, контролер регенерації пам’яті або зовнішня плата).

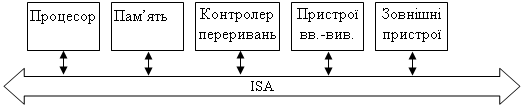

Рис.1. Основні пристрої, що під’єднуються до ISA

Центральний процесор (ЦП, 8, 16, 32 розрядні дані) - є основним задатчиком на шині (за замовчуванням). Контролер ПДП і контролер регенерації пам'яті можуть стати задатчиками на шині, тільки заздалегідь заборонивши роботу ЦП. Процес заборони роботи ЦП полягає у виробленні сигналу запиту на ПДП і прийому сигналу підтвердження ПДП.

Зовнішня плата (8 або 16 розрядні дані) - взаємодіє з рештою пристроїв через роз'єм на шині ISA, 16 розрядна плата може ставати задавачем (власником) на шині для доступу до пам'яті або пристроїв введення/виведення. Якщо ЦП є задатчиком на шині, то зовнішня плата може функціонувати тільки в режимі пам'яті або пристрою вводу/виводу.

До шини ISA під’єднується такий пристрій, як „Перестановник байтів даних”, який дозволяє обмінюватися даними 16-розрядним і 8-розрядним пристроям.

Особливість шини ISA в тому, що її тактовий сигнал (8 МГц) не співпадає з тактовим сигналом процесора, тому швидкість обміну по ній значно нижча за швидкість обміну процесор-пам’ять.

ISA – це 16-розрядна системна магістраль середньої швидкодії з розділеними шинами даних і адреси, обмін здійснюється 8 і 16 розрядними даними.

Адресний простір при зверненні до пам'яті

Максимальний адресний простір при зверненні до пам'яті, підтримуване шиною ISA, 16 Мб (24 лінії адреси), але не всі слоти підтримують повністю цей адресний простір. Коли задатчик на шині здійснює доступ до пам'яті на материнській платі або до пам'яті, встановленої в слот, він повинен дозволяти сигнали -MEMR або -MEMW; апаратно на материнській платі додатково дозволяються сигнали -SMEMR і -SMEMW, якщо необхідна адреса знаходиться в межах першого мегабайта адресного простору. До 8-розрядних слотів підведені тільки лінії -SMEMR і -SMEMR, SD<7...0> і SA<19...0>.

Адресний простір для пристроїв вводу/виводу

Максимально адресний простір для пристроїв введення/висновку, підтримуване шиною ISA складає 64 Кб (16 адресних ліній). Всі слоти підтримують 16 адресних ліній. Перші 256 адрес зарезервовані для пристроїв, розташованих, як правило, на материнській платі - регістри контролера ПДП, контролера переривань, годинника реального часу, таймера-лічильника і інших пристроїв, потрібних для сумісності різних комп'ютерів.

Не дивлячись на те, що для вибору адреси ПВВ (пристрою вводу/ виводу) доступні всі 16 сигналів адреси, традиційно для адрес ПВВ в комп'ютерах серії IBM PC/XT/AT використовувалися тільки перші 10 розрядів адреси. Тому для зовнішньої плати слід використовувати "вікна" в існуючому зараз розподілі адрес стандартних ПВВ для комп'ютерів IBM PC/AT.

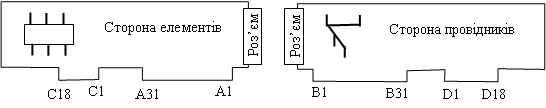

Апаратно шина має 2 роз’єми: 62-контактний і 36 контактний.

На материнській платі звичайно розміщується від 2 до 8 роз’ємів ISA.

Рис.2. Конструктивне виконання плат, що вставляються в роз’єм ISA

Загальне число встановлюваних в роз'єми шини плат обмежується як здатністю навантаження шини, так і конструктивним виконанням материнської плати. Як правило, допускається встановлювати не більш 8 (п'ять 16-розрядних і три 8-розрядних) зовнішніх плат на шину. Таке обмеження викликане також і відносно невеликою кількістю вільних ліній запитів на ПДП і запитів на переривання, що є на шині.

Зовнішня плата може функціонувати в 5 різних режимах:

1) задатчика шини;

2) пам'яті і пристроїв введення/виведення прямого доступу;

3) пам'яті і пристроїв введення/виведення;

4) регенерації пам'яті;

5) скидання.

Плата може підтримувати будь-яку комбінацію з перших чотирьох режимів; сигналу скидання повинна підкорятися вся плата одночасно.

Структура переривань

Лінії запиту на переривання безпосередньо заведені на контролери переривань типа Intel 8259A. Контролер переривань реагуватиме на запит по такій лінії у випадку, якщо сигнал на ній перейде з низького рівня у високий. Шина ISA не має ліній, підтверджуючих прийом запиту на переривання, що тому зовнішній пристрій повинен сам визначати підтвердження прийому свого запиту по реакції ЦП.

Для кращого розуміння функціонування шини доцільно розбити всі сигнали на 7 груп: АДРЕСИ, ДАНІ, СІНХРОСИГНАЛИ, КОМАНДНІ СИГНАЛИ, СИГНАЛИ РЕЖИМУ ПДП, ЦЕНТРАЛЬНІ СИГНАЛИ УПРАВЛІННЯ, СИГНАЛИ ПЕРЕРИВАННЯ, ЖИВЛЕННЯ. Інформація про спрямованість сигналів (вхід, вихід або двонаправлений) приводиться щодо задатчика на шині. Основні сигнали ISA наступні:

SA19... SA0 – фіксовані сигнали адреси, дійсні протягом всього циклу обміну. Сигнали SA19...0 дозволяють здійснювати доступ до пам'яті тільки в молодшому мегабайті адресного простору (й для ПВВ). Група сигналів адреси включає адреси, що виробляються поточним задатчиком на шині.

LA23... LA17 – нефіксовані адресні сигнали, дійсні на початку циклу обміну. використовуються для адресації пам’яті більше мегабайта.

BALE (Bus Address Latch Enable - дозвіл фіксації адреси) – сигнал стробування адресних сигналів.

Сигнал AEN (Address Enable - Дозвіл адреси) дозволяється тоді, коли контролер ПДП стає задатчиком на шині і повідомляє всі ресурси на шині про те, що на шині виконуються цикли ПДП. Цей сигнал забороняється, якщо задатчиком на шині є центральний процесор або контролер регенерації.

ОСОБЛИВОСТІ ДЛЯ ЗОВНІШНЬОЇ ПЛАТНІ

Якщо зовнішня платня, виконуючи процедуру захоплення шини, виробляє сигнал -MASTER, сигнал AEN забороняється контролером ПДП для того, щоб дозволити зовнішній платні доступ до пристроїв введення/висновку.

Для роботи з ПВВ використовують сигнали SA9...0.

SD<7...0> і SD<15...8>

Лінії SD<7...0> і SD<15...8>, як правило, ще називають шиною даних, причому по лінії SD15 передається старший значущий біт, а по лінії SD0 - молодший значущий біт. Лінії SD<7...0> - молодша половина шини даних, SD<15...0> - старша половина шини даних. Все 8-ми розрядні ресурси можуть обмінюватися даними тільки по молодшій половині шини даних. Підтримка обміну даними між 16-ти розрядним задатчиком на шині і 8-ми розрядним ресурсом здійснюється перестановщиком байтів на материнській платі.

Для роботи з ПВВ використовують сигнали SD7...0.

0 комментариев