Навигация

Вибір підходящої структури процесорного елемента та його опис

1.2 Вибір підходящої структури процесорного елемента та його опис

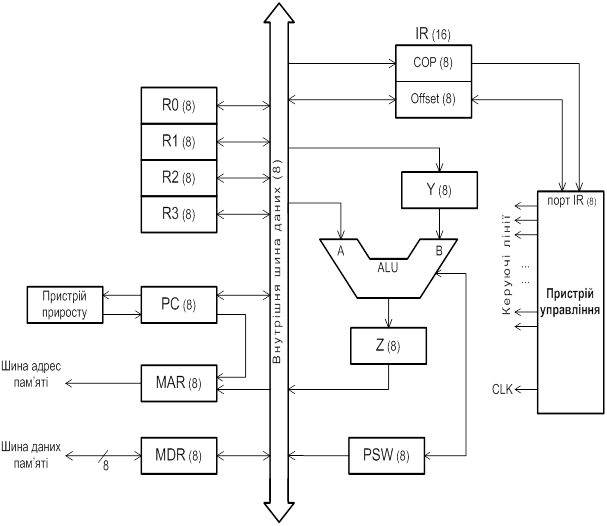

Структура створеного процесорного елемента зображена в додатку 1, розшифровка позначень, використаних у схемі, наведена в додатку 2.

Створюючи власну структуру процесорного елемента я вирішив, що його розрядність зручно зробити 8 біт, розрядність адрес теж я вирішив зробити 8 біт. Відповідно розрядність абсолютно всіх регістрів, а саме регістрів загального призначення, допоміжних регістрів АЛП, регістру даних пам’яті, регістру адрес пам’яті (MAR), лічильника команд (PC), регістру команд (IR) та регістру станів (PSW) — теж 8 біт.

Команди – однооперандні. Розмір коду операції – фіксований, і складає 8 біт. Структура команди має такий вигляд:

| 15 8 | 7 2 | 1 0 |

| Операнд | Код операції | Rm |

Операнд вибирається після дешифрації команди в тому випадку, якщо він потрібен. Для спрощення вважається, що операнд завжди присутній, просто в деяких командах він не використовується. В нашому випадку операндом є константа, з якою виконується порівняння. Rm (біти 0 та 1) — це номер регістра, значення якого порівнюється зі значенням константи. Нехай для нашої команди біти 2-7 мають таке значення: 000001b. Так як регістрів у нас 4, то можливі наступні варіанти коду команди:

00000100 SBR R0, B

00000101 SBR R1, B

00000110 SBR R2, B

00000111 SBR R3, B

Кількість регістрів загального призначення (R0..R3) вибрана такою малою через нестачу портів введення/виведення в пристрої управління.

До структури процесора також ввійшов пристрій приросту. Його задача — збільшення значення 8-розрядного регістру PC на одиницю за один такт, при цьому не займаючи шину даних.

Безпосередньо до шини даних під’єднані всі структурні елементи процесора, крім пристрою управління та пристрою приросту. Останній може отримувати дані лише через регістр IR (через старший або молодший байт). Виведення даних з пристрою управління на шину можливе лише через IRoff. Під’єднати шину даних безпосередньо пристрою управління не вдалося через нестачу портів введення/виведення в пристрої управління.

Для економії часу на пересилку адреси наступної команди з регістру PC в регістр MAR я вирішив з’єднати їх між собою безпосередньо. Завдяки цьому при вибірці кожної команди економиться один такт процесора. Крім того, пересилку PC à MAR для отримання наступної команди можна здійснювати під час виконання поточної команди, адже така пересилка не використовує шину даних. Тоді можна економити ще один такт при вибірці кожної команди.

На структурній схемі знехтувано лініями керування та лініями синхронізації, по яким пристрій управління посилає сигнали до всіх елементів процесора.

На рис 2 (додаток 1) показана розроблена архітектура процесора. В ній арифметико-логічний пристрій (АЛП) і всі регістри з'єднані однією загальною шиною. Це внутрішня шина процесора, яку не слід плутати з зовнішньою шиною, що з'єднує процесор з основною пам'яттю і пристроями введення\виведення.

Лінії даних і адреси зовнішньої шини пам'яті з'єднані з внутрішньою шиною процесора через регістр даних пам'яті, MDR, і регістр адреси пам'яті, MAR. Регістр MDR має два входи і два виходи. Дані можуть завантажуватися в нього або з зовнішньої шини пам'яті, або з внутрішньої шини процесора. Дані, що зберігаються в MDR також можуть бути поміщені на будь-яку з цих шин. Вхід регістра MAR з'єднаний із внутрішньою шиною і регістром PC, а його вихід — із зовнішньою. Керуючі лінії шини пам'яті з'єднані з дешифратором команди і керуючим логічним блоком.

Всі операції всередині процесора виконуються протягом періодів часу, що обумовлені тактовим сигналом процесора, або сигналом синхронізації, що надходить від пристрою управління, в якості якого в нашому випадку вступає мікроконтроллер. Сигнали, що керують конкретними операціями пересилання, активізуються на початку такту.

1.3 Реалізація пристрою управління

Пристрій управління реалізований у вигляді мікроконтроллера. Мікроконтроллер можна взяти будь-який, єдина вимога до нього — наявність п’яти потрів введення/виведення. Нехай було взято мікроконтроллер сімейства MCS-51.

4 порти введення/виведення під’єднані до управляючих ліній всіх елементів процесора. Інший 5-тий порт використовуються для введення чи виведення 8-бітних даних. Цей порт (P.2) може обмінюватись даними з молодшим та старшим байтом регістру IR. Призначення портів зображено на рис 1.

| R0in P1.0 | • | • | P0.0 IRcopin | |

| R0out P1.1 | • | • | P0.1 IRcopout_mc | |

| R1in P1.2 | • | • | P0.2 Yin | |

| R1out P1.3 | • | • | P0.3 Yout | |

| R2in P1.4 | • | • | P0.4 Zin | |

| R2out P1.5 | • | • | P0.5 Zout | |

| R3in P1.6 | • | • | P0.6 CLK | |

| R3out P1.7 | • | • | P0.7 PCinc | |

| PCin P3.0 | • | • | P2.0 IR 0 | |

| PCout P3.1 | • | • | P2.1 IR 1 | |

| PC_to_MAR P3.2 | • | • | P2.2 IR 2 | |

| MFC P3.3 | • | • | P2.3 IR 3 | |

| MARin P3.4 | • | • | P2.4 IR 4 | |

| MRead P3.5 | • | • | P2.5 IR 5 | |

| MDRin P3.6 | • | • | P2.6 IR 6 | |

| MDRout P3.7 | • | • | P2.7 IR 7 | |

| • | P4.0 ALUe0 | |||

| • | P4.1 ALUe1 | |||

| • | P4.2 ALUe2 | |||

| • | P4.3 ALUe3 | |||

| • | P4.4 ALUm | |||

| • | P4.5 IRoffin | |||

| • | P4.6 IRoffout | |||

| • | P4.7 | |||

Рис 1. Призначення портів пристрою управління

Розшифровка позначень

Біти портів для отримання сигналів (введення)

MFC — лінія для отримання сигналу готовності пам’яті.

Біти портів для керування (виведення):

Xin — лінія дозволу на вхід даних в регістр X з шини.

Xout — лінія дозволу на видачу даних з регістру X на шину.

Xin_mc — лінія дозволу на вхід даних в регістр X з порта мікроконтроллера.

Xout_mc — лінія дозволу на видачу даних з регістру X на порт мікроконтроллера.

CLK — лінія для сигналів синхронізації

PCinc — лінія для активації пристрою приросту

MRead — лінія для сигналу читання з пам’яті

PC_to_MAR — лінія дозволу пересилки даних з регістра PC в регістр MAR.

ALUe0.. ALUe0 — лінії для видачі на АЛП коду операції

ALUm — лінія вибору режиму роботи АПЛ (арифметичний / логічний)

Порт для обміну даними (введення/виведення)

IR — порт може обмінюватись даними з молодшим байтом регістру IR та отримувати дані зі старшого байту регістру IR.

2. Розробка мікропрограми

2.1 Загальний алгоритм виконання процесором команди SBR Rm, B

Для виконання програми процесор вибирає команди з пам'яті по одній і виконує обумовлені ними дії. Команди вибираються з послідовних адрес пам'яті доти, доки не зустрінеться команда переходу або розгалуження. Для цього в лічильнику команд (PC) відслідковується адреса чергової команди, що підлягає виконанню. Після вибору цієї команди вміст регістра PC змінюється так, щоб він вказував на наступну команду в пам'яті в порядку розташування адрес. Команда розгалуження може завантажити в PC іншу адресу.

Загальний алгоритм роботи процесора можна зобразити наступним чином:

1. Вибірка машинної команди

2. Збільшення лічильника команд на довжину команди

3. Дешифрація команди

4. Вибірка операнду (якщо потрібно)

5. Виконання команди

Команда “SBR Rm, B” — установка бітів регістру Rm згідно з бітовою маскою B.

Алгоритм виконання цієї машинної команди можна зобразити так:

1. Виконати команду логічного „або” над значенням регістру Rm та бітовою маскою.

2. Результат логічної операції записати в регістр Rm.

3. Перейти до вибірки наступної команди

2.2 Спрощена мікропрограма та її пояснення

Спрощена мікропрограма виконання команди SBR R1, B:

(Примітка: кожен рядок відповідає одному такту процесора)

1. PC_to_MAR, MRead, WMFC

2. MDRout, IRcopin , PCinc

3. PC_to_MAR, MRead, WMFC

4. MDRout, IRoffin , PCinc, IRcopout_mc , дешифрація

5. IRoffout, Yin

6. R1out , Yout , OR, Zin

7. Z out , R1in , End.

Кроки 1 та 2 складають фазу вибірки команди, однакову для всіх команд, кроки 3 та 4 — вибірка операнда та дешифрація.

1. На кроці 1 відбувається пересилка вмісту регістра PC в регістр MAR та ініціюється операція читання з пам'яті. Після отримання від пам’яті сигналу готовності переходимо до 2-го кроку:

2. Пересилка отриманого байту з регістру MDR в регістр IRcop (це перший байт команди – код операції); інкремент адреси, що знаходиться в PC.

3. На 3-му кроці робляться такі ж дії, що і на першому, а саме запит на читання байту з пам’яті за адресою, що в PC.

4. Пересилка отриманого байту з регістру MDR в регістр IRoff (другий байт команди (для команди SBR це бітова маска)); інкремент адреси, що знаходиться в PC; пересилка коду операції з регістру IRcop в блок управління; дешифрація коду операції.

Після вибірки команди і її дешифрації відбувається власне виконання команди (в нашому випадку – SBR R1, B ) .

5. Пересилка бітової маски, що знаходиться в регістрі IRoff, до регістру Y для подальшого його використання в АЛП в якості операнду.

6. Видача на шину вмісту регістру R1, операція логічного „або” в АЛП, результат помістити в регістр Z.

7. Пересилка значення регістру Z до регістру R1.

Лістинг програми, розбитий по крокам, з коментарями наведений в додатку 3.

ВИСНОВОК

Завданням курсової роботи було Розробка структурної схеми процесорного елемента та мікропрограми керування для реалізації команди “SBR Rm, B”. Для його виконання було розглянуто декілька літературних джерел, архітектури різних процесорів та мікроЕОМ. Розроблена в результаті курсової роботи архітектура не претендує на звання кращої, чи оптимальної. Вона проектувалась з боку спрощення, кращої наглядності схеми, для кращого її розуміння. Деякими структурними блоками було знехтувано, про що вказувалось по ходу роботи. При розробці схеми основну увагу приділялось правильному виконанню вказаної в завданні команди.

Розроблена мікропрограма для керування виконанням команди “SBR Rm, B” написана на машинній мові з використанням команд мікроконтроллера сімейства MCS-51. Створена мікропрограма виконується за 7 тактів процесора, з них 4 такти — це вибірка команди (коду операції та операнду), а 3 інших — безпосереднє виконання команди. Це дуже проста команда, що не потребує запитів до пам’яті, тому на її виконання треба всього 3 такти.

В результаті виконання роботи я поглибив свої знання про будову, принципи роботи процесорів та мікропроцесорних систем різних архітектур.

СПИСОК ВИКОРИСТАНИХ ДЖЕРЕЛ

1. Будіщев М.С. Електротехніка, електроніка та мікропроцесорна техніка. – видавництво «Афіша», 2001.–421с.

2. А. Буняк. Електроніка та мікросхемотехніка. – СМП «Астон», 2001.

3. Н. Ершова, О. Ивашенков, С. Курсков, Микропроцессоры, Пособие к курсам "Микропроцессорные средства" и "Автоматизированные системы для научных исследований" — http://dfe3300.karelia.ru/koi/posob/pos.html

4. Система команд AVR-контроллеров — http://ntlib.chat.ru/avr/instr.htm

5. Документація на мікроконтроллери фірми Intel MCS-51/151/251. (каталог pdf файлів) — http://www.intel.com/design/mcs51/docs_mcs51.htm

ДОДАТКИ

Додаток 1

Рис 2. Структурна схема процесорного елемента

Додаток 2

Розшифровка позначень на схемі

Таблиця 1

| Символьне позначення | Опис |

| R0, R1, R2, R3 | Регістри загального призначення, використовуються програмістами для потреб програм. |

| Z | Регістр, призначені для тимчасового збереження результату виконання певної операції арифметико-логічним пристроєм. |

| Y | Регістр для тимчасового збереження операнду, який потрібно обробити в АЛП. |

| IR | (Instruction register) Регістр, в якому зберігається код машинної команди. |

| ALU | (Arithmetical-logical unit) Арифметико-логічний пристрій, АЛП |

| PC | (Program counter) Лічильник команд |

| MAR | (Memory address register) Регістр адрес пам’яті |

| MDR | (Memory data register) Регістр даних пам’яті |

| PSW | (Program status word) Регістр стану |

Додаток 3

Лістинг мікропрограми

consts.inc

R0_in EQU p1.0

R0_out EQU p1.1

R1_in EQU p1.2

R1_out EQU p1.3

R2_in EQU p1.4

R2_out EQU p1.5

R3_in EQU p1.6

R3_out EQU p1.7

PC_in EQU p3.0

PC_out EQU p3.1

PC_to_MAR EQU p3.2

MFC EQU p3.3

MAR_in EQU p3.4

MRead EQU p3.5

MDR_in EQU p3.6

MDR_out EQU p3.7

IRcop_in EQU p0.0

IRcop_out_mc EQU p0.1

Y_in EQU p0.2

Y_out EQU p0.3

Z_in EQU p0.4

Z_out EQU p0.5

CLK EQU p0.6

PC_inc EQU p0.7

IR EQU p2

ALUe0 EQU p4.0

ALUe1 EQU p4.1

ALUe2 EQU p4.2

ALUe3 EQU p4.3

ALUm EQU p4.4

IRoff_in EQU p4.5

IRoff_out EQU p4.6

prog.asm

INCLUDE 80512.mc

INCLUDE consts.inc

Start:

fetch:

; ВИБІРКА КОМАНДИ

;...

; вибірка команди

;...

deshifr:

; ДЕШИФРАЦІЯ КОДУ КОМАНДИ

; Розпізнавання команди і перехід на відповідний код її виконання

MOV A, IR

ANL A, 11111100b ; залишаємо в А лише код операції, без номера регістру

my_cmd:

CJNE A, 00000100b, other_cmd

JMP SBR_Rm_B

other_cmd:

; ...

; ...

; ...

unknown_code:

JMP fetch

; ----------------------------------------------------------

; ВИКОНАННЯ КОМАНДИ

SBR_Rm_B:

; IRoff_out , Yin

SETB IRoff_out ; Пересилка бітової маски IRoff - > Y

SETB Y_in ;

SETB CLK ; Сигнал синхронізації

CLR CLK

CLR IRoff_out

CLR Y_in

; Rm_out , Yout , OR, Zin

; вибір потрібного регістру для пересилки в Y

MOV A, IR

ANL A, 00000011b ; залишаємо в А лише сам номер регістра

regR0out:

CJNE A, 00000000b, regR1out

SETB R0_out

JMP end_case1

regR1out:

CJNE A, 00000001b, regR2out

SETB R1_out

JMP end_case1

regR2out:

CJNE A, 00000010b, regR3out

SETB R2_out

JMP end_case1

regR3out:

SETB R3_out

end_case1:

SETB R1_out

SETB Y_out

SETB ALUe0 ; Код операції OR - 0001b

CLR ALUe1 ;

CLR ALUe2 ;

CLR ALUe3 ;

SETB Z_in ; результат - > Z

SETB CLK ; Сигнал синхронізації

CLR CLK

CLR R0_out ; закриваємо всі регістри

CLR R1_out ;

CLR R2_out ;

CLR R3_out ;

CLR Y_out

CLR ALUe0

CLR Z_in

; Z out , Rm_in , End

SETB Z_out ; пересилка результату в регістр R1

; вибір потрібного регістру для пересилки: Z - > Rm

regR0in:

CJNE A, 00000000b, regR1in ; в А - лише номер потрібного регістра

SETB R0_in

JMP end_case2

regR1in:

CJNE A, 00000001b, regR2in

SETB R1_in

JMP end_case2

regR2in:

CJNE A, 00000010b, regR3in

SETB R2_in

JMP end_case2

regR3in:

SETB R3_in

end_case2:

SETB CLK ; Сигнал синхронізації

CLR CLK

CLR Z_out

CLR R0_in ; закриваємо всі регістри

CLR R1_in ;

CLR R2_in ;

CLR R3_in ;

JMP fetch ; вибираєм наступну команду

0 комментариев