Навигация

ОБЩЕЕ ОПИСАНИЕ ПРИНЦИПА РАБОТЫ ПРОЦЕССОРА

2 ОБЩЕЕ ОПИСАНИЕ ПРИНЦИПА РАБОТЫ ПРОЦЕССОРА

Данный процессор с одномагистральной структурой выполняет указанный в задании набор команд.

К недостаткам такой схемы можно отнести низкую по сравнению с многошинными процессорами производительность, так как и для адресации и для передачи данных используется единственная шина. Но в данном случае адресация производится по содержимому программного счетчика, и по шине будет производиться только передача данных. Поэтому производительность такой системы будет не ниже, чем у многошинной.

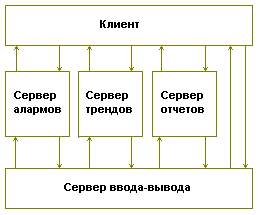

На рис. 1 показана структурная схема процессора с одной магистралью.

Следует привести некоторые пояснения к этой схеме. Блок «Memory» содержит последовательность команд, которые принадлежат набору команд, приведенному в предыдущем разделе. Выполнение каких либо других команд не данном процессоре будет невозможно. Выборка команд из памяти производится следующим образом: адрес команды, содержащийся в программном счетчике, записывается в регистр адреса, а затем выдается на адресные входы блока памяти, что сопровождается выдачей управляющим устройством сигнала чтения из памяти. Данные из памяти считываются буферный регистр. После того, как выбранная из памяти команда попадает в буферный регистр, она выдается на внутрипроцессорную шину, откуда она записывается в регистр команд (IR). На этом выборка команды заканчивается. Эту последовательность действий принято называть фазой извлечения команды (Fetch).

Итак, после окончания фазы извлечения команды начинается фаза интерпретации команды. В зависимости от команды эта фаза может представлять собой, например, извлечение из памяти константы, необходимой для выполнения команды, сдвиг аккумулятора и т. д. В конце этой фазы процессор готов к выполнению команды. На этом начинается фаза выполнения.

Алгоритм выполнения команды в общем случае состоит из таких фаз:

1. Выборка команды

2. Интерпретация команды

3. Формирование адреса из команды

4. Выполнение команды

3 ВРЕМЕННЫЕ ДИАГРАММЫ, ОПИСЫВАЮЩИЕ ВЫПОЛНЕНИЕ МИКРООПЕРАЦИЙ ДЛЯ КАЖДОЙ КОМАНДЫ

Разработаем формат команды, способный закодировать операции:

| Код операции | Номер РОН | Не используются | |||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

Пронумеруем операции процессора:

| Код операции | Команды | |

| 0 | 0 | Jmp # |

| 0 | 1 | Mov A,# |

| 1 | 0 | Mov Rn,# |

| 1 | 1 | Rl A |

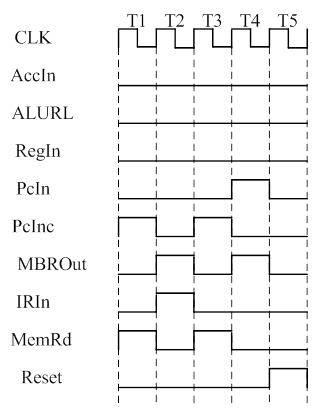

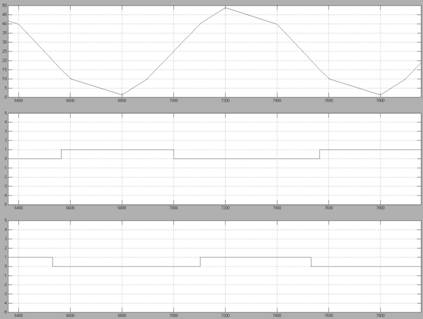

Временная диаграмма микроопераций выполнения команды JMP #d:

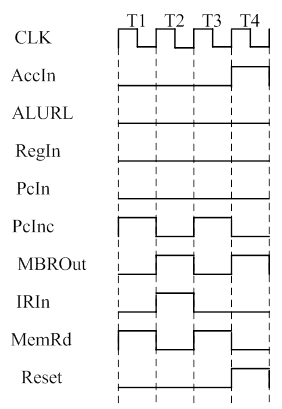

Временная диаграмма микроопераций выполнения команды MOV A, #d:

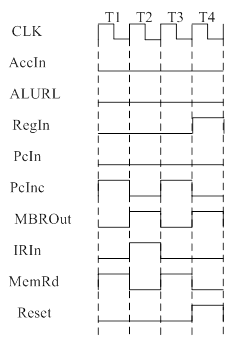

Временная диаграмма микроопераций выполнения команды MOV Rn, #d:

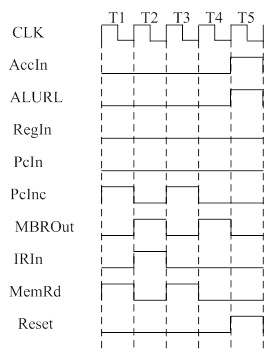

Временная диаграмма микроопераций выполнения команды RL A:

4 СОДЕРЖАТЕЛЬНЫЙ АЛГОРИТМ МИКРОПРОГРАММЫ

Опишем основные алгоритмы выполнения команд в процессоре по тактам с краткими пояснениями к каждой из них:

Переход в заданную часть кода (JMP #d)

1 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

2 MBROut, IRIn (загрузка из MBR, загрузка следующей команды)

3 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

4 MBROut, PCIn (загрузка из MBR)

5 Reset (сброс)

Загрузка константы в аккумулятор (MOV A, #d)

1 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

2 MBROut, IRIn (загрузка из MBR, загрузка следующей команды)

3 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

4 MBROut, AccIn, Reset (загрузка из MBR, загрузка в аккумулятор, сброс)

Загрузка константы в РОН (MOV Rn, #d)

1 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

2 MBROut, IRIn (загрузка из MBR, загрузка следующей команды)

3 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

4 MBROut, RegIn, Reset (загрузка из MBR, загрузка в РОН, сброс)

Сдвиг аккумулятора влево циклический (RL A)

1 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

2 MBROut, IRIn (загрузка из MBR, загрузка следующей команды)

3 MemRd, PCInc (чтение из памяти, инкремент программного счетчика)

4 MBROut (загрузка из MBR)

5 ALUOP, AccIn, Reset (выполнение операции, загрузка результата в аккумулятор, сброс)

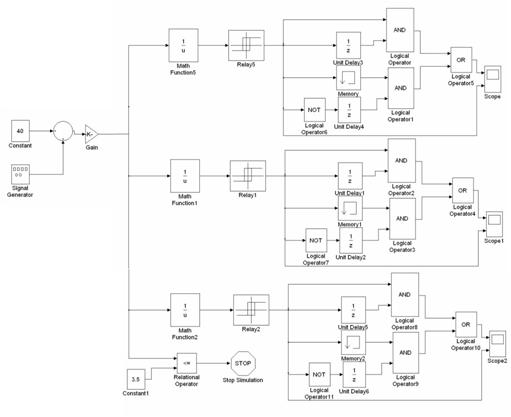

5 СИНТЕЗ УПРАВЛЯЮЩЕГО АВТОМАТА НА ОСНОВЕ ЖЕСТКОЙ ЛОГИКИ

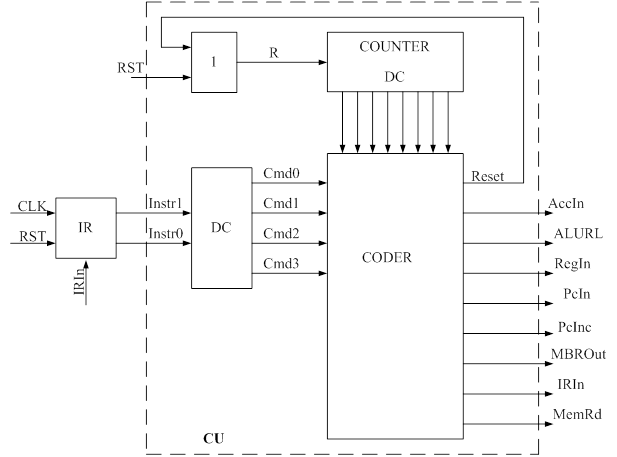

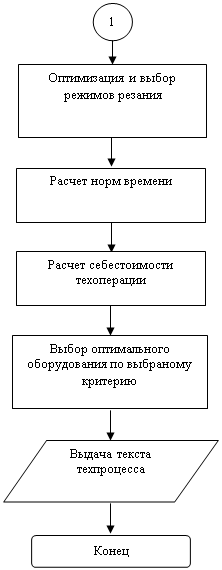

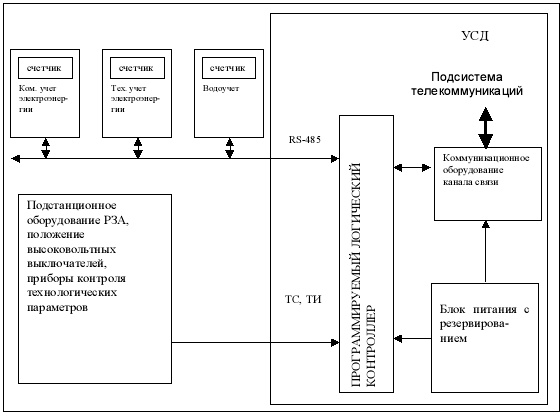

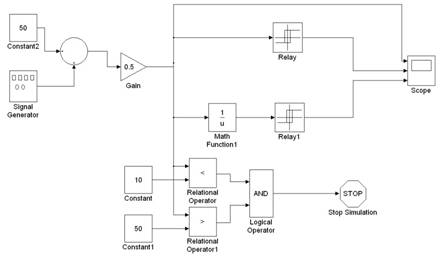

Структурная схема управляющего автомата на основе жесткой логики показана на рис. 2.

Рис. 2. Структурная схема управляющего автомата на основе жесткой логики

Ниже записаны выражения для выходных сигналов шифратора:

MemRd<='1' when c="00000001" or c="00000100" else '0' after 5ns;

PCInc<='1' when c="00000001" or c="00000100" else '0' after 5ns;

MBROut<='1' when c="00000010" or c="00001000" else '0' after 5ns;

IrIn<='1' when c="00000010" else '0' after 5ns;

PCIn<='1' when c="00001000" and i="0001" else '0' after 5ns;

AccIn<='1' when (c="00001000" and i="0010") or (c="00010000" and i="1000") else '0' after 5ns;

RegIn<='1' when c="00001000" and i="0100" else '0' after 5ns;

ALURL<='1' when c="00010000" and i="1000" else '0' after 5ns;

Reset<='1' when (c="00010000" and i="0001") or (c="00010000" and i="1000")

or (c="00001000" and i="0010")or (c="00001000" and i="0100") else '0' after 5ns;

Похожие работы

... недостаточно). Возможно включение комплекса в план учебного процесса, для обучения студентов. 2. Специальная часть разработка программного обеспечения для организации интерфейса программно-методического комплекса 2.1 Разработка технического задания на реализацию специальной части дипломного проекта Наименование программного изделия - "Интерфейс программно - методического комплекса для ...

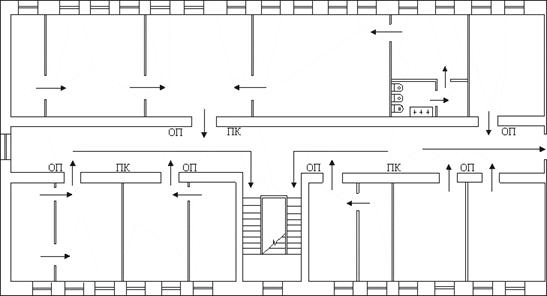

... ребрами) изображают конструктивные и потоковые функциональные структуры [14]. Принципы построения функциональных структур технических объектов рассматриваются в последующих главах курса "Основы проектирования им конструирования" не включенных в настоящее пособие. Для систем управления существуют характеристики, которые можно использовать в качестве критериев для оценки структур. Одна из них - ...

... К. Сатпаева» для просмотра и ввода информации системы оперативно-диспетчерского контроля и управления, создаваемые на Visual Basic. Специфика используемого в системе оперативно-диспетчерского контроля и управления РГП «Канал им. К. Сатпаева» ПО такая, что разработка ПО, как таковая, может производиться только при создании самой системы. Применяемое ПО является полуфабрикатом. Основная задача ...

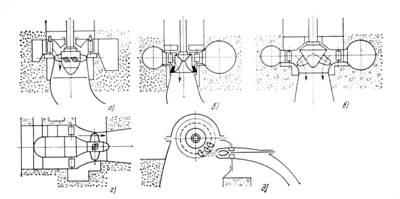

... ). Подпрограмма завершена, управление передается назад вызывавшему модулю. 6. Технико-экономическое обоснование 6.1 Пути снижения затрат за счет внедрения системы Внедрение автоматической системы управления маслонапорной установкой гидроэлектростанции решает следующие задачи - Полностью автоматическая система управления маслонапорной установкой не требует участия человека ...

0 комментариев