Навигация

Составляющие программы

1.7.2 Составляющие программы

Программа управления автоматизированным комплексом многоканальной связи состоит из трех частей: основная программа, подпрограмма перезаписи карты памяти части битов внутренних регистров CR1, CR2, TSR и PSR линейных интерфейсов, которая выполняется с приходом прерывания от любого линейного интерфейса и подпрограмма связи с внешней ПЭВМ через последовательный порт, которая выполняется, когда приходит прерывание от последовательного порта.

Система прерываний для микроконтроллера АТ89С51 организована следующим образом. При приходе прерывания от последовательного порта, выполняется специальная подпрограмма обработки этого прерывания. Как она работает. Вначале производится проверка, и если приходит прерывание от передатчика, то сбросить его и выйти. Если нет, то производится проверка полученного байта, если пришёл байт с установленным 9 битом то выполняется инициализация процедуры чтения данных из памяти, затем подсчёт контрольной суммы, передача блока данных на ЭВМ и завершение подпрограммы. Если пришел байт без установленного 9 бита, то если переданы все байты – передаётся контрольная сумма, а если нет – передаётся байт и подсчитывается контрольная сумма.

В начале основной программы происходит назначение векторов прерываний от линейных интерфейсов и последовательного порта. Далее идут два блока инициализации: области памяти ОЗУ данных с 40Н по 7FН и самих линейных интерфейсов. Команды инициализации последних CR2.RESET формируются в соответствии с таблицей адресов линейных интерфейсов и таблицей адресов внутренних регистров линейных интерфейсов.

| Регистр | Bit | ||||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| LI1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00Н |

| LI2 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 10H |

| LI3 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 20Н |

| LI4 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 30H |

| LI5 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 40Н |

| LI6 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 50H |

| LI7 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 60H |

| LI8 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 70H |

| LI9 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 80H |

| LI10 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 90H |

| LI11 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | A0H |

| LI12 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | В0Н |

| LI13 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | C0H |

| LI14 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | D0Н |

| LI15 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | E0H |

| LI16 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | F0H |

| Регистр | Bit | ||||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| CR1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 00H |

| CR2 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 02H |

| CR3 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 04H |

| CR4 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 0EH |

| ICR | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 06H |

| TSR | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 08H |

| PSR | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0AH |

| ESR | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 | 0CH |

Рис. 1.10. Адреса внутренних регистров линейных интерфейсов.

Затем производится запись в ОЗУ данных состояний части битов внутренних регистров линейных интерфейсов. Данные располагаются в заранее оговоренной техническим заданием области памяти 40Н – 7FН в заданном порядке. Распределение памяти ОЗУ данных процессора показано на рисунке 1.11. Нужные биты выбираются из внутренних регистров линейных интерфейсов, таблица которых приведены на рисунке 1.12. Например, для занесения бита AIS в 1‑й бит ячейки памяти 40Н, его нужно считать из 2‑го бита регистра PSR LI1. Порядок сохраняется для всей карты по возрастанию следующий: PSR, TSR, CR2, CR1.

| Линейный интерфейс | Адрес регистра в ОЗУ | Bit | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| L1 1 | 40 Н | DFMO | AIS | LOS | |||||

| 41 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 42 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 43 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 2 | 44 H | DFMO | AIS | LOS | |||||

| 45 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 46 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 47 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 3 | 48 Н | DFMO | AIS | LOS | |||||

| 49 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 4A Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 4B Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 4 | 4C Н | DFMO | AIS | LOS | |||||

| 4D Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 4E Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 4F Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 5 | 50 Н | DFMO | AIS | LOS | |||||

| 51 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 52 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 53 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 6 | 54 Н | DFMO | AIS | LOS | |||||

| 55 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 56 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 57 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 7 | 58 Н | DFMO | AIS | LOS | |||||

| 59 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 5A Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 5B Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 8 | 5C Н | DFMO | AIS | LOS | |||||

| 5D Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 5E Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 5F Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 9 | 60 Н | DFMO | AIS | LOS | |||||

| 61 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 62 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 63 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 10 | 64 Н | DFMO | AIS | LOS | |||||

| 65 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 66 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 67 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 11 | 68 Н | DFMO | AIS | LOS | |||||

| 69 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 6A Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 6B Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 12 | 6C Н | DFMO | AIS | LOS | |||||

| 6D Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 6E Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 6F Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 13 | 70 Н | DFMO | AIS | LOS | |||||

| 71 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 72 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 73 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 14 | 74 Н | DFMO | AIS | LOS | |||||

| 75 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 76 Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 77 Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 15 | 78 Н | DFMO | AIS | LOS | |||||

| 79 Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 7A Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 7B Н | ES4 | ES3 | ES2 | ES1 | |||||

| L1 16 | 7C Н | DFMO | AIS | LOS | |||||

| 7D Н | FL | TQRSS | ESOVR | ESUNF | TDFMO | TAIS | TLOS | ||

| 7E Н | ЕРАТ1 | EPAT0 | ETAOS | EQZMON | ERLOOP | ELLOOP | EALOOP | ||

| 7F Н | ES4 | ES3 | ES2 | ES1 | |||||

Рис. 1.11. Распределение памяти ОЗУ данных процессора.

Потом инициализируется последовательный порт Р3 на прием. Инициализируется таймер, выбор 1‑го таймера, перевод его в третий режим работы, загрузка константы скорости в таймер для 9600 Бод, разрешение работы таймера. Инициализация последовательного порта проходит следующим образом: порт устанавливается в режим 9‑бит с программируемой скоростью, устанавливается адрес для записи принятых значений, выбирается номера канала, идет разрешение приёма сообщений с взведённым 9‑м битом, разрешение работы приёмопередатчика, разрешение прерываний от приёмопередатчика, общее разрешение прерываний, сброс бита разрешения приёма. После этого выполняется основной цикл программы: ожидание прерывания либо от любого из линейных интерфейсов с переходом на подпрограмму перезаписи карты памяти части битов внутренних регистров линейных интерфейсов, либо от последовательного порта с переходом на подпрограмму связи с внешней ПЭВМ через последовательный порт.

Подпрограмма перезаписи карты памяти части битов внутренних регистров линейных интерфейсов состоит из четырех последовательных вызовов подпрограмм RDPSR, RDTSR, DRCR2 и RDCR1 с предварительным занесением в регистр R1 соответствующих адресов регистров, используя таблицу, приведенную на рисунке 1.10. Выполнение подпрограммы происходит в режиме маскирования прерываний. После перезаписи карты памяти снимаются все флаги прерываний линейных интерфейсов и происходит выход из подпрограммы.

Подпрограмма связи с внешней ПЭВМ через последовательный порт вызывается при появлении прерывания от последовательного порта. Она также с запрещения всех прерываний. Инициализируется прием и прослушивается порт на приход старт байта. В случае его получения происходит инициализация чтения данных из памяти. Считается контрольная сумма для передачи бита четности и происходит поблочная передача данных. Для передачи всех 64 байт требуется 64 сеанса связи. Такая организация работы выбрана не случайно. В разделе, где упоминалось об основах асинхронной последовательной связи, приводились причины, по которым данный способ взаимодействия внешней ПЭВМ с последовательным портом является оптимальным. При втором сеансе связи приема старт байта не происходит. Это говорит о продолжении уже начатой передачи данных. Смотрится, является ли этот байт признаком передачи последнего кусочка данных. В этом случае считается контрольная сумма и выполнение подпрограммы прекращается. Иначе мы продолжаем поблочно читать данные из памяти и передавать их внешней ПЭВМ через последовательный порт.

Похожие работы

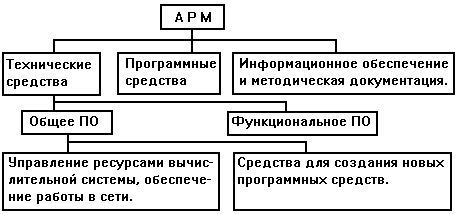

... также невысока и обычно составляет около 100 кбайт/с. НКМЛ могут использовать локальные интерфейсы SCSI. Лекция 3. Программное обеспечение ПЭВМ 3.1 Общая характеристика и состав программного обеспечения 3.1.1 Состав и назначение программного обеспечения Процесс взаимодействия человека с компьютером организуется устройством управления в соответствии с той программой, которую пользователь ...

... первичной или первичной вместе со вторичной или только вторичной И. Если это - итог обработки информации, решения задачи, то такая информация называется результативной, результирующей. В процессе решения задач возникает промежуточная информация, которая часто в автоматизированных системах играет самостоятельную роль, определения направления путей завершения решения задачи. Результатная информация ...

еоценить значение МП и микроЭВМ при создании автоматизированных средств измерений, предназначенных для управления, исследования, контроля и испытаний сложных объектов. Развитие науки и техники требует постоянного совершенствования средств измерительной техники, роль которой неуклонно возрастает. Основные понятия и определения Понятия и определения, используемые в измерительной технике, ...

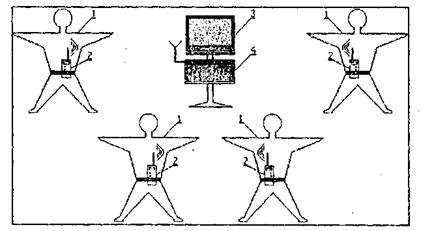

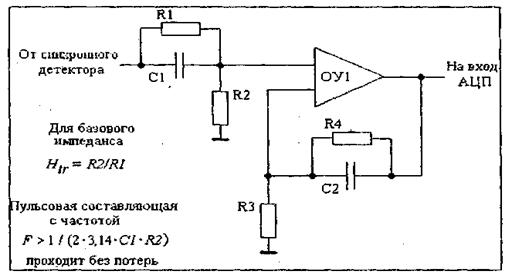

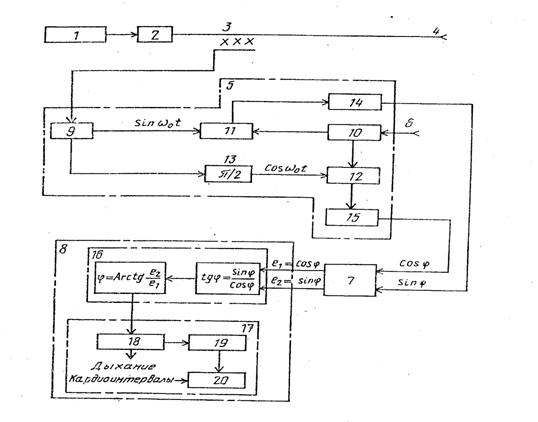

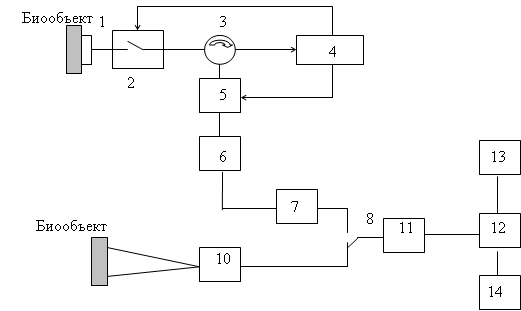

... питания, блока сопряжения с компьютером, компьютер, индикатор. Блок – схема радиоприемника представлена на рисунке.2.1. Рисунок 2.1 - Структурная схема дистанционного комплекса контроля функционального состояния 1 – приемник; 2 – дешифратора; 3 – детектора; 4 – усилителя; 5 – усилителя вертикального отклонения; 6 – электронно-лучевой трубки; 7 – задающего генератора ...

0 комментариев