Навигация

1. Розробка схеми пристрою

1.1 Опис схеми

У мікросхемах пам’яті динамічного типу функції ЕП виконує електричний конденсатор, утворений усередині МДН-структури. Інформація надходить у вигляді заряду: наявність заряду на конденсатор відповідає логічному ‘0’, відсутність – логічній ‘1’. Оскільки час збереження конденсатором заряду обмежений, передбачають періодичне відновлення (регенерацію) записаної інформації. У цьому полягає одна з відмінних рис динамічних ОЗП. Крім того, для них потрібна синхронізація, що забезпечує необхідну послідовність вмикань і вимикань функціональних вузлів.

В моєму курсовому проекті мені треба використовувати мікросхему К565РУ5Б. Модуль пам’яті DD1…DD8 побудований на мікросхемах К565РУ5Б шляхом з’єднання їх одноіменних виводів, крім інформаційних. Сигнали RAS i CAS формує контролер ОЗП CLM, сигнал MWTC із шини керування подається на вхід W/R.

З’єднання з шиною даних реалізується за допомогою шинного формувача DD9 (К580ВА86), котрий керується сигналом MRDC контролером ОЗП CLM.

Мультиплексор DD10…DD12 забезпечує послідовне за часом введення адресного коду рядків Ах (А6-А11) у модуль ОЗП. Адресні сигнали надходять на входи К1, К2 і К5, К6 мультиплексорних систем і комутуються на виходи під керуванням сигналу на вході А(Ау-Ах) за наявності на іншому керуючому вході В(RЕF) рівня ‘0’. Умови комутації адресних сигналів такі: при Ау/Ах = 0 до виходів підключаються канали К1, К5 і отже, на адресні входи ОЗП надходять адреси рядків Ах, при Ау/Ах = 1 до виходів підключаються канали К2,К6 і до ОЗП спрямовується код адреси стовпців Ау.

Сигнали керування (RЕF – ознака режиму регенерації і Ау/Ах – сигнал мультиплексування каналів) виробляє контролер.

У режимі регенерації RЕF = 1 і мультиплексор комутує на виходи при зміні Ау/Ах канали К3, К4 і К7, К8. Проте через те, що зазначені канали попарно з’єднані, то на результат комутації сигнал Ау/Ах не впливає: за будь-яких його значень на виходи мультиплексора надходять адреси регенерації АR, що виробляються лічильником контролера. Ці сигнали адресують тільки рядки, сигналів адреси стовпців у цьому режимі на адресних входах немає.

Контролер динамічного ОЗП має вузол формування сигналів керування модулем ОЗП та мультиплексором адреси і вузол формування 8-розрядного адресного коду регенерації АR0 – АR5.

У кінці циклу звертання до ОЗП контролер формує сигнал регенерації RЕF= 1. За відсутності звертання до ОЗП (МRDС = 1, МWТС = 1) або за наявності сигналу заборони ІNHI = 0 блок ОЗП працює тільки в режимі регенерації. З кожним тактом Ф2 контролер формує сигнали RAS, RЕF і код адреси чергового рядка і ініціює роботу модуля пам’яті за циклом регенерації. Процес регенерації припиняється при звертанні мікропроцесора до ОЗП, і контролер обробляє вимогу мікропроцесора. У кінці циклу звертання контролер переводить блок ОЗП у режим регенерації, продовжуючи цей процес з адреси, на якій він був перерваний. Тактові сигнали виробляє генератор тактових імпульсів DD16 (КР580ГФ24). В схемі використовується мікропроцесор DD15 (КР580ВМ80А).

1.2 Вибір елементів схеми

В якості ЦП використовується КР580ВМ80А

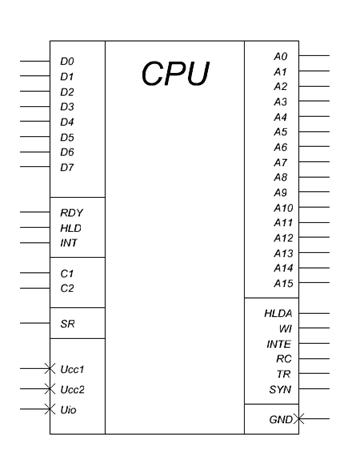

Умовне позначення мікросхеми наведено на рис. 1.2

Рисунок 1.1 – Умовне позначення КР580ВМ80А

Призначення виводів наступне:

A0-А15 - адресні шини мікросхеми;

GND- спільний;

Uio- напруга зміщення джерела - 5В;

C1, C2-вихід, тактові сигнали;

Ucc1-напруга живлення +5В;

Ucc2-напруга живлення +12В;

D0 – D7 – шини даних;

SR (установка) - переведення процесора у вихідний стан. Виконання програми починається з нульової адреси;

SYNC - сигнал синхронізації, що визначає початок кожного машинного циклу команди;

C1, C2 - входи двох послідовностей синхросигналів, що не перекриваються.

WAIT (чекання) - сигнал, який чекає процесор, коли зовнішній пристрій або пам'ять будуть готовий до обміну;

RDY (готовність) - вхідний сигнал, вказуючий, що зовнішній пристрій готовий до обміну. Разом з сигналом WAIT дозволяє синхронізувати обмін з пристроями низької швидкодії або організувати покроковий, командний режим роботи (при відладці) і останов за необхідною адресою;

WR - вихід сигналу низького активного рівня, вказуючого, що мікропроцесор видав дані на шину D7...D0. Використовується для управління записом інформації в пам'ять або в зовнішній пристрій;

DBIN - сигнал дозволу прийому інформації на шину даних D7...D0 з пам'яті або зовнішніх пристроїв;

INT - вхідний сигнал запиту переривання роботи процесора, що поступає від зовнішніх пристроїв;

INTE - вихідний сигнал дозволу переривання високого рівня, вказуючий, що процесор готовий до обміну (може прийняти запит переривання). Після переходу до обслуговування переривання на виході встановлюється сигнал низького рівня і запити переривання не сприймаються;

HLD - вхідний сигнал запиту на захват шин D7...D0, А15...А0 з боку зовнішніх пристроїв. Процесор переходить в стан "ЗАХВАТ", і системна шина може використовуватися зовнішніми пристроями;

HLDA - вихідний сигнал підтвердження захвату шин. Є ознакою допуску зовнішнього пристрою до шин даних і адреси системи.

Процесор містив 4500 транзисторів за технологією 6 мкм n-МДП (дані для i8080, але для КР580ВМ80А ймовірно мають бути аналогічними).Штатна тактова частота для процесора КР580ВМ80А — до 2,5 МГц (теоретично дозволяв працювати на вищій частоті). Кожна команда виконується за 1..5 машинних циклів, кожен з яких складається з 3..5 тактів. Таким чином середня продуктивність оцінюється на рівні 200..300 тис. оп/c на частоті 2 МГц.

Мікропроцесор мав роздільні 16-розрядну шину адреси і 8-розрядну шину даних. 16-розрядна шина адреси забезпечує пряму адресацію зовнішньої пам'яті об'ємом до 64 Кбайт і 256 пристроїв введення/виводу.

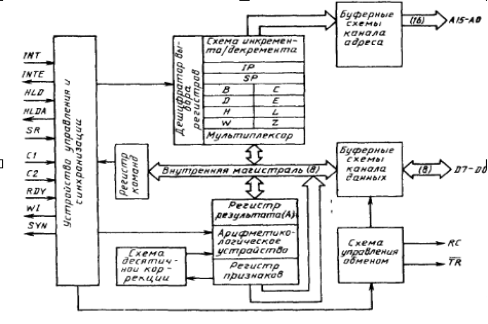

Для зберігання тих, що беруть участь в операціях даних передбачено 7-8-розрядних регістрів. Регістр А, званий акумулятором, призначений для обміну інформацією із зовнішніми пристроями, при виконанні арифметичних, логічних операцій він служить джерелом операнда, в нього поміщається результат виконаної операції. Шість інших регістрів, позначених B, C, D, E, H, L, утворюють так званий блок регістрів загального призначення (ЗП). Ці регістри можуть використовуватися як одиночні 8-розрядні регістри. У випадках, коли виникає необхідність зберігати 16-розрядні двійкові числа, вони об'єднуються в пари BC, DE, HL.

Покажчик стека служить для адресації особливого вигляду пам'яті, званого стеком в якому зберігаються адреси повернення до перерваних підпрограм.

Рисунок 1.2 - Структурна схема КР580ВМ80А

Лічильник команд (адреси) вказує адресу, де знаходитися в пам'яті черговий байт команди.

У 8-розрядному АЛП передбачена можливість виконання чотирьох арифметичних операцій, чотирьох видів логічних, а також чотирьох видів циклічного зсуву. При виконанні цих операцій одним з операндів служить вміст акумулятора і результат операції поміщається в акумулятор. Циклічне зрушення виконується лише над вмістом акумулятора. Передбачена можливість виконання арифметичних операцій над десятковими числами.

Регістр команд. У нього поступає перший байт команди що містить код операції.

Буфери даних і буфери адреси забезпечують зв'язок центрального процесора із зовнішніми шинами даних і адреси. Використання буферів з трьома станами дозволяє процесору відключатися від зовнішніх шин, надаючи їх в розпорядження зовнішніх пристроїв, а також дозволяє використовувати одну і ту ж шину як для прийому даних так і для передачі.

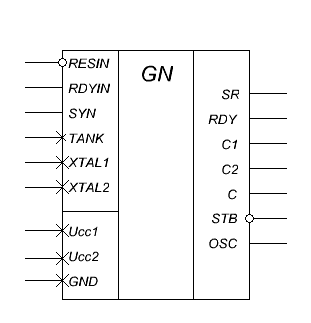

Мікросхема КР580ГФ24 (рисунок 1.3) – генератор тактових імпульсів (ГТІ) сигналів фаз С1, С2, призначений для синхронізації роботи МП КР580ВМ80А.

Рисунок 1.3 – Умовне позначення ГТІ

Генератор формує: дві фази С1, С2 з позитивними імпульсами, зсунутими в часі, амплітудою 12 В і частотою 0,5-3,0 МГц; тактові сигнали опорної частоти амплітудою напруги рівня ТТЛ; стробуючий сигнал стану STB тривалістю не менше (Топ/9-15 нс), де Топ – період тактових сигналів опорної частоти; тактові сигнали С, синхронні з фазою С2, амплітудою напруги рівня ТТЛ.

Генератор синхронізує сигнали RDYIN і RESIN з фазою С2.

ГТІ складається з генератора опорної частоти, лічильника-дільника на 9, формувача фаз С1, С2 і логічних схем. Для стабілізації тактових сигналів опорної частоти до входів ХТАL1, ХТАL2 генератора підключають резонатор, частоти якого повинна бути в 9 раз більше частоти вихідних сигналів С1, С2.

Призначення виводів ГТІ:

SR – установка в початковий стан МП і системи;

RЕSІN – установка 0;

RDYIN – сигнал "готовність";

RDY – сигнал "готовність"(вихід);

SYN – сигнал синхронізації;

С – тактовий сигнал, синхронізуючий з фазою С2;

SТВ – стробуючий сигнал стану;

GND - загальний;

UCC2 - напруга живлення +12 В;

С2 – тактові сигнали – фаза С2;

С1 - тактові сигнали – фаза С1;

OSC – тактові сигнали опорної частоти;

TANK – вивід для підключення коливального контура;

ХТАL1,ХТАL2 – виводи для підключення резонатора;

UCC1 – напруга джерела + 5 В.

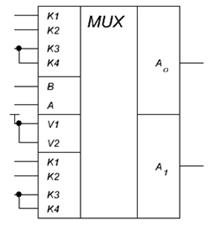

Мікросхема К155КП2 являє собою здвоєний селектор-мультиплексор 4-1 зі спільними входами вибірки даних і роздільними входами стробування.

Призначення виводів К155КП2:

A,B – вхід вибірки розряду;

K1,K2,K3,K4,K5,K6,K7,K8 – адресні входи;

A0,A1 - адресні виходи;

Рисунок 1.4 – Умовне позначення К155КП2

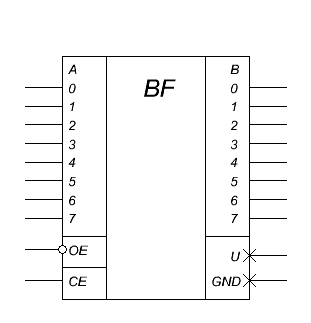

Мікросхема КР580ВА86 це двонаправлений 8-розрядний шинний формувач, призначений для обміну даними між мікропроцесором і системою шин. Мікросхема складається з восьми однакових функціональних блоків і схеми управління. За допомогою блоку управління виконується дозвіл передачі (управління 3-м станом виходу) і вибір напрямку передачі.

Призначення виводів КР580ВА86:

A0-A7 – інформаційна шина;

B0-B7 – інформаційна шина;

CE – вибір кристалу;

OE - вибір напрямку передачі;

U -напруга живлення +5В;

GND - загальний;

Рисунок 1.5 – Умовне позначення КР580ВА86

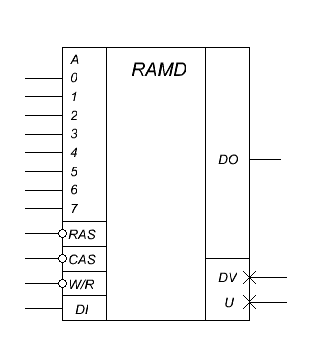

Мікросхема К565РУ5Б - елемент пам’яті організований в матрицю рядків і стовпців. DI i DO – інформаційні входи і виходи, W/R – вхід керування читанням/записом, А7-А0 – адресні входи, RAS – вхід вибірки рядка, CAS – вхід вибірки стовця.

Спочатку на адресні входи подаються молодші сім розрядів повної адреси, які запам’ятовуються в внутрішньому адресному регістрі по сигналу RAS , потім на ці лінії подаються старші сім розрядів адреси, які запам’ятовуються по сигналу CAS. Сигнал WE виконує функцію читання/запису.

Призначення виводів мікросхеми КР565РУ5:

А0-А11 - адресні входи;

CАS - строб адреси рядків;

RAS - строб адреси стовпців;

WR/RD - сигнал запису/зчитування;

D0,DІ - інформаційні входи;

Рисунок 1.6 - Умовне позначення КР565РУ6

Контролер динамічного ОЗП має вузол формування сигналів керування модулем ОЗП та мультиплексором адреси, і вузол формування 8-розрядного адресного коду регенерації Ar0 – Ar5

Рисунок 1.7 – Контролер динамічного ОЗП CLM

Контролер динамічного ОЗП має вузол DD1-DD5 формування сигналів керування модулем ОЗП та мультиплексором адреси і вузол DD6, DD7 формування 8-розрядного адресного коду регенерації Ar0 – Ar7. Вихідні сигнали генераторної мікросхеми КР580ГФ24 формують OSC з частотою 18МГц і Ф2 з періодом 0,5 мкс. Вихідними для контролера є також сигнали MWTC, MRDC, INH1, що надходять із шини керування.

Сигнали керування мультиплексором формують регістр DD1 і схему керування режимом звертання до модуля ОЗП на елементах DD2, DD3. У разі звертання до ОЗП на виході DD3.1 з'являється 1, що по попередньому фронту Ф2записуеться в DD2.1 і з’являється на виході цього тригера. Другий тригер DD2.2 зберігає свій стан "0" маючи на iнверсному виходi "1". Тому вихід DD3.4 переходить у стан "0" і забезпечує REF = 0, за якого мультиплексор комутує на адресні входи ОЗП адреси рядків Аx і стовпців Ау. Введення цих адрес у мікросхему здійснюють сигнали RAS і CAS, які формують регістр DD1 і додаткові логічні елементи DD4.1, DD5.1 так, щоб була виконана вимога зсуву в часі сигналу CAS відносно RAS. Одночасно із зазначеними сигналами в режимі звертання формуються сигнали СЕ = 1 і OE = О (при MRTC = 0), що забезпечують обмін модуля ОЗП із шиною через шинний формувач для запису в ОЗП (СЕ = 1, ОЕ = 1 і вихід вимкнений) і зчитування з ОЗП (СЕ = 1, ОЕ = 0) інформації. У кінці циклу звертання до ОЗП контролер формує сигнал регенерації REF = 1, що через мультиплексор комутує виходи лічильника DD6, DD7 на адресні входи ОЗП й у такий спосіб забезпечує регенерацію інформації в ЕП рядка кожної мікросхеми пам'яті. Після закінчення сигналу REF лічильник адреси регенерації переходить у наступний стан і формує на своїх виходах адресу чергового рядка.

0 комментариев