Навигация

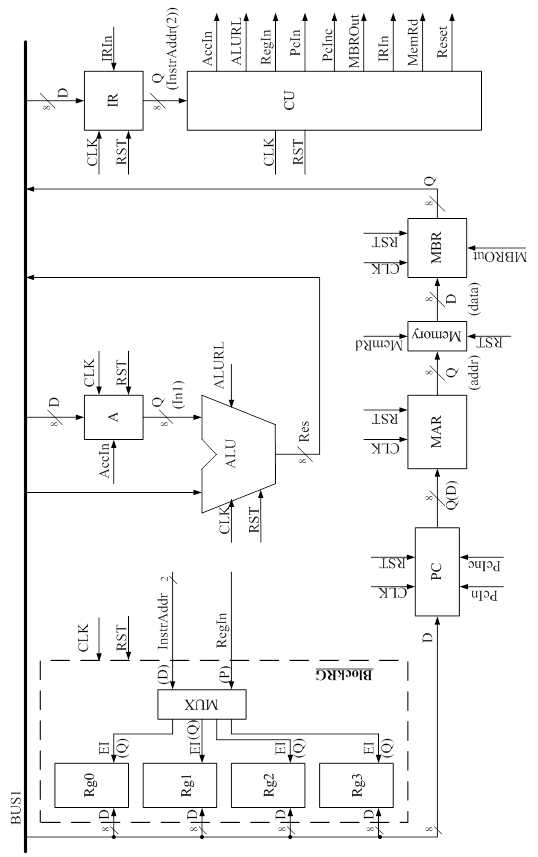

Временные диаграммы, описывающие выполнение микроопераций для каждой команды

3. Временные диаграммы, описывающие выполнение микроопераций для каждой команды

Пронумеруем операции процессора:

| Код операции | Команда | ||

| 0 | 0 | 0 | Mov A,#d |

| 0 | 0 | 1 | Mov Rn,#d |

| 0 | 1 | 0 | ADD Rn, A |

| 1 | 0 | 0 | JBC bit, rel |

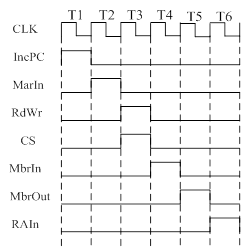

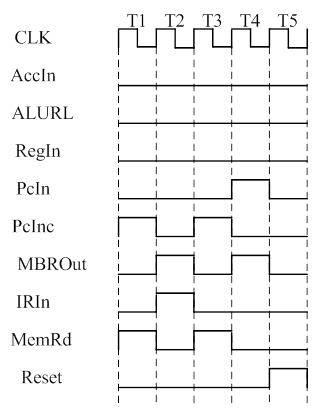

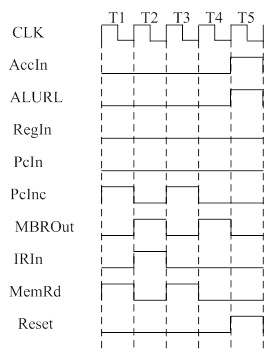

Временная диаграмма микроопераций выполнения команды MOV A, #d:

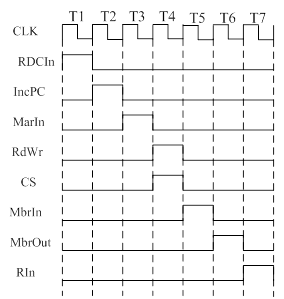

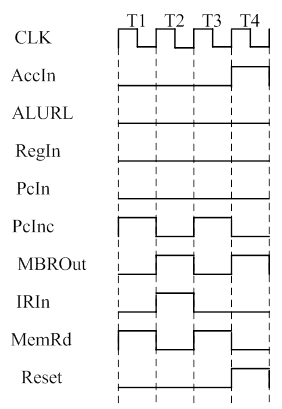

Временная диаграмма микроопераций выполнения команды MOV Rn, #d:

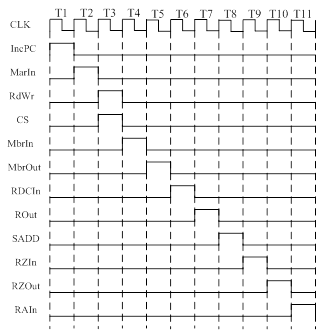

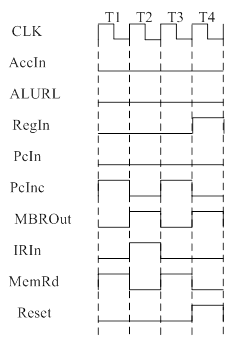

Временная диаграмма микроопераций выполнения команды Add A, Rn:

4. Содержательный алгоритм микропрограммы

Алгоритм выполнения команды в общем случае состоит из таких фаз:

1. Выборка команды из памяти по соответствующему адресу

2. Интерпретация команды (дешифрирование) и подача соответствующих управляющих сигналов

3. Загрузка данных

4. Выполнение команды

5. Подготовка к загрузке следующей команды

В случае с разрабатываемым процессором общий алгоритм выглядит следующим образом:

1. Запись значения программного счетчика в MAR (Memory Address Register).

2. Передача содержимого MAR на адресные входы памяти.

3. Передача сигнала чтения и выбора микросхемы памяти.

4. Запись данных из памяти в MBR (Memory Buffer Register).

5. Передача содержимого MBR на шину данных процессора и запись его в регистр команд IR (Instruction Register).

6. Выбор из памяти команд необходимой команды

7. Увеличение значения программного счётчика

8. Запись значения программного счетчика в MAR (Memory Address Register).

9. Выдача содержимого MAR на адресные входы памяти.

10. Выдача сигнала чтения и выбора микросхемы памяти.

11. Запись данных из памяти в MBR (Memory Buffer Register).

12. Выдача содержимого MBR на шину данных процессора.

13. Если команда mov, то запись значения с шины данных в аккумулятор или в один из регистров общего назначения, увеличение программного счётчика и переход к пункту 1.

14. Если команда ADD или SUB, то выводим на шину данных значение из выбранного ранее регистра общего назначения, затем подаём на АЛУ сигнал сложения либо умножения, эти действия происходят над данными из аккумулятора и данными с шины. Результат заносится в регистр результата, а затем с регистра результата переписывается в аккумулятор. Увеличение программного счётчика и переход к пункту 1.

15. Если команда JBC, то проверяется содержимое однобитного регистра, если оно равно единице, то происходит переход по адресу rel и регистр сбрасывается в ноль.

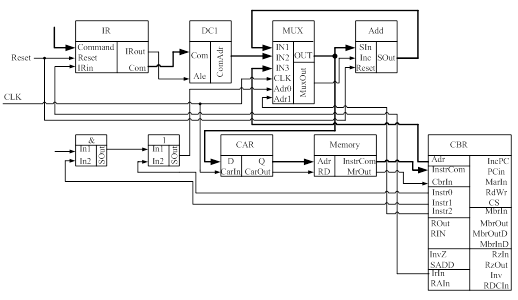

5. Синтез управляющего автомата на памяти с одним полем адреса

Структурная схема управляющего автомата на основе памяти с одним полем адреса показана на рис. 2.

Рис. 2. Структурная схема управляющего автомата на основе памяти с одним полем адреса

Следует определить набор управляющих сигналов, вырабатываемых устройством управления. Во-первых, это сигналы разрешения записи в регистры MAR, MBR, R0-R1, RzIn, IRIn. Во-вторых – сигналы выдачи содержимого регистров MAR, MBR, R0-R1 и Z. Кроме того – сигнал чтения из памяти, сигнал увеличения содержимого программного счетчика и сигнал выбора операции АЛУ. Ниже приведен полный список этих сигналов:

Instr0 – сигналы управления автоматом

Instr1

Instr2

ADR – адрес перехода

PCIn – сигнал загрузки в регистр команд

IncPC – увеличение значения счётчика команд

IrIn – загрузка в регистр инструкций

MarIn – загрузка в регистр команд

RdWr – сигнал чтения-записи памяти

CS – сигнал выбора микросхемы памяти

MbrIn – загрузка в буферный регистр из памяти

MbrOut – выдача на шину из буферного регистра

MbrInD – загрузка в буферный регистр с шины

MbrOutD – выдача в память из буферного регистра

RzIn – загрузка в регистр результата

RzOut – вывод из регистра результата

Inv – инвертирование значения подаваемого в АЛУ из аккумулятора

RAIn – загрузка в аккумулятор

RIn – сигнал загрузки в регистры общего назначения

ROut – сигнал вывода из регистров общего назначения

RDCIn – сигнал загрузки значения в мультиплексор номера регистра

SADD – сигнал сложения для АЛУ

InvZ – инвертирование результата

Похожие работы

... УПРАВЛЯЮЩЕГО АВТОМАТА НА ОСНОВЕ ЖЕСТКОЙ ЛОГИКИ Структурная схема управляющего автомата на основе жесткой логики показана на рис. 2. Рис. 2. Структурная схема управляющего автомата на основе жесткой логики Ниже записаны выражения для выходных сигналов шифратора: MemRd<='1' when c="00000001" or c="00000100" else '0' after 5ns; PCInc<='1' when c="00000001" or c="00000100" else '0' ...

... элементов, глобальное пространство имен, а также лавинообразную первоначальную загрузку сети. Таким образом ОСРВ SPOX имеет необходимые механизмы для создания отказоустойчивой распределенной операционной системы реального времени, концепция построения которой описана в главе 2. 4.3 Аппаратно-зависимые компоненты ОСРВ Модули маршрутизации, реконфигурации, голосования реализованы как аппаратно- ...

... состоянии am. Рассмотренные выше абстрактные автоматы можно разделить на: 1) полностью определенные и частичные; 2) детерминированные и вероятностные; 3) синхронные и асинхронные; Полностью определенным называется абстрактный цифровой автомат, у которого функция переходов и функция выходов определены для всех пар ( ai, zj). Частичным называется абстрактный автомат, у которого функция ...

... с приглашением по запросу (в машинной графике)required parameter обязательный параметрrequired space обязательный пробел (в системах подготовки текстов)requirements specification 1. техническое задание 2. описание требований к программному средствуrerun перезапуск, повторный запускreschedule переупорядочивать очередь (о диспетчере операционной системы)reschedule interval период переупорядочения ...

0 комментариев