Навигация

Застосування RISK- ядра у універсальних МП

2. Застосування RISK- ядра у універсальних МП.

Нагадаємо, що CISC- архітектура (повна система команд -- Complicated Instruction Set Computer) більш підходить для побудови універсальних МП, але RISC-архітектура (скорочена система команд -- Reduced Instruction Set Computer) забезпечує, у багатьох випадках, більшу швидкодію МП за рахунок можливості більш глибокої конвеєризації обчислень. Тому сучасні універсальні МП, залишаючись для користувача CISC – процесорами, часто мають RISC –ядро.

3. Інтеграція більшості контролерів периферійних та комунікаційних пристроїв безпосередньо у складі системних плат ПК (аудіо, відео, мережеві контролері, модеми та ін.). Така інтеграція зменшує час проходження сигналів між окремими компонентами обчислювальної системи, що позитивно впливає на загальну швидкодію системи.

4. Збільшення розрядності МП (внутрішньої та зовнішньої шин даних). Зрозуміло, що збільшення розрядності ШД, наприклад, з 32 до 64 розрядів, дозволяє передавати удвічі більший обсяг інформації за той самий інтервал часу.

5. Широке застосування багаторівневої кеш- пам’яті.

Збільшення ємності пам'яті МПС зумовлює зниження швидкодії операцій обміну інформацією між процесором та модулем пам'яті. Навіть за час звернення до пам'яті, що дорівнює 70 нс, неможливо отримати потрібну інформацію за один тактовий цикл шини. Це призводить до потреби виконання тактів очікування у процесі роботи процесора для того, щоб час звернення до пам'яті був узгоджений із часом виконання команди у процесорі. Підвищення швидкодії обміну інформацією можливе через реалізацію додаткової пам'яті порівняно невеликої ємності, звернення до якої відбувається на тактовій частоті процесора. Така пам'ять отримала назву кеш-пам 'яті або буферної пам 'яті. Кеш-пам'ять реалізується на основі ВІС ОЗП статичного типу. Інформаційна ємність та принцип організації кеш-пам'яті є одними з основних чинників, що визначають продуктивність роботи МПС.

Кеш-пам'ять використовують не тільки для обміну даними між МП і ОЗП, але й для обміну між ОЗП і зовнішніми накопичувачами. В основу роботи кеш-пам'яті покладено принципи часової і просторової локальностей програм.

Принцип часової локальності полягає в тому, що під час зчитування будь-яких даних із пам'яті існує висока ймовірність звернення програми протягом деякого невеликого проміжку часу знову до них.

Принцип просторової локальності ґрунтується на високій імовірності того, що програма через деякий невеликий проміжок часу звернеться до комірки пам'яті, наступної за тією, до якої вона зверталася перед цим.

Згідно з принципом часової локальності інформацію у кеш-пам'яті доцільно зберігати протягом деякого часу, а принцип просторової локальності вказує на доцільність розміщення у кеш-пам'яті вмісту декількох сусідніх комірок, тобто певного блоку інформації. Лінійні ділянки програм (без переходів) у більшості випадків не перевищують 3-5 команд, тому недоцільно використовувати блоки інформації, ємність яких перевищує ємність пам'яті, потрібну для зберігання 3-5 команд. Як правило, інформація з основної пам'яті завантажується у кеш-пам'ять блоками по 2-4 слова і зберігається там деякий час.

Під час звернення процесора до пам'яті спочатку перевіряють наявність у кеш-пам'яті даних, які запитують, і якщо їх немає, здійснюють завантаження у кеш-пам'ять потрібної інформації. Правильна організація роботи кеш-пам'яті забезпечує підвищення швидкодії системи, оскільки у більшості випадків відбувається звернення процесора до кеш-пам'яті, а не до більш повільної основної оперативної пам'яті.

В сучасних МП кеш-пам'ять команд та даних розділені для попередження конфліктів при одночасної їх вибірки. Крім того, кеш-пам'ять будується за ієрархічним, багаторівневим принципом. Наприклад, МП Pentium IV і Xeon кеш-пам'ять трьох рівнів.

Кеш-пам'ять першого рівня L1 називають також внутрішньою кеш-пам'яттю. Це найбільш швидкодіюча, але й найменша за ємністю кеш-пам'ять. Цю пам'ять розділено на два блоки: кеш-пам'ять даних і кеш-пам'ять команд (по 8... 16 кбайт).

Кеш-пам'ять команд L1, названа в останніх моделях Pentium IV кеш-пам'яттю трасування виконання ETC (Execution Trace Cache), містить мікрокоманди, декодовані вузлом завантаження-дешифрування в блоці оброблення команд.

Кеш-пам 'ять даних L1 використовують для завантаження і зберігання всіх типів даних: цілих, із плаваючою точкою і мультимедійних. Звернення до цієї пам'яті виконується двічі протягом одного такту.

Якщо дані не знайдено в кеш-пам'яті L1, то виконується звернення до менш швидкодіючої, але більшої за ємністю (від 256 кбайт до 1 Мбайт) кеш-пам'яті другого рівня (L2). Спочатку ця кеш-пам'ять розміщувалася на материнській платі, тому її інколи називають також зовнішньою кеш-пам'яттю. Кеш-пам'ять L2 виконано у вигляді одного блоку. Кеш-пам'ять передає 32 байт протягом одного такту процесора і для процесора, тактова частота якого 3,4 ГГц; швидкість обміну досягає 108,8 Гбайт/с.

У свою чергу, якщо дані не знайдено в кеш-пам'яті L2, то за допомогою системної шини виконується звернення до оперативної пам'яті.

У блок кеш-пам'яті останніх моделей процесорів Pentium IV і Хеоп між кеш-пам'яттю L2 і системною шиною добавлено кеш-пам 'ять третього рівня (L3). Ця найменш швидкодіюча пам'ять має ємність від 512 кбайт до 2 Мбайт. Кеш-пам'ять L3 також виконано у вигляді одного блоку.

Похожие работы

... на окремих кристалах. Мікропрограмні багатокристальні МП забезпечують велику гнучкість в досягненні потрібних користувачі характеристик (в першу чергу потрібної швидкодії мікропроцесорного пристрою або мікропроцесорної системи, надаючи користувачу можливість задавати спеціалізовану систему команд, орієнтовану на певне використання. Проте при цьому проектувальник повинен розробляти мікропрограми, ...

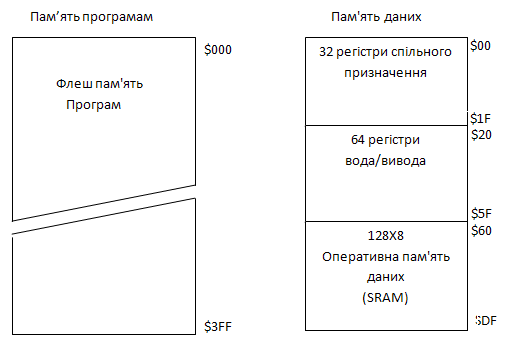

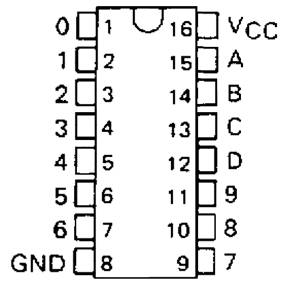

... дображення стану систем і т. п. В курсовому проекті я розробляю лічильник, який рахує число людей. 1.Основна частина 1.1 Розробка технічного завдання Загальні відомості: Мікропроцесорній пристрій, який рахує число імпульсів готової продукції. Призначення розробки: розробка МПС з навчальною метою. Вимоги до МПС: Тип МК ATtiny2313, індикація на 2 розряда, число імпульсів – 10, індикац ...

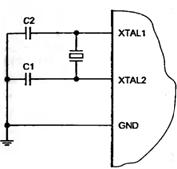

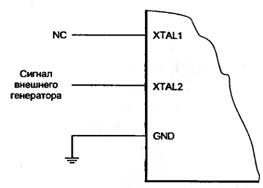

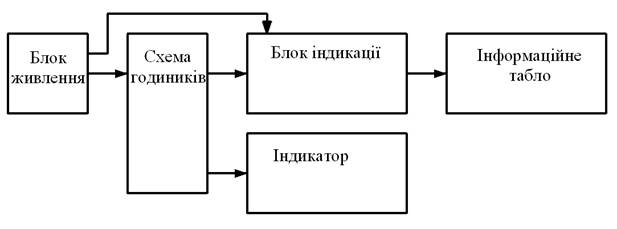

... 2.1 Розробка принципової схеми годинника 2.1.1 Етапи створення принципової схеми Для реалізації теми дипломного проекту, а саме проектування мікропроцесорної системи для багатоканального інформаційного табло, необхідно створити годинник та під’єднати його до табло. Розпочнемо з створення годинників. Для стабільної роботи та виконання відповідних функцій необхідно було обрати елементи для ...

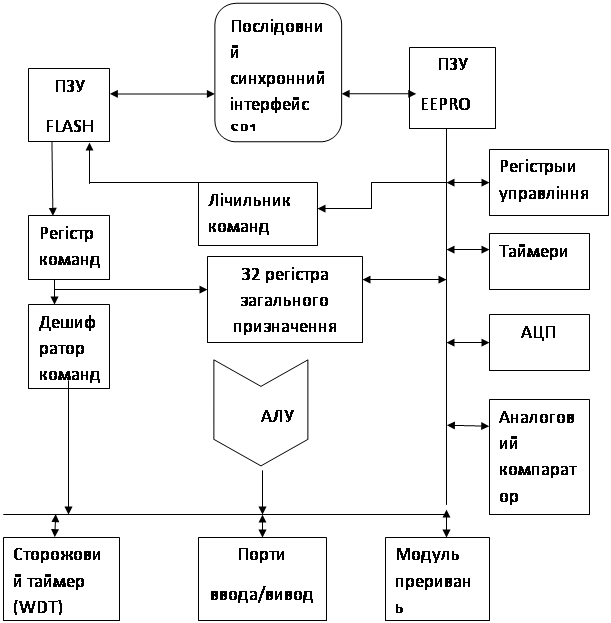

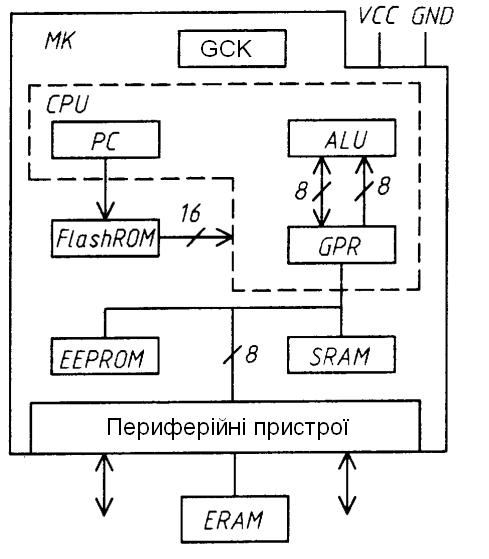

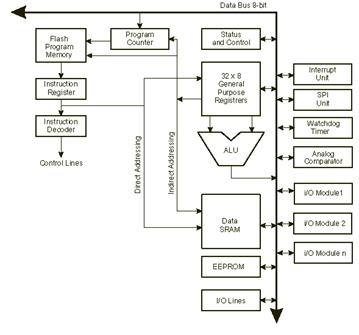

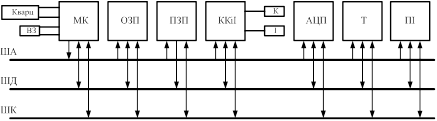

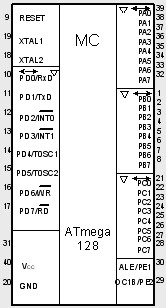

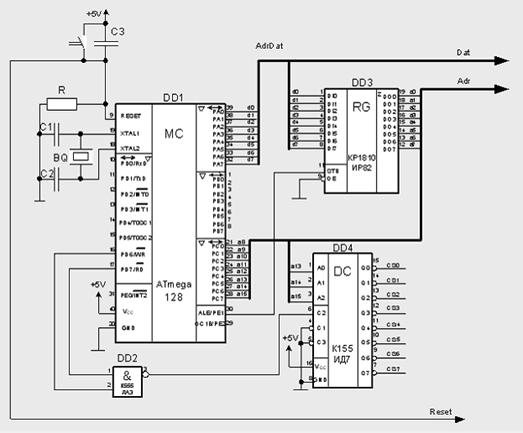

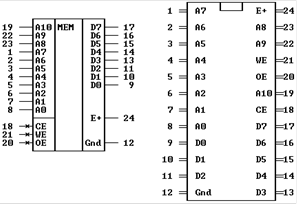

проводитись згідно завданню. Для побудови структурної схеми необхідно точно визначити необхідні вузли системи і зв'язку між ними. 2.1 Розробка мікропроцесорного блоку Основний елемент системи - мікроконтролер ATmega128, ATmega128L 8-розрядний AVR-мікроконтролер з внутрісистемно програмованою флэш-пам'яттю ємкістю 128 кбайт Відмітні особливості: Високопродуктивний, малопотужний 8-розрядний ...

0 комментариев