Навигация

Типова структура модульного МК

1.2. Типова структура модульного МК

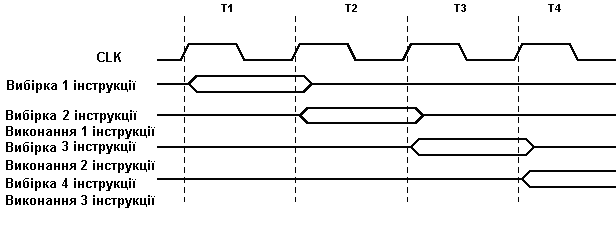

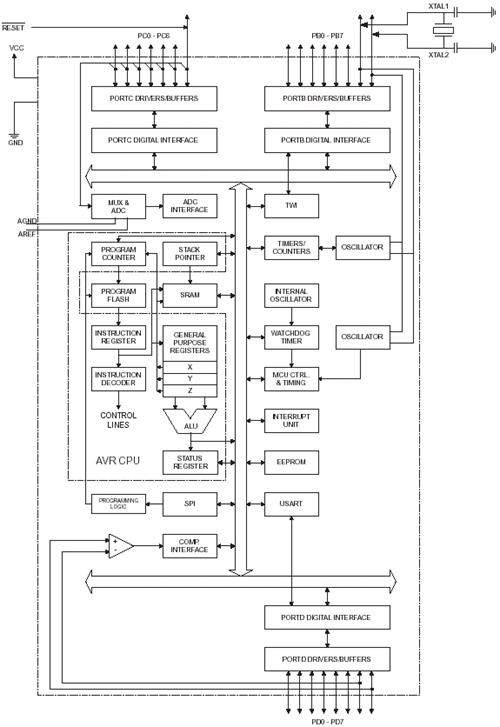

При модульному принципі побудови всі МК одного сімейства містять процесорне ядро, однакове для всіх МК даного сімейства, і змінюваний функціональний блок, що відрізняє МК різних моделей. Структура модульного МК подана на рис. 1.

| |

Процесорне ядро містить у собі:

· центральний процесор;

· внутрішню контролерную магістраль (ВКМ) у складі шин адреси, даних і керування;

· схему синхронізації МК;

· схему керування режимами роботи МК.

Змінюваний функціональний блок містить у собі модулі пам'яті різного типу й обсягу, порти введення/виведення, модулі тактових генераторів (Г), таймери. У відносно простих МК модуль обробки переривань входить до складу процесорного ядра. У більш складних МК він являє собою окремий модуль з розвиненими можливостями. До складу змінюваного функціонального блоку можуть входити і такі додаткові модулі, як компаратори напруги, АЦП і інші. Кожен модуль проектується для роботи в складі МК з урахуванням протоколу ВКМ. Даний підхід дозволяє створювати різноманітні МК у межах одного сімейства.

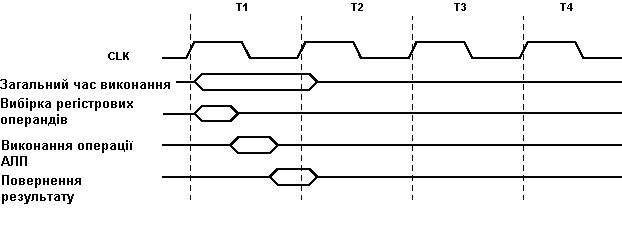

Процесорне ядро сучасних 8-розрядних МК може бути побудовано на основі CISC- архітектури (повна система команд -- Complicated Instruction Set Computer), або RISC-архітектури (скорочена система команд -- Reduced Instruction Set Computer).

CISC-процесори виконують великий набір різноманітних команд, даючи розроблювачеві можливість вибрати найбільше підходящу команду для виконання необхідної операції. Вибірка команди на виконання здійснюється побайтно протягом декількох циклів роботи МК. Час виконання команди може складати від 1 до 12 циклів. До МК із CISC-архітектурою відносяться МК фірми Intel з ядром MCS-51, що підтримуються в даний час великою кількістю виробників.

Схема синхронізації МК забезпечує формування сигналів синхронізації, необхідних для виконання командних циклів центрального процесора та мітки часу, які необхідні для роботи таймерів МК. Вона звичайно будується на основі дільників частоти опорної імпульсної послідовності. Сучасні МК містять вбудовані тактові генератори, але практично всі МК допускають роботу від зовнішнього джерела сигналу з метою завдання довільної тактової частоти МК.

У МК використовується три основних види пам'яті:

Пам'ять програм являє собою ПЗП, призначену для збереження програм і констант.

Пам'ять даних призначена для збереження змінних у процесі виконання програми і являє собою, як правило, статичне ОЗП. Термін «статичне» означає, що вміст комірок ОЗП зберігається при зниженні тактової частоти МК до як завгодно малих значень.

Регістри МК – внутрішні регістри процесора (акумулятор, регістри стану, індексні регістри) і регістри, що служать для керування периферійними пристроями (регістри спеціальних функцій).

Обсяг пам'яті даних МК, як правило, невеликий і складає звичайно десятки і сотні байт. Цю обставину необхідно враховувати при розробці програм для МК.

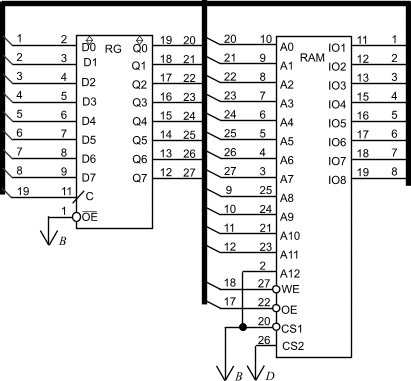

Незважаючи на існуючу тенденцію переходу до закритої архітектури МК, у деяких випадках виникає необхідність підключення додаткової зовнішньої пам'яті. Для цього використовуються порти введення-виведення. Такий спосіб дозволяє уникнути реалізації складних шинних інтерфейсів, однак приводить до зниження швидкодії системи при звертанні до зовнішньої пам'яті.

Кожен МК має декілька паралельних портів введення-виведення, які виконують роль пристроїв часового узгодження функціонування МК і об'єкта керування, що у загальному випадку працюють асинхронно. Звертання до регістра даних порту здійснюється тими ж командами, що і звертання до пам'яті даних. Крім того, у багатьох МК окремі розряди портів можуть бути опитані або встановлені бітовими командами процесора.

Більшість задач керування, що реалізуються за допомогою МК, виконуються у реальному часі. Під цим розуміється здатність системи одержати інформацію про стан керованого об'єкта, виконати необхідні розрахункові процедури і видати керуючі впливи (сигнали) на протязі інтервалу часу, достатнього для бажаної зміни стану об'єкта.

Покладати функції керування в реальному масштабі часу тільки на центральний процесор неефективно, тому що це займає ресурси, необхідні для розрахункових процедур. Тому в більшості сучасних МК використовується апаратна підтримка роботи в реальному часі з використанням таймерів.

Модулі таймерів служать для прийому інформації про час настання тих або інших подій від зовнішніх датчиків подій, а також для формування керуючих впливів у часі. Таймер – це 8-ми або 16-розрядний лічильник зі схемою керування. Схемотехнікою МК передбачається можливість використання таймера в режимі лічильника зовнішніх подій, тому його часто називають таймером/лічильником. Напрямок рахування – тільки прямий, тобто при надходженні вхідних імпульсів вміст лічильника інкрементується (збільшується на одиницю).

Лічильник може використовувати, у якості джерела вхідних сигналів як імпульсну послідовність з виходу керованого дільника частоти fBUS, так і сигнали зовнішніх подій. У першому випадку говорять, що лічильник працює в режимі таймера, у другому – у режимі лічильника подій.

Наступним етапом розвитку модулів підсистеми реального часу МК стали модулі процесорів подій. Вперше модулі процесорів подій були використані компанією Intel у МК сімейства 8x51Fx. Цей модуль одержав назву програмувального лічильного масиву (Programmable Counter Array — PCA). Він забезпечує більш широкі можливості роботи в реальному масштабі часу і меньше витрачає ресурси центрального процесора, чим таймери/лічильники. Тенденція розвитку підсистеми реального часу сучасних МК – збільшення числа каналів процесорів подій і розширенні їхніх функціональних можливостей.

Обробка переривань у МК відбувається відповідно до загальних принципів обробки переривань у МПС. Модуль переривань приймає запит переривання і організує перехід до виконання програми, що перериває. Запити переривань можуть надходити як від зовнішніх джерел, так і від джерел, розташованих у різних внутрішніх модулях МК (зовнішні та внутрішні переривання). Як входи для прийому запитів зовнішніх переривань найчастіше використовуються виводи паралельних портів.

Адреса, що завантажується в програмний лічильник при переході до обробки переривання, називається «вектор переривання». Питання про пріоритети при одночасному надходженні декількох запитів на переривання вирішується в різних МК по-різному. Є МК з однорівневою системою пріоритетів (усі запити рівноцінні), багаторівневою системою з фіксованими пріоритетами і багаторівневою програмованою системою пріоритетів.

Сучасні МК надають користувачеві великі можливості в плані економії енергоспоживання і мають наступні режими роботи:

- активний режим (Run mode) — основний режим роботи МК. У цьому режимі МК виконує робочу програму, і всі його ресурси доступні. Споживана потужність має максимальне значення PRUN.

- режим очікування (Wait mode, Idle mode або Halt mode). У цьому режимі припиняє роботу центральний процесор, але продовжують функціонувати периферійні модулі, що контролюють стан об'єкта керування. При необхідності сигнали від периферійних модулів переводять МК в активний режим, і робоча програма формує необхідні керуючі впливи. У режимі очікування потужність споживання МК знижується в порівнянні з активним режимом у 5...10 разів;

- режим останова (Stop mode, Sleep mode або Power Down mode). У цьому режимі припиняє роботу як центральний процесор, так і більшість периферійних модулів. Перехід МК зі стану останова в робочий режим можливий, як правило, тільки за перериваннями від зовнішніх джерел або після подачі сигналу скидання. У режимі останова потужність споживання МК PSTOP знижується в порівнянні з активним режимом приблизно на три порядки і складає одиниці мікроват.

З метою забезпечення надійного запуску, контролю роботи МК і відновлення працездатності системи (автоматічного скидання і ініціалізації) всі сучасні МК забезпечуються апаратними засобами забезпечення надійної роботи, а саме: схемою формування сигналу скидання МК, модулем моніторингу напруги живлення та сторожовим таймером.

Похожие работы

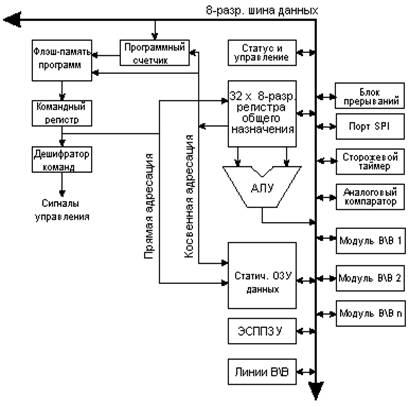

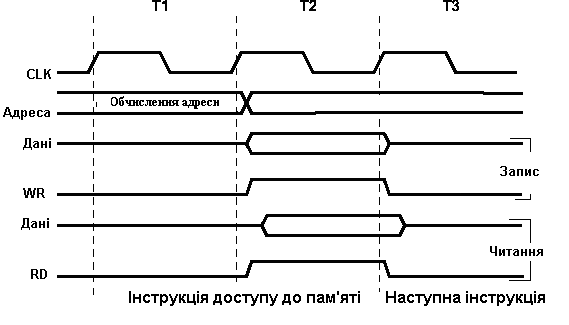

... повинно бути прийняте в розрахунок при порівнянні продуктивності різних моделей контролерів. 2. Однокристальні AVR-мікроконтролери Архітектуру RISC МК розглянемо на прикладі AT90S 2313. Це малопотужний восьмирозрядний КМОП МК, заснований на розширеній AVR RISC-архітектурі. Він належить до сім’ї AVR-МК загального призначення і створений дослідницьким центром фірми Atmel Corp. (Норвег ...

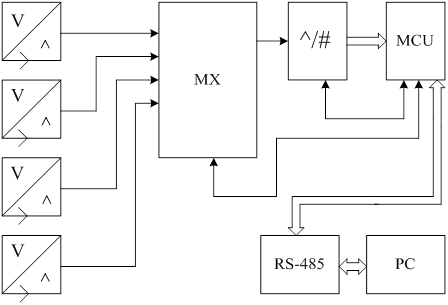

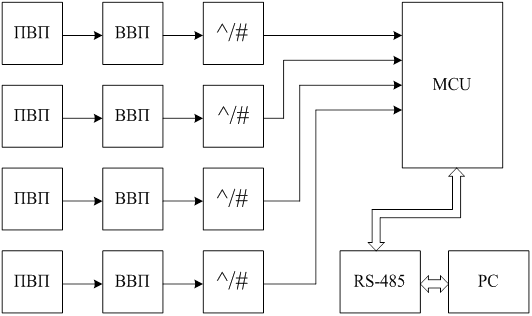

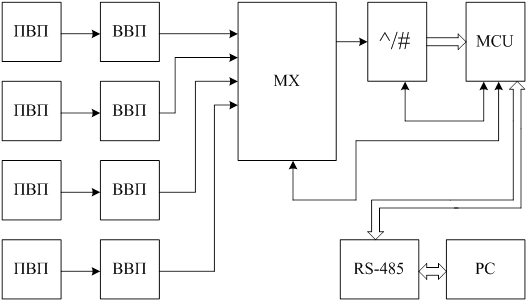

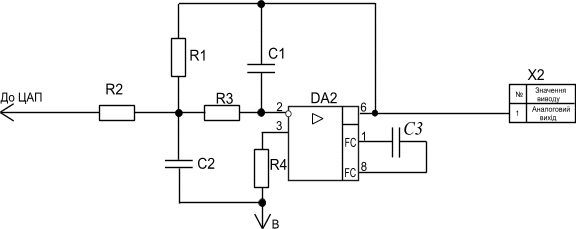

... габаритність та точність. Розглянемо першу структурну схему, яка приведена на рисунку 2.1. Рисунок 2.1 – Перший варіант реалізації структурної схеми системи для визначення складу вихлопних газів автомобілів Позначення на схемі: V/ – датчик концентрації, який використовується для визначення концентрації вихлопних газів автомобілів; МХ – мультиплексор; – аналого-цифровий перетворювач; ...

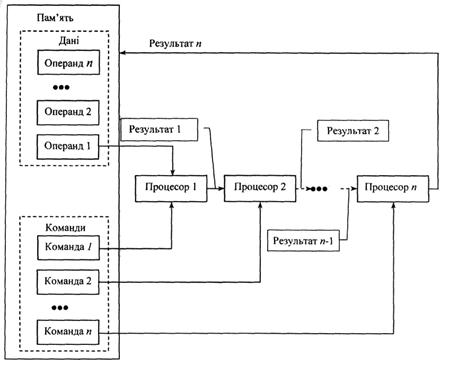

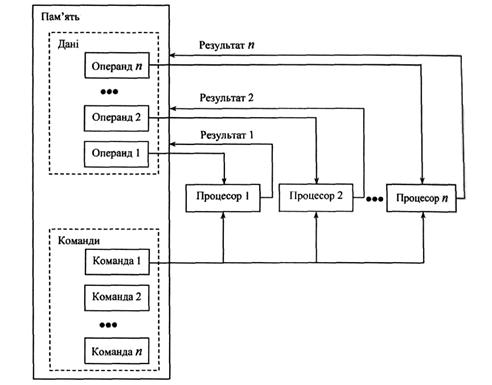

... для розв'язання особливо складних науково-технічних задач, оброблення великих обсягів даних у реальному масштабі часу, моделювання складних систем, автоматизованого проектування складних об'єктів, а також у системах керування (промислових і військових). Макет найпотужнішого суперкомп'ютера ES (Earth Simulator) Центра моделювання Землі (Earth Simulator Center) у Йокогамі (Японія) показаний рис. ...

... вводу-виводу, блок спряження із ПЕОМ та інші пристрої, що забезпечують роботу того чи іншого модулю. 1. Розробка структурної схеми МПС В даній курсовій роботі розробляється система управління та керування об’єктом на базі одно кристального RISK AVR-мікроконтролера (МК) ATMega1281V-8AU , що складається з: - Системи аналогового вводу інформації; - Системи аналогового виводу інформації; - ...

0 комментариев