Навигация

2.2 RISC-архитектура

В 70-е годы XX века ученые выдвинули революционную по тем временам идею создания микропроцессора, "понимающего" только минимально возможное количество команд.

Замысел RISC- процессора (Reduced Instruction Set Computer, компьютер с сокращенным набором команд) родился в результате практических исследований частоты использования команд программистами, проведенных в 70-х годах в США и Англии. Их непосредственный итог - известное "правило 80/20": в 80% кода типичной прикладной программы используется лишь 20% простейших машинных команд из всего доступного набора.

Первый "настоящий" RISC-процессор с 31 командой был создан под руководством Дэвида Паттерсона из Университета Беркли, затем последовал процессор с набором из 39 команд. Они включали в себя 20-50 тыс. транзисторов. Плодами трудов Паттерсона воспользовалась компания Sun Microsystems, разработавшая архитектуру SPARC с 75 командами в конце 70-х годов. В 1981 г. в Станфордском университете стартовал проект MIPS по выпуску RISC-процессора с 39 командами. В итоге была основана корпорация Mips Computer в середине 80-х годов и сконструирован следующий процессор уже с 74 командами.

По данным независимой компании IDC, в 1992 году архитектура SPARC занимала 56% рынка, далее следовали MIPS - 15% и PA-RISC - 12,2%

Примерно в то же время Intel разработала серию 80386, последних "истинных" CISC-процессоров в семействе IA-32. В последний раз повышение производительности было достигнуто только за счет усложнения архитектуры процессора: из 16-разрядной она превратилась в 32-разрядную, дополнительные аппаратные компоненты поддерживали виртуальную память, и добавился целый ряд новых команд.

Основные особенности RISC-процессоров:

ü Сокращенный набор команд (от 80 до 150 команд).

ü Большинство команд выполняется за 1 такт.

ü Большое количество регистров общего назначения.

ü Наличие жестких многоступенчатых конвейеров.

ü Все команды имеют простой формат, и используются немногие способы адресации.

ü Наличие вместительной раздельной кэш-памяти.

ü Применение оптимизирующих компиляторов, которые анализируют исходный код и частично меняют порядок следования команд.

RISC-процессоры 3-го поколения

Самыми крупными разработчиками RISC-процессоров считаются Sun Microsystems (архитектура SPARC - Ultra SPARC), IBM (многокристальные процессоры Power, однокристальные PowerPC - PowerPC 620), Digital Equipment (Alpha - Alpha 21164), Mips Technologies (семейство Rxx00 -- R 10000), а также Hewlett-Packard (архитектура PA-RISC - PA-8000).

Все RISC-процессоры третьего поколения:

ü являются 64-х разрядными и суперскалярными (запускаются не менее 4-х команд за такт);

ü имеют встроенные конвейерные блоки арифметики с плавающей точкой;

ü имеют многоуровневую кэш-память. Большинство RISC-процессоров кэшируют предварительно дешифрованные команды;

ü изготавливаются по КМОП-технологии с 4 слоями металлизации.

Для обработки данных применяется алгоритм динамического прогнозирования ветвлений и метод переназначения регистров, что позволяет реализовать внеочередное выполнение команд.

Повышение производительности RISC-процессоров достигается за счет повышения тактовой частоты и усложнения схемы кристалла. Представителями первого направления являются процессоры Alpha фирмы DEC, наиболее сложными остаются процессоры компании Hewlett-Packard.

Уменьшение набора машинных команд в RISC-архитектуре позволило разместить на кристалле вычислительного ядра большое количество регистров общего назначения . Увеличение количества регистров общего назначения позволило минимизировать обращения к медленной оперативной памяти, оставив для работы с RAM только операции чтения данных из оперативной памяти в регистр и запись данных из регистра в оперативную память, все остальные машинные команды используют в качестве операндов регистры общего назначения.

Основными преимуществами RISC-архитектуры является наличие следующих свойств:

- Большое число регистров общего назначения.

- Универсальный формат всех микроопераций.

- Равное время выполнения всех машинных команд.

- Практически все операции пересылки данных осуществляются по маршруту регистр – регистр.

Равное время выполнения всех машинных команд позволяют обрабатывать поток командных инструкций по конвейерному принципу, т.е. выполняется синхронизация аппаратных частей с учетом последовательной передачи управления от одного аппаратного блока к другому.

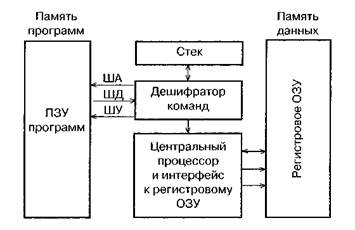

Аппаратные блоки в RISC-архитектуре:

Блок загрузки инструкций включает в себя следующие составные части: блок выборки инструкций из памяти инструкций, регистр инструкций, куда помещается инструкция после ее выборки и блок декодирования инструкций. Эта ступень называется ступенью выборки инструкций.

Регистры общего назначения совместно с блоками управления регистрами образуют вторую ступень конвейера, отвечающую за чтение операндов инструкций. Операнды могут храниться в самой инструкции или в одном из регистров общего назначения. Эта ступень называется ступенью выборки операндов.

Арифметико-логическое устройство и, если в данной архитектуре реализован, аккумулятор, вместе с логикой управления, которая, исходя из содержимого регистра инструкций, определяет тип выполняемой микрооперации. Источником данных помимо регистра инструкций может быть счетчик команд, при выполнении микроопераций условного или безусловного перехода. Данная ступень называется исполнительной ступенью конвейера.

Набор состоящий из регистров общего назначения, логики записи и иногда из RAM образуют ступень сохранения данных. На этой ступени результат выполнения инструкций записываются в регистры общего назначения или в основную память.

Однако к моменту разработки RISC-архитектуры, промышленным стандартом микропроцессоров де-факто стала архитектура Intel x86, выполненная по принципу CISC-архитектуры. Наличие большого числа программ, написанных под архитектуру Intel x86, сделала невозможным массовый переход ЭВМ на RISC-архитектуру. По этой причине основной сферой использования RISC-архитектуры явились микроконтроллеры, благодаря тому, что они не были привязаны к существующему программному обеспечению. Кроме того некоторые производители ЭВМ во главе с IBM так же начали выпускать ЭВМ, построенные по RISC-архитектуре, однако несовместимость программного обеспечения между Intel x86 и RISC-архитектурой в значительной степени ограничивала распространение последних.

Однако, преимущества RISC-архитектуры были столь существенны, что инженеры нашли способ перейти на вычислители, выполненные по RISC-архитектуре, при этом не отказываясь от существующего программного обеспечения. Ядра большинство современных микропроцессоров, поддерживающих архитектуру Intel x86, выполнены по RISC-архитектуре с поддержкой мультискалярной конвейерной обработки. Микропроцессор получает на вход инструкцию в формате Intel x86, заменяем ее несколькими (до 4-х) RISC-инструкциями.

Таким образом, ядра большинства современных микропроцессоров, начиная с Intel 486DX, выполнены по RISC-архитектуре с поддержкой внешнего Intel x86 интерфейса. Кроме того, подавляющее большинство микроконтроллеров, а так же некоторые микропроцессоры выпускаются по RISC-архитектуре.

В современном RISC-процессоре используется не менее 32 регистров, часто более 100, в то время, как в классических ЦВМ обычно 8-16 регистров общего назначения. В результате процессор на 20%-30% реже обращается к оперативной памяти, что также повысило скорость обработки данных. Кроме того, наличие большого количества регистров упрощает работу компилятора по распределению регистров под переменные. Упростилась топология процессора, выполняемого в виде одной интегральной схемы, сократились сроки ее разработки, она стала дешевле.

После появления RISC-процессоров традиционные процессоры получили обозначение CISC – то есть с полным набором команд (Complete Instruction Set Computer).

В настоящее время RISC-процессоры получили широкое распространение. Современные RISC-процессоры характеризуются следующим:

- упрощенным набором команд;

- используются команды фиксированной длины и фиксированного формата,

простые способы адресации, что позволяет упростить логику декодирования команд;

- большинство команд выполняются за один цикл процессора;

- логика выполнения команд с целью повышения производительности ориентирована на аппаратную, а не на микропрограммную реализацию, отсутствуют макрокоманды, усложняющие структуру процессора и уменьшающие скорость его работы;

- взаимодействие с оперативной памятью ограничивается операциями

пересылки данных;

- для обработки, как правило, используются трехадресные команды, что помимо упрощения дешифрации дает возможность сохранять большее число переменных в регистрах без их последующей перезагрузки;

- создан конвейер команд, позволяющий обрабатывать несколько из них одновременно;

- наличие большого количества регистров;

- используется высокоскоростная память.

В RISC-процессорах обработка машинной команды разделена на несколько ступеней, каждую ступень обслуживают отдельные аппаратные средства и организована передача данных от одной ступени к следующей.

Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняются несколько команд.

Выполнение типичной команды можно разделить на следующие этапы:

ü выборка команды IF - по адресу, заданному счетчиком команд, из памяти извлекается команда;

ü 2) декодирование команды ID – выяснение ее смысла, выборка операндов из регистров;

ü 3) выполнение операции EX, при необходимости обращения к памяти - вычисление физического адреса;

ü 4) обращение к памяти ME;

ü 5)запоминание результата WB

В процессорах с RISC-архитектурой набор исполняемых команд сокращен до минимума. Для реализации более сложных операций приходится комбинировать команды. При этом все команды имеют формат фиксированной длины (например, 12, 14 или 16 бит), выборка команды из памяти и ее исполнение осуществляется за один цикл (такт) синхронизации. Система команд RISC-процессора предполагает возможность равноправного использования всех регистров процессора. Это обеспечивает дополнительную гибкость при выполнении ряда операций. К МК с RISC-процессором относятся МК AVR фирмы Atmel, МК PIC16 и PIC17 фирмы Microchip и другие.

На первый взгляд, МК с RISC-процессором должны иметь более высокую производительность по сравнению с CISC МК при одной и той же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен.

Рис.2 Структура МК с RISC архитектурой

Гарвардская архитектура почти не использовалась до конца 70-х годов, пока производители МК не поняли, что она дает определенные преимущества разработчикам автономных систем управления.

Дело в том, что, судя по опыту использования МПС для управления различными объектами, для реализации большинства алгоритмов управления такие преимущества фон-неймановской архитектуры как гибкость и универсальность не имеют большого значения. Анализ реальных программ управления показал, что необходимый объем памяти данных МК, используемый для хранения промежуточных результатов, как правило, на порядок меньше требуемого объема памяти программ. В этих условиях использование единого адресного пространства приводило к увеличению формата команд за счет увеличения числа разрядов для адресации оперрандов. Применение отдельной небольшой по объему памяти данных способствовало сокращению длины команд и ускорению поиска информации в памяти данных.

Кроме того, гарвардская архитектура обеспечивает потенциально более высокую скорость выполнения программы по сравнению с фон-неймановской за счет возможности реализации параллельных операций. Выборка следующей команды может происходить одновременно с выполнением предыдущей, и нет необходимости останавливать процессор на время выборки команды. Этот метод реализации операций позволяет обеспечивать выполнение различных команд за одинаковое число тактов, что дает возможность более просто определить время выполнения циклов и критичных участков программы.

Большинство производителей современных 8-разрядных МК используют гарвардскую архитектуру. Однако гарвардская архитектура является недостаточно гибкой для реализации некоторых программных процедур. Поэтому сравнение МК, выполненных по разным архитектурам, следует проводить применительно к конкретному приложению.

Похожие работы

... AVR Studio запомнит расположение окон и использует эти установки при следующем запуске проекта. 3.2. Анализ методики реализации разработки программного обеспечения 3.2.1. Классификация вариантов заданий Цель заданий – практическое освоение методики программирования на ассемблере микроконтроллеров ATMEL семейства AVR, отладка программы на симуляторе AVR Studio и программирование кристалла с помощью ...

... напряжения. У ЦАП с токовым выходом этот параметр в большой степени зависит от типа выходного ОУ. Виды ЦАП Существуют последовательные и параллельные ЦАП. Последовательные –- используются в микропроцессорных системах, если не требуется высокое быстродействие. Среди параллельных - наиболее просты ЦАП с суммированием весовых токов Большинство схем параллельных ЦАП основано на суммировании ...

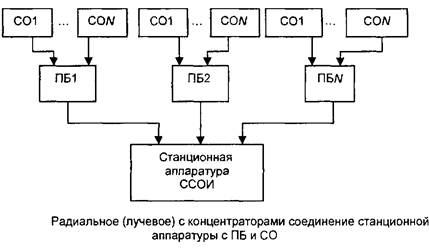

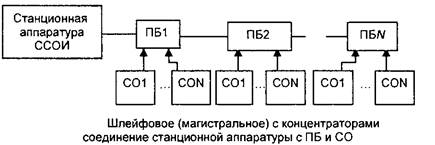

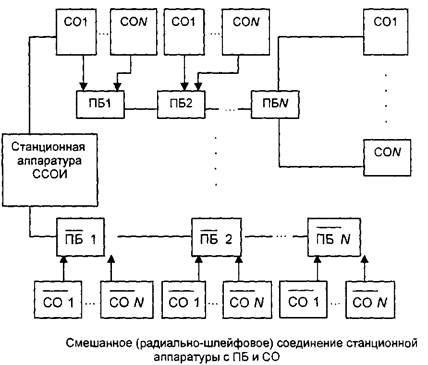

... Например, можно предложить классификацию, изображенную на рис. 1.13. Более определенно типы ТСО будут рассмотрены в последующих главах. Отметим лишь, что при выборе СО следует выяснять, каковы основные тактико-технические характеристики. Например, для особо важных объектов желательно, чтобы вероятность обнаружения СО была близка к 0.98; наработка на ложное срабатывание - к 2500 ч и к 3500 ...

... , 2 приложения. детекторная головка, измерительная часть, схема управления, система автокалибровки, микроконтроллер, коэффициент усиления, измерение, диод Шоттки. Работа выполнена с целью создания аппаратной части системы автокалибровки и измерения скалярных параметров СВЧ устройств (программная часть системы разрабатывается в рамках курсового проекта по курсу “Автоматизированное управление в ...

0 комментариев