Навигация

Исследование комбинационных устройств

Исследование комбинационных устройств

Екатеринбург 2005

КОМБИНАЦИОННЫЕ УСТРОЙСТВА

Устройства, оперирующие с двоичной (дискретной) информацией, подразделяются на два класса: комбинационные и последовательностные.

Комбинационные устройства (КУ) характеризуются отсутствием памяти.

Сигналы на их выходах в любой момент времени однозначно определяются сочетанием сигналов на входах и не зависят от предыдущих сигналов.

Схемными признаками таких устройств является отсутствие цепей обратной связи с выхода на вход. К КУ относятся сумматоры, дешифраторы, шифраторы, преобразователи кодов, мультиплексоры, демультиплексоры, схемы сравнения кодов и т.д.

Сумматоры. Сумматоры представляют собой функциональные цифровые устройства, выполняющие операцию сложения чисел. В цифровой технике суммирование осуществляется в двоичном или, реже, в двоично-десятичном коде. По характеру действия сумматоры подразделяются на комбинационные и накопительные. В свою очередь, каждый из сумматоров, оперирующий с многоразрядными числами, в зависимости от способа их сложения может быть отнесен к последовательному или параллельному типу. Сумматор имеет n входов разрядов слагаемого А, n входов разрядов слагаемого В и вход переноса cr (carry – перенос). Выходами сумматора являются n выходов разрядов суммы S и выход переноса (переполнения) CR. Сумматор характеризуется четырьмя значениями задержки распространения:

TCrs – от подачи входного переноса до установления всех выходов суммы. При постоянном уровне на всех входах слагаемых (а и b);

TAs – от одновременной подачи всех слагаемых до установления всех выходов суммы при постоянном уровне на входе переноса (выходной CR не учитывается);

TcrCR – от подачи входного переноса до установления выходного CR при постоянном уровне на входах слагаемых;

Tacr – от подачи всех слагаемых до установления выходного переноса CR при постоянном уровне на входах слагаемых.

Как последовательные, так и параллельные сумматоры строятся на основе одноразрядных суммирующих схем. Примером сумматора может быть микросхема серии К155ИМ2.

Шифраторы

Шифратором называется комбинационное устройство, преобразующее унитарный код, подаваемый на входные шины, в соответствующий код на выходах.

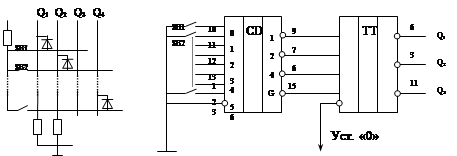

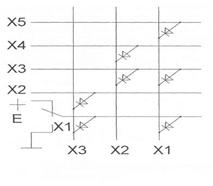

Задача шифратора сформировать код. На ввод шифратора могут подаваться различные сигналы: логический «0» через контакты кнопок клавиатуры управления или сигналы с других устройств, но во всех случаях в шифраторе происходит преобразование одного сигнала в n-разрядный код. На рисунке представлена схема шифратора на диодах. На следующей схеме (рисунок) если нажать на несколько кнопок сразу, а затем отпустить, то на выходе шифратора будет код последней отпущенной кнопки.

Если ни одна кнопка не нажата, то на выходах 1-2-4-G МС 1 устанавливается сигнал с уровнем логической единицы. При нажатии на одну из кнопок на выходе 1-2-4 появляется сигнал инверсного кода, соответствующий номеру нажатой кнопки, а на G-“0”. При отпускании кнопки здесь (на G) будет 1 и поэтому сигнал ДД2 запишет на выход код этой кнопки.

Рассмотрим подробнее структуру МС шифратора.

Классический шифратор имеет m входов и n выходов, и при подаче сигналов на один из входов (обязательно на один и не более) на выходе узла появляется двоичный код номера возбужденного выхода.

Число входов и выходов такого шифратора связано соотношением m=2n.

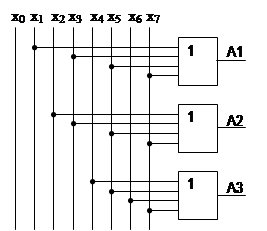

Для построения шифратора можно использовать схемы ИЛИ – по одной на каждый выход. При этом схема разбивается на n простых фрагментов. К входу элементов ИЛИ каждого выходного разряда должны быть подключены те входы шифратора, в двоичном представлении номера которых есть

единица в данном разряде. Так, к ИЛИ младшего разряда формируемого выходного кода должны быть подключены все нечетные входы, поскольку у всех нечетных номеров и только у них в младшем разряде содержится единица. Функциональная схема такого шифратора представлена на рисунке. Эту схему можно преобразовать по формулам де Моргана. В новом варианте вместо схемы ИЛИ будут И-НЕ.

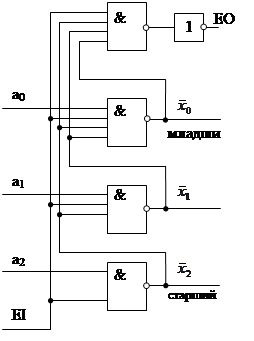

Совместно с шифратором в состав кодирующих узлов может входить схема выделения старше единицы. Эта схема преобразует m-разрядное слово следующим образом: все старшие нули и самая старшая единица входного кода пропускается на вход без изменения; все разряды более младшие, чем старшая единица, заменяются нулями. На схеме на входы а0,а1,а2и поступает преобразуемое слово (а0- младший разряд, а2- старший разряд), на вход EI (от enable in) – входной сигнал разрешения. При EI=1 схема работает следующим образом: любое число старших нулей порождает на выходах своих разрядов единицы и никак не влияет на работу элементов И-НЕ более младших разрядов. Любая самая старшая единица порождает на соответственном выходе нуль (активный низкий уровень выхода) и запирает все более младшие элементы И-НЕ, устанавливая на их выходах не активный высокий уровень. При этом низкий уровень появляется и на выходе EO (от enable out) – выходе разрешения.

Если разрядность обрабатываемого слова (число входных сигналов) превышает разрядность схемы, то слово разбивается на группы и выход EO более старшей группы подается на вход EI более младшей. При таком включении единица, поступившая на любой вход любой группы, запрет не только все более младшие разряды своей группы, но по цепи EO-EI и все более младшие группы. На выходах всей схемы останется только самая старшая единица входного слова, представленная активным низким уровнем.

Если к выходу схемы выделение старше единицы подключить шифратор, то в сумме получится функциональный узел приоритетного шифратора (priority encoder), формирующий в двоичном коде номе самой старшей единицы из всех, присутствующих во входном слове.

С выходами рассмотренной схемы хорошо стыкуются входы шифратора, двойственного по отношению к рассмотренному ранее (то есть на элемент И-НЕ): инверсным выходом одной схемы (битовое деление старше единицы) будут соответствовать инверсные входы другой, и весь приоритетный шифратор будет построен на технологичных элементах без лишних инверторов.

Если во входном слове присутствует только одна единица, то приоритетный шифратор будет выполнять функцию обычного шифратора. Поэтому МС обычных шифраторов не встречаются почти ни в одной серии, а приоритетные шифраторы - в составе многих серий.

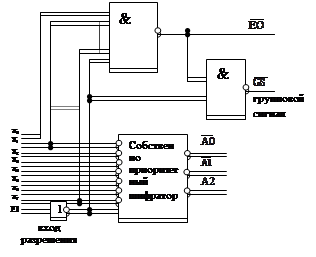

Упрошенная структура МС155ИВ1 представлено на рисунке.

| ВХОД | ВЫХОД | ||||||||||||

| E1 | a0 | a1 | a2 | a3 | a4 | a5 | a6 | a7 | GS | A0 | A1 | A2 | EO |

| B | X | X | X | X | X | X | X | X | B | B | B | B | B |

| H | B | B | B | B | B | B | B | B | B | B | B | B | H |

| H | X | X | X | X | X | X | X | H | H | H | H | H | B |

| H | X | X | X | X | X | X | H | B | H | B | H | H | B |

| H | X | X | X | X | X | H | B | B | H | H | B | H | B |

| H | X | X | X | X | H | B | B | B | H | B | B | H | B |

| H | X | X | X | H | B | B | B | B | H | H | H | B | B |

| H | X | X | H | B | B | B | B | B | H | B | H | B | B |

| H | X | H | B | B | B | B | B | B | H | H | B | B | B |

| H | H | B | B | B | B | B | B | B | H | B | B | B | B |

Из таблицы следует, что вход EI позволяет сделать все входы неактивными (а0-а7) при EI=1, т.е. напряжение высокого уровня на этом входе – это напряжение запрета при этом и на всех выходах высокий (неактивный) уровень.

На выходе GS низкий уровень, если хотя бы на одном выходе (сигнальном: а0,а1, а2) низкий, иначе хотя бы один из входов активный (кроме а0, при этом сигналы А0, А1, А2 и EO – высокие).

На EO низкий уровень, если на всех входах высокие уровни. Приоритетный шифратор обозначают так:

Эта схема до 16 входов. Для десятичной клавиатуры или декадных переключателей система шифратора может быть реализована следующим образом.

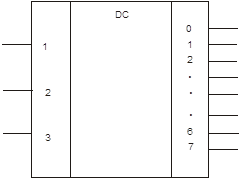

Дешифраторы. Дешифратор (декодер) – это комбинационное устройство с несколькими входами и выходами, у которого определенным комбинациям входных сигналов соответствует активное состояние одного из выходов. Дешифраторы преобразуют двоичный и двоично-десятичный коды в унитарный код, т.е. код двоичного и n-разрядного числа, представленного 2 разрядами, только один из разрядов которого равен 1.

Используются три структуры дешифраторов: матричная, каскадная и пирамидальная.

Если декодер имеет n входов m выходов и использует все возможные наборы входных переменных, то m=2n.

Такой декодер называют полным. Если используются лишь часть наборов, то такой декодер называют неполным. DC используют, когда нужно обращаться к различным цифровым устройствам, и при этом номер устройства(его адрес) представлен двоичным кодом.

Формально описать работу DC можно, задав список функций, отрабатываемых каждым из его выходов Yi? так для DC 3-8:

Yo =

Yo = ![]() ; Y1 =

; Y1 = ![]() ; Y2 =

; Y2 = ![]() ; Y3 =

; Y3 =![]() ; ... Y7 =a4a2a1,

; ... Y7 =a4a2a1,

а) б)

а) б)

Рис. 1. Матричный дешифратор 3-8: а)структура, б) условное обозначение

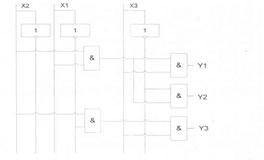

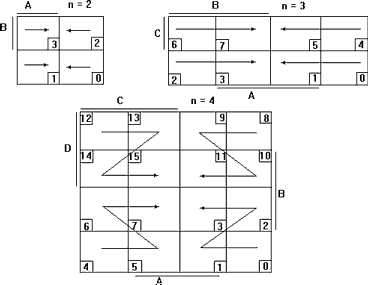

Матричные дешифраторы состоят из 2 логических схем совпадения (И), каждая из которых имеет n входов. На входы подаются все возможные комбинации прямых и инверсных разрядов дешифрируемого числа X. Пример матричного дешифратора 3x8 приведен на рис. 1.

Недостатком матричных дешифраторов является большое число входов логических элементов с ростом разрядности. Этот недостаток менее существен при использовании диодной логики. Пример такого дешифратора приведен рис. 2. Для того, чтобы такой дешифратор обладал свойством наращиваемое для увеличения разрядности входного числа, он должен строиться из одинаковых схем. На рис. 2 они обведены пунктирной линией. Так, дешифратор 2. может быть построен на основе двух таких схем, дешифратор 3x8- на основе трех схем и т.д.

Пирамидальные дешифраторы отличаются тем, что каждая конституента единицы формируется как конъюнкции одной из конституент предыдущего каскада и одного из разрядов входного числа, еще не использовавшегося для формирования конституент. Принцип построения пирамидального дешифратора иллюстрируется на рис. 3. Из схемы видно, что в этом случае можно использовать элементы на два входа.

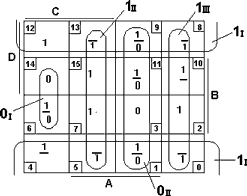

Дешифраторы входят в состав нескольких серий ТТЛ. В качестве примера приведено условное обозначение микросхем дешифратора 4x16 типа К155ИДЗ (рис. 4). Если на обоих входах разрешение VO=V1=0, микросхема работает как дешифратор. Потенциал VO=1, Vl=l устанавливает уровень "1" всех выходах независимо от состояния входов. Данные микросхемы позволяют наращивать разрядность дешифратора.

Рис. 4. Условное обозначение дешифратора типа К155ИДЗ

Рис.5. Шифратор микросхемы 5x3 на диодах

Преобразователи кодов (ПК). Предназначены для преобразования одного параллельного кода в другой. Они используются для шифрации и дешифрации цифровой информации и могут иметь n входов и К выходов. По назначению ПК можно разделить на два типа: с невесомым и с весовым преобразованиями кодов. В преобразователях первого типа отсутствует численная зависимость входного и выходного кодов, а имеет место символьная взаимосвязь. Например, преобразование двоично-десятичного кода в код семисегментного индикатора десятичных цифр.

Таблица 2

| Трехэлементный код | Пятиэлементный код | ||||||

| Х3 | Х2 | Х1 | У1 | У2 | У3 | У4 | У5 |

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 |

Преобразователи второго типа используются, как правило, для преобразования числовой информации, когда между числами входного и выходного кодов имеет место заданная математическая взаимосвязь.

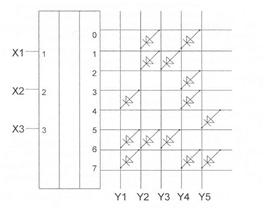

Преобразование n-элементного кода в к-элементный можно осуществить с предварительной дешифрацией первого кода и без нее.

В первом случае сначала дешифрируется n-элементный код и на каждой из 2 выходных шин получается сигнал, соответствующий одной из входных кодовых комбинаций. Затем каждый из выходных сигналов кодируется в к -элементном коде при помощи шифратора.

Рассмотрим в качестве примера преобразование трехэлементного кода в пятиэлементный согласно табл. 2. Схема, реализующая такой ПК, показана на рис. 6. В качестве дешифратора используется полный дешифратор 3x8, а в качестве шифратора – диодный матричный шифратор.

Рис.6.Схема, реализующая преобразование 3-элементного кода в 5-элементный

Мультиплексоры. Мультиплексором (MS) называется комбинационное устройство, предназначенное для коммутации в желаемом порядке сигналов с нескольких входных шин на одну выходную. С помощью мультиплексора осуществляется временное разделение информации, поступающей по разным каналам.

Мультиплексоры в микросхемном исполнении обладают двумя группами входов и одним или двумя взаимодополняющими выходами. Входы: информационные; управления; адресные; разрешающие. Если адресных входов n, то информационных входов — 2![]() . Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходом.

. Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединен с выходом.

Наличие разрешающего входа расширяет возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов. Этот вход используется также для наращивания разрядности.

Входы MS делятся на информационные, адресные и разрешающие (апробирующие). На первые подается информация, подлежащая передаче на выход. Адресные входы определяют нужный информационный вход. На разрешающий вход подается сигнал, разрешающий передачу информации со входа на выход. Наличие разрешающего его входа позволяет синхронизировать работу с работой других устройств, а также наращивать его разрядность.

Число адресных входов n позволяет коммутировать 2![]() входных каналов. Работа MS описывается следующим логическим уравнением:

входных каналов. Работа MS описывается следующим логическим уравнением:

![]()

где Di, - входные информационные сигналы;

mi, - минтермы, образованные переменными адресных шин;

Y - стробирующий сигнал.

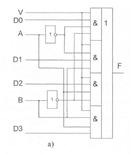

Из уравнения следует, что структура MS состоит из 2![]() схем совпадения, каждая из которых имеет n адресных, один информационный и один стробирующий вход, и одной схемы ИЛИ с п входами. Ее выход является выходом MS. Пример схемы MS с четырьмя информационными входами (4x1) приведен на рис. 7, а. Условное обозначение MS типа К155КП7 – на рис. 7, 6. Мультиплексоры в интегральном исполнении имеют возможность наращивания числа коммутируемых каналов.

схем совпадения, каждая из которых имеет n адресных, один информационный и один стробирующий вход, и одной схемы ИЛИ с п входами. Ее выход является выходом MS. Пример схемы MS с четырьмя информационными входами (4x1) приведен на рис. 7, а. Условное обозначение MS типа К155КП7 – на рис. 7, 6. Мультиплексоры в интегральном исполнении имеют возможность наращивания числа коммутируемых каналов.

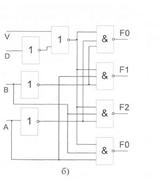

Демультиплексоры. Демультиплексоры (DS) в функциональном отношении противоположны мультиплексорам. В них сигналы с одного информационного входа распределяются в необходимой последовательности по нескольким выходам, соответствующим кодам на адресных входах. При n-разрядном адресе DS может иметь 2![]() выходов.

выходов.

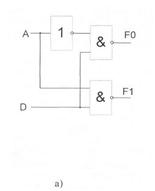

Принцип работы DS поясняет рис. 8. Здесь D – информационный, А – адресный входы. В зависимости от сигнала А (0 или 1) по адресному входу открыт верхний или нижний элемент И и через него сигнал D подключается к выходу Yo либо к выходу Y1.

Рис.7.Принцип работы схемы мультиплексора 4х I а) и микросхема К155 КП7 б)

Рис. 8. Принцип работы демультиплексора а), пример DS 1x4 б)

Как и мультиплексоры, PS дополняются управляющим входом Y . Пример демультиплексора 1x4 представлен на рис. 8, б.

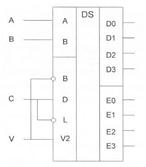

На рис. 9 показано условное обозначение микросхемы К155ИД4, которая может выполнять роль как демультиплексора, так и дешифратора. Если входы А, В, С использовать как адресные, а информации передавать на вход V, схема работает как демультиплексор 1x8. При Y = О она работает как дешифратор состояния трех входов А, В и С на восемь выходов (от До до Е3).

Похожие работы

... шумы анализатора), называют динамическим диапазоном по комбинационным помехам . Динамический диапазон по комбинационным помехам в анализаторах спектра миллиметрового диапазона волн в основном определяются КВЧ преобразователями входных сигналов. Исторически на начальных этапах освоения мм диапазона длин волн предпочтение отдавалось гармониковым преобразователям частоты и анализаторам ...

... D=1- W3W4(W1W5W6+ W7+ W1W8+ W2W6 W7+ W2W7+2W2W8+ 1)+ W5W6(W3W4(W7+ W1W5W6+ W2W7+ W2W8+1)-1) Для x1 Для x4 Для y Для х13 Задание 2. Синтез комбинационных схем. 2.1 Определение поставленной задачи Устройство, работа которого может быть представлена на языке алгебры высказываний, принято называть логическим. Пусть такое устройство имеет n ...

... в народном хозяйстве. Специальная часть. 3. 1. Определение задачи. Из задания на курсовое проектирование определим суть задачи: для некоторого синхронного цифрового автомата необходимо спроектировать устройство управления на основе жёсткой логики, которое в соответствии с заданными кодами микрокоманд формирует на выходной десятиразрядной шине управляющую последовательность цифровых сигналов. 3. ...

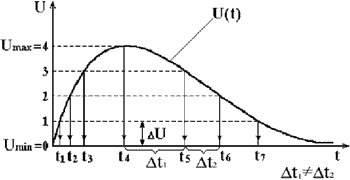

... показана на рисунке 8.4 Величина резистора R выбирается из условия [12] 240 Ом < R < 1,5 кОм.(8.5) Рисунок 8.4 Период генерируемых импульсов (8.6) 9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ 9.1 Комбинационные цифровые устройства (КЦУ) Логические устройства, выходные сигналы которых однозначно определяются комбинацией входных логических ...

0 комментариев