Навигация

Структура АЛУ для сложения и вычитания чисел с фиксированной запятой

6. Структура АЛУ для сложения и вычитания чисел с фиксированной запятой

При выполнении сложения положительные слагаемые представляются в прямом коде, отрицательные – в дополнительном. Производится сложение двоичных кодов, включая разряды знаков. Если при этом возникает перенос из знакового разряда суммы при отстуствии переноса в этот разряд или перенос в знаковый разряд при отсутствии переноса из разряда знака, то имеется переполнение разрядной сетки соответственно при отрицательной и положительной суммах. Если нет переносов из знакового разряда и в знаковый разряд суммы или есть оба этих переноса, то переполнения нет и при 0 в знаковом разряде сумма положительна, а при 1 отрицательна и представленя в ДК.

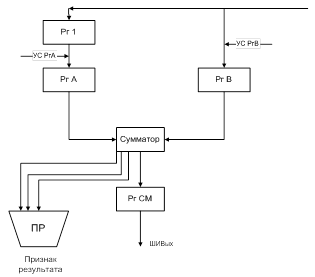

Алгоритм работы:

1) Из памяти по входной информационной шине в АЛУ поступают операнды, причем положительные числа – в прямом, а отрицательные – в дополнительном коде.

2) РгВ – первое слагаемое или уменьшаемое

3) РгА – второе слагаемое или вычитаемое. Рг1 связан с РгА цепями прямой и инверсной передачи кода. Прямая передача используется при сложении, инверсная - вычитания

4) Результат операции выдается из АЛУ в оперативную память по выходной информационной шине ШИВых. 5)При выполнении операции в АЛУ формируется 2-разрядный код признака результата ПР.

| Результат | Признак | результата |

| 0 | 0 | 0 |

| <0 | 0 | 1 |

| >0 | 1 | 0 |

| Переполнение | 1 | 1 |

6) Операция алгебраического вычитания Z=X-Y=X+(-Y) может быть сведена к изменению знака вычитаемого Y и операции алгебраического сложения. Изменение знака – принятый в Рг1 код инверсно передается в РгА и при сложении осуществляетя подсуммирование 1 в младший разряд сумматора.

7) Передача информации в регистрах АЛУ производится отдельными микрооперациями, инициируемыми соотвествующими УСами.

7. Структура АЛУ для умножения чисел с фиксированной запятой (сумматор частичных произведений)

В ЭВМ операция умножения чисел с фиксированной запятой с помощью соответствующих алгоритмов сводится к операциям сложения и сдвига. Произведение двух (n-1)-разрядных чисел может иметь 2(n-1) значащих разрядов. Т.о. при операции умножения целых чисел необходимо предусмотреть возможность формирования в АЛУ произведения, имеющего двойную по сравнению с сомножителем длину. В ЭВМ, в которых числа с фиксированной запятой являются дробями, младшие n-1 разрядов произвдения часто отбрасываются (возможно с операцией округления).

Для выполнения умножения АЛУ должно содержать регистры множимого, множителя и схемы формирования суммы частичных произведений – сумматор частичных произведений, в котором путем соответствующей организации передач производится последовательное суммирование частичных произведений.

Операция умножения состоит из n-1 [(n-1) – число цифровых разрядов множителя] циклов. В каждом цикле анализируется очередная цифра множителя, и если это 1, то к сумме частичных произведений прибавляется множимое, в противном случае прибавления не происходит. Цикл завершается сдвигом множимого относительно суммы частичных произведений либо сдвигом суммы частичных произведений относительно неподвижного множимого.

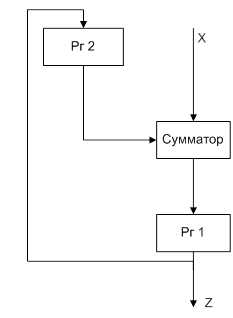

8. Умножение начиная с младших разрядов множителя со сдвигом суммы частичных произведений вправо и при неподвижном множимом

Регистр множителя и сумматор частичных произведений при этом должны иметь цепи сдвига вправо. Регистр множимого может не иметь цепей сдвига. Последовательность действий в каждом цикле выполнения умножения определяется младшим разрядом регистра множителя, куда последовательно одна за другой поступают цифры множителя. Поскольку по мере сдвига множителя вправо старшие разряды регистра множителя освобождаются, он может быть использован для хранения младших разрядов произведения, поступающих из младшего разряда сумматора частичных произведений по мере выполнения умножения. Для этого при выполнении сдвига младший разряд регистра сумматора частичных произведений соединяется со старшим разрядом регистра множителя. После выполнения умножения старшие разряды произведения находятся в ргеистре сумматора, младшие – в регистре множителя. При данном методе умножения все три регистра имеют одинаковую длину, равную числу разрядов сомножителей. Этот метод нашел наибольшее применение в ЭВМ.

Алгоритм: 1. Берутся модули от сомножителей.

2. Исходное значение суммы частичных произведений принимается равным 0

3. Если анализируемая цифра множителя равна 1, то к сумме частичных произведений прибавляется множимое; если эта цифра 0, прибавление не производится.

4. Производится сдвиг суммы частичных произведений вправо на один разряд.

5. Пункты 3 и 4 последовательно выполняются для всех цифровых разрядов множителя, начиная с младшего.

6. Произведению присваивается знак плюс, если знаки сомножителей одинаковы, минус – в противном случае.

9. Умножение, начиная с младших разрядов множителя при сдвиге множимого влево и неподвижной сумме частичных произведений

Регистр множителя должен иметь цепи сдвига вправо, регистр множимого – влево, сумматор не должен иметь цепей сдвига. Последовательность действий определяется младшим битом регистра множителя. При этом методе регистр множимого и сумматор частичных произведений должны иметь двойную длину. Этот метод требует больше оборудования, но никаких преимуществ не дает, поэтому его применение нецелесообразно.

Похожие работы

... на кристалл) и средней степени интеграции (СИС - 10 -1000 компонентов на кристалл). Появилась идея, которая и была реализована, проектирования семейства компьютеров с одной и той же архитектурой, в основу которой положено главным образом программное обеспечение. В конце 60-х появились мини-компьютеры. В 1971 году появился первый микропроцессор. Быстродействие (операций в секунду) порядка 1 млн ...

... это делать. Буфера адресов позволяют в конечном итоге сгладить неравномерность поступления запросов к памяти и тем самым повысить эффективность ее использования. Третьей структурной особенностью БЭСМ-6 является метод использования сверхоперативной, неадресуемой из программы памяти небольшого объема, цель которого≈автоматическая экономия обращений к основному оперативному запоминающему ...

... процессоры, входящие в состав периферийных устройств). В многомашинной вычислительной системе несколько процессоров, входящих в вычислительную систему, не имеет общей оперативной памяти, а имеют каждый свою (локальную). Каждый компьютер в многомашинной системе имеет классическую архитектуру, и такая система применяется достаточно широко. Однако эффект от применения такой вычислительной системы ...

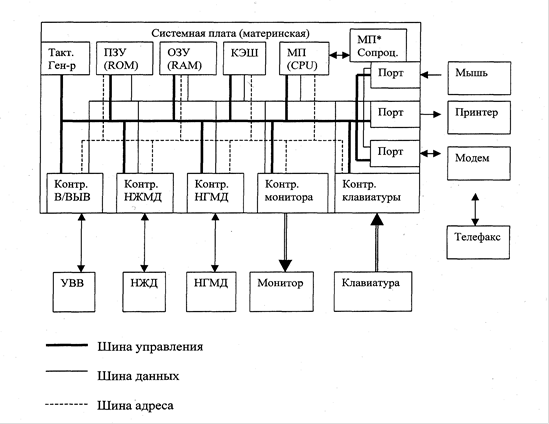

... пользователя. С помощью клавиатуры управляют компьютерной системой, а с помощью монитора получают от нее оклик. Принцип действия. Клавиатура относится к стандартным средствам персонального компьютера. Ее основные функции не нуждаются в поддержке специальными системными программами (драйверами). Необходимое программное обеспечения для начала работы с компьютером уже имеется в микросхеме ПЗУ в ...

0 комментариев