Навигация

Разаработка аппаратных средств

2. Разаработка аппаратных средств.

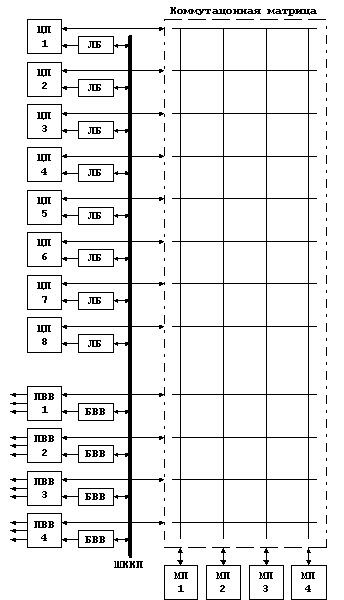

Наряду с подключение банка глобальной памяти к СМ, предусмотрено подключение 24

устройств Ввода/Вывода к СМ, основное назначение которых – производить обмен

информацией между процессорными модулями и пользователями данной ВС.

Обмен информацией иницируется либо Внешним Устройством через централизованный

контроллер прерываний, при этом необходимо отметить, что каждый ПЭ может

получить доступ для обмена с ВУ с помощью механизма прерываний либо обмен

информацией инициируется процессорным элементом, при этом процессор в

программном режиме может обратиться к любому ВУ, подключенному к СМ. Как

достоинство такого решения следует отметить расширение возможностей

процессорного элемента по передаче данных, как недостаток – это увеличение

времени доступа к ВУ, так как требуется дополнительное время на арбитраж доступа

к СМ.

Функционирование МВС

МВС функционирует под управлением многозадачной ОС, построенной по принципу

Ведущий-Ведомый (Master-Slave). При этом одиниз процессоров системы определяется

как ведущий, а остальные – как ведомые. Ведущий процессор согласует работу и

взаимодействие ведомых процессоров.

Ядро ОС храниться в глобальной памяти, поэтому в случае выхода из строя ведущего

процессора либо при необходимости организации на данном процессоре решения

автономной (самостоятельной) задачи, его функции может взять на себя любой

другой процессорный элемент системы, загрузив в свою локальную память часть

основного кода из ядра ОС.

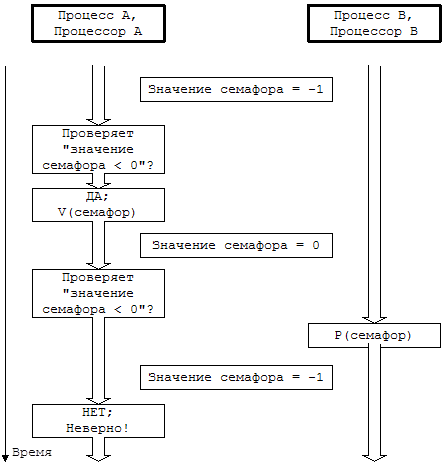

Синхронизация обмена информацией и взаимодействие задач на программном уровне

производиться с помощью механизма мониторов и семафоров, при этом

предполагается, что все данные, с которыми работает процессор в данной задаче

должны быть перенесены из глобальной памяти в локальную память данного

процессора с целью уменьшения времени доступа к ним.

2 Разработка аппаратных средств

МВС выполняется из отдельных процессорных модулей, подключенных к СМ. К СМ

подключен также банк глобальной памяти и ВУ Ввода/Вывода.

Младшие 1М адресного пространства каждого процесора выделяются под локальную

память. Старшие 12М выделяются под глобальную память и являются общими для всех

процессоров. В связи с этим возможно возникновение конфликта доступа к общему

ресурсу. Для решения данной проблемы применяется схема централизованного арбитра

доступа к общему ресурсу. В частности в каждый процессорный модуль входит схема

блока коммутации адресов, которая предназначена для определения адреса,

выставляемого ПЭ (см ИАЛЦ 462631 001.Э2 МВС. Схема электрическая

функциональная). Если в регистр адреса ПЭ поступает адрес, то блок коммутации

анализирует 4 старших разряда адреса. Если хотя бы в одном разряде присутствует

1, то очевидно, что обращение идет к банку глобальной памяти.

В таком случае вырабатывается сигнал ТПДП – требование прямого доступа к

глобальной памяти, который через интерфейс арбитра (внутренний автомат)

поступает на Централизованный Арбитр Доступа (ЦАД), как сигнал ТШ (требование

шины). Если шина свободна, то ЦАД вырабатывает сигнал РШ (разрешение шины),

который преобразуется интерфейсом арбитра в ППДП и процессор подключается к

глобальной шине для операций Чтения/Записи.

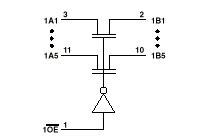

Контроль работы процессорного модуля осуществляется блоком контроля (БК).

Реализован метод контроля с аппаратным сравнением эталонов. Функциональная схема

блока контроля со схемой сравнения кодов представлена на рис.2.2.

Хочется отметить ту особенность, что в данной схеме скорректирован недостаток

простейшего блока контроля, работающего по методу сравнения контрольных и

эталонных слов – снижение бысродействия за счет большого распада команд, но за

счет усложнения аппаратуры.

При выходе ПМ из строя, на выходе блока контроля формируется сигнал ошибки,

который представляет собой 8-битовую последовательность, каждый бит которой

несет информацию о текущем состоянии соответствующего ПМ (0-ПМ в рабочем

состоянии, 1-ПМ вышел из строя) и выставляет его на СМ каждый раз по

срабатыванию таймера ПМ. Блок Выбора Мастера(БВМ) каждый раз анализирует

вышеописанный сигнал ошибки, и в случае обнаружения отказа ПМ-Мастера назначает

Мастером любой другой работоспособый ПМ, о чем объявляет выставлением на БК ПМ

сигнала НМ(номер мастера).

3 Разработка программного обеспечения

3.1 Общие принципы построения ОС

Для проектируемой МВС в качестве основной выбрана ОС, построенная по принципу

Ведущий-Ведомый(Master-Slave), поэтому все процессоры системы делятся на две

категории:

1.Главный процессор – Ведущий (Master)

2.Вспомогательный процессор – Ведомый (Slave)

Главный процессор имеет статус выше, чем у всех остальных ПМ МВС. Поэтому

выполнение управляющих фуекций ОС МВС осуществляется на главном процессоре.

После запуска системы, вспомогательные процессоры обращаются к главному за

получением работы, а также за предоставлением ОС МВС программного интерфейса.

Все сервисные программы ОС должны иметь возможность быть выполненными на любом

процессоре, входящем в МВС. На главном процессоре осуществляется планирование

процессов во времени, а также распределение их по ресурсам (процессорам), т.е. в

пространстве.

Основным достоинством данного метода является относительная простота. Данную ОС

можно получить сравнительно несложным расширением возможностей многозадачных ОС,

используемых в однопроцессорных системах. Добавляются новые возможности,

связанные с одновременным выполнением задач. Как достоинство можно отметить

также и простоту управления ресурсами, поскольку все функции, связанные с

управлением решаются в одном узле.

Рассморим недостатки данного типа ОС. Главной проблемой функционирования таких

систем является их относительно низкая надежность. А именно, поскольку

управление системой осуществляется одним процессорным модулем(Мастером), то

выход его из строя может привести к приостановке работы всей системы.

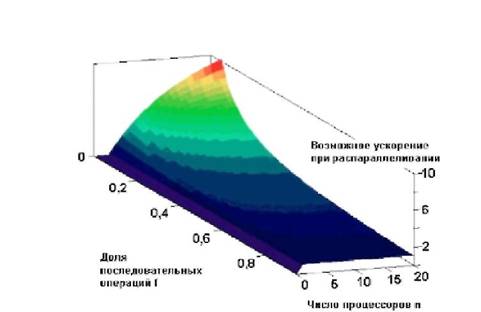

Вторым важным недостатком является низкая эффективность управления ресурсами,

поскольку один Ведущий процессор не может обеспечить высокую загрузку множества

Подчиненных процессоров.

Для устранения первого недостатка, т.е. повышения надежности системы, в

разрабатываемой МВС предусмотрена возможность отслеживания подчиненными

процессорами работоспособности главного процессора: в случае выхода его из

строя, о чем говорит сигнал Error на СМ блок выбора мастера производит

принудительное назначение первого попавшегося Подчиненного процессора на роль

Ведущего процессора системы, который при этом производит загрузку в свою

локальную память копию ядра ОС из ПЗУ глобальной памяти. Подробное описание

данной процедуры приведено в подразделе 3.2 Примеры алгоритмов программ.

Устранения второго недостатка, т.е. повышения эффективности управления

ресурсами, связано с возможностью назначения более одного процессора на роль

Ведущего: в этом случае можно снять нагрузку по распараллеливанию заданий на

процессоры с одного процессора на несколько, но в проектируемой МВС данный метод

не применяется ввиду возникающего при этом усложнения аппаратной реализации МВС.

3.2 Примеры алгоритмов программ

Для детального ознакомления с основными принципами функционирования

проектируемой МВС в качестве наглядных примеров предлагается к рассмотрению

следующие алгоритмы:

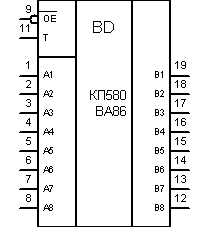

4 Разработка принципиальной схемы

Для разработки принципиальной схемы проектируемой МВС был задан централизованный

арбитр доступа к ОР с абсолютным географическим приоритетом ПМ.

4.1 Централизованный арбитр доступа к ОР

Параметры арбитра:

Тип арбитра – централизованный

Приоритет ПМ – абсолютный географический

Автомат – синхронный

Заключение

В данном курсовом проекте была разработана Многопроцессорная Вычислительная

Система с 8 ПМ, централизованным арбитром доступа к общему ресурсу с абсолютным

географическим приоритетом ПМ, с централизованным контроллером приоротетных

прерываний для обслуживания ВУ и организации взаимодействия между ПМ-Ведущим и

ПМ-Подчиненным (при помощи системы прерываний).

Результаты разработок предоставлены в виде схемы электрической функциональной

ИАЛЦ 462631005.Э2, схемы электрической принципиальной ИАЛЦ 462631001.Э2

Централизованного Арбитра Доступа к ОР.

В ходе проведения проектирования МВС были произведены расчеты :

общий расчет надежности системы (результат – время наработки на отказ составит

14 409 часов)

расчет потребляемой мощности

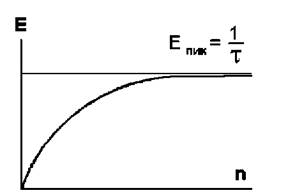

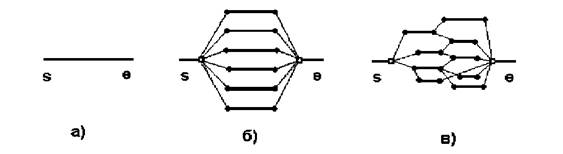

расчет производительности МВС.

Были разработаны и описаны алгоритмы отражающие:

взаимодействие процессоров между собой на примере операции обмена данными;

процесс реконфигурации системы.

Был разработан и оформлен полный комплект технической документации, отражающий

функциональные особенности разработанной МВС и предоставляющий подробное

описание функционирования как МВС в целом, так и отдельно рассмотренных ее

модулей.

Похожие работы

... 5k управления ресурсами (программно-аппаратный комплекс) массивно-параллельного компьютера обязана обрабатывать подобные ситуации в обход катастрофического общего рестарта с потерей контекста исполняющихся в данный момент задач. 2.4.1 Массивно-параллельные суперкомпьютеры серии CRY T3 Основанная в 1972 году фирма Cry Research Inc. (сейчас Cry Inc.), прославившаяся разработкой векторного ...

... процесса, а либо вообще не сказываются на работе МПВК, либо вызывают постепенную деградацию вычислительной мощности. Меры по обеспечению отказоустойчивости свои для каждого компонента МПВК. Отказы оперативной памяти были рассмотрены выше. Отказы в коммутационной матрице также как и отказы оперативной памяти целесообразно маскировать применением кодов, корректирующих ошибки. Наиболее сложны для ...

... характер сигналов интерфейса и их временную диаграмму, а также описание электрофизических параметров сигналов. На рис. 2.2 представлена общая схема сопряжения МП с устройствами ввода-вывода УВВ и ОЗУ в микропроцессорной системе. Рис 2.2. Схема интерфейсных связей микропроцессора Связь МП с УВВ требует пять групп связей, обеспечиваемых через выводы корпуса МП. По группе шин 1 передается ...

... канал ввода-вывода и внешнее запоминающее устройство, что требует много времени. 1. Разработка структурной схемы Целью данного курсового проекта является разработка структуры многопроцессорного вычислительного комплекса с многовходовым ОЗУ. Структурная схема такого МПВК приведена в приложении на схеме 1. Рассмотрим блоки, представленные на данной схеме. 1. Блок генерации сигналов. ...

0 комментариев