СИНТЕЗ ЛОГИЧЕСКОЙ СХЕМЫ ТТЛШ

Комплексное задание

по практическим занятиям и лабораторным работам

по дисциплине: «Проектирование и конструирование

полупроводниковых приборов и ИМС»

Синтез принципиальной электрической схемы.

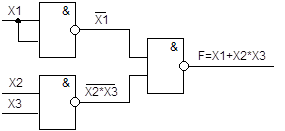

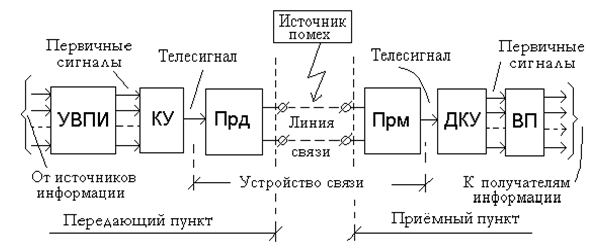

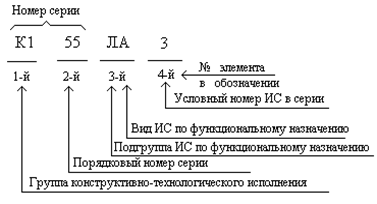

Исходя из технический параметров ИМС приведенных в ТЗ реализуем логическую функцию F=X1+X2×X3 на основе логической схемы ТТЛШ (на логическом базисе 2И-НЕ).

Рисунок 1 – Схема логической функции в базисе 2И-НЕ

Таблица 1 – Таблица истинности логической функции| Х1 | Х2 | Х3 | F |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

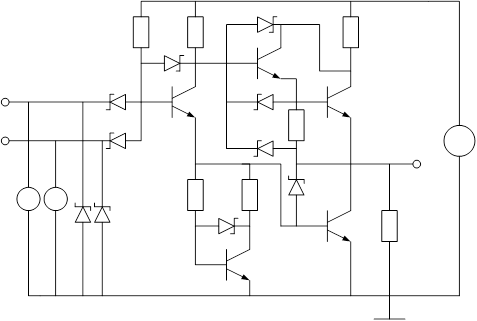

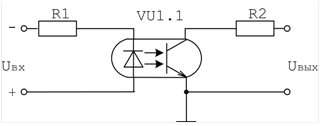

Рисунок 2 – Принципиальная электрическая схема логического базиса 2И-НЕ

Программа расчета блока логического базиса 2И-НЕ на языке программы PSpice.

* Комплексная работа по предмету ПИММС

*Студент группы 8033у

R1 3 12 20k

R2 4 12 8k

R3 5 6 1.5k

R4 7 5 3k

R5 11 10 4k

R6 12 8 120

R7 10 0 1E+9

D1 0 2 D_SH

D2 0 1 D_SH

D3 3 1 D_SH

D4 3 2 D_SH

D5 3 4 D_SH

D6 9 4 D_SH

D7 4 8 D_SH

D8 5 10 D_SH

D9 6 7 D_SH

Q1 4 3 5 Tran

Q2 7 6 0 Tran

Q3 9 4 11 Tran

Q4 8 9 10 Tran

Q5 10 5 0 Tran

.model Tran npn ()

.model D_SH D(IS=1E-11 TT=0)

VIN1 1 0 pulse(0 5 0.01us 0 0 0.03us 0.2us)

VIN2 2 0 5

VCC 11 0 5

.DC vin1 0 5 0.01

.tran 0.001us 0.07us

.probe

.END

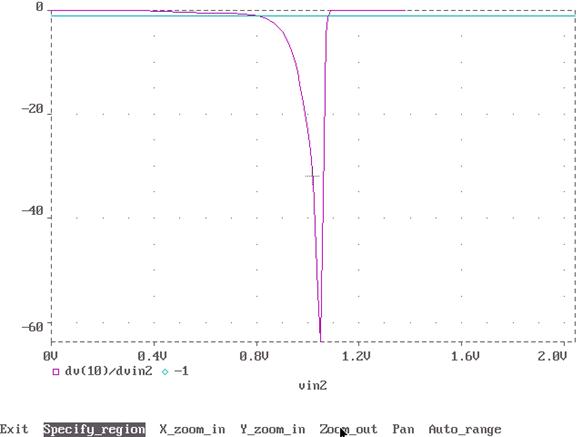

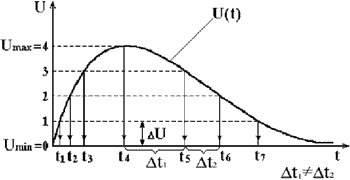

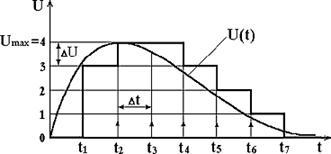

Рисунок 3 - Определение пороговых напряжений

Из графика видно, что U0пор=0,798 В и U1пор=1,08 В.

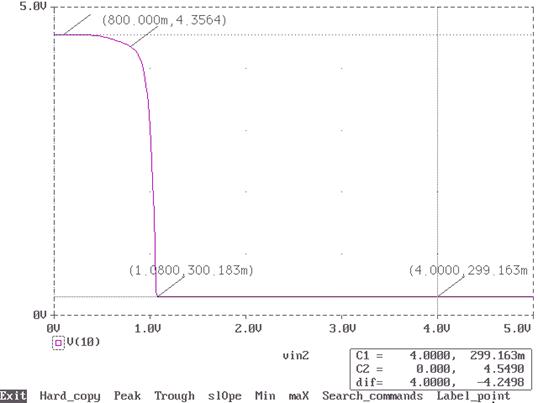

Рисунок 4 - Передаточная характеристика базового логического элемента 2И-НЕ

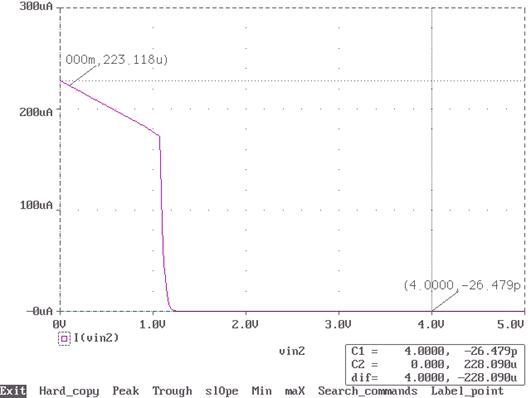

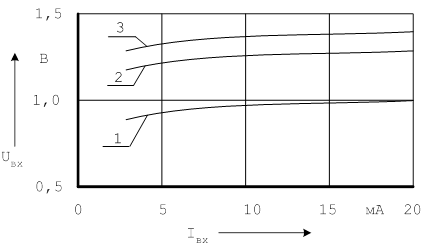

Рисунок 5 - ВАХ на входе логического элемента

Найдены значения I0=0.22 мА и I1=0.026 мкА.

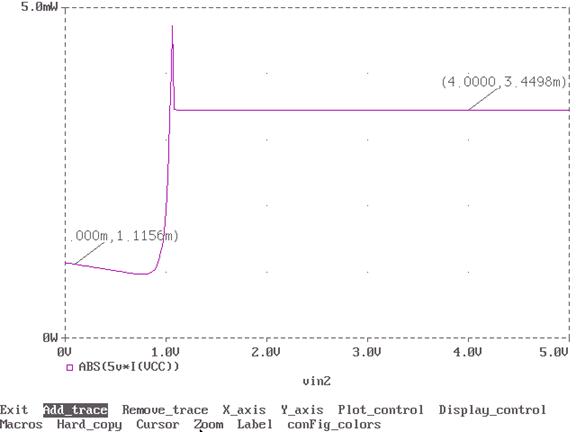

Рисунок 6- Мощность потребляемая логическим элементом

Из графика видно, что Р0=3.45 мВт и Р1=1.12 мВт.

Отсюда находим среднюю мощность:

Рср=( Р0+ Р1)/2=(3.45+1.12)/2=2.285 мВт

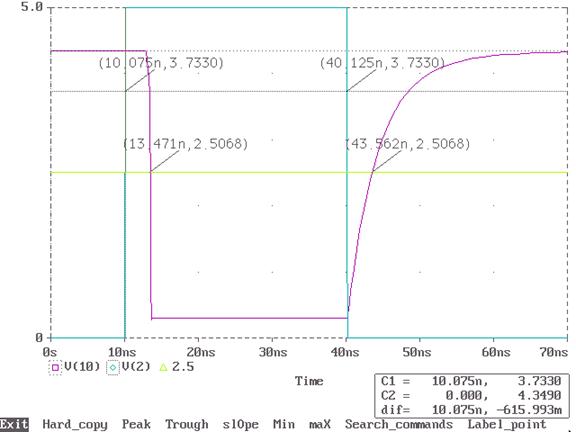

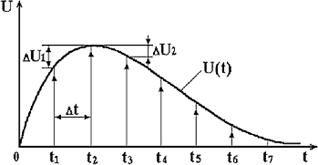

Из рисунка 7 находим t10=3.39 нсек и t01=3.44 нсек.

Находим общее время задержки:

tз=( t10+ t01)/2=(3.39+3.44)/2=3.415 нсек

Похожие работы

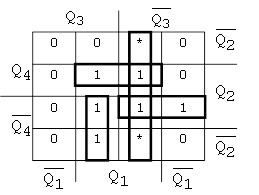

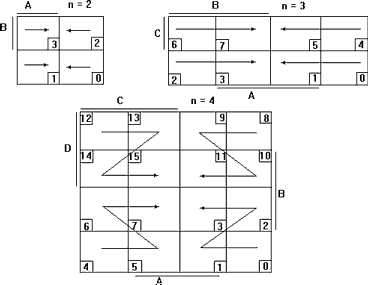

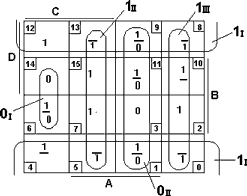

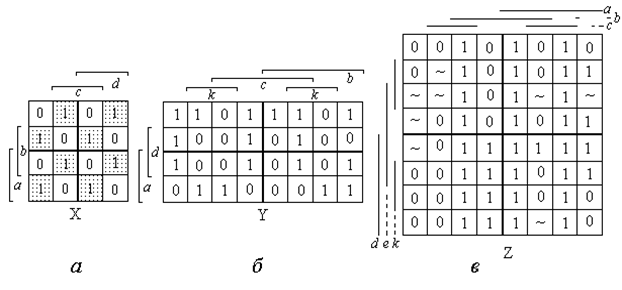

... состояний триггеров. Рис.3.5. Карта Карно, описывающая зависимость состояния входа D4 от состояний триггеров. Рис.3.6. Схема последовательностной части цифрового управляющего устройства Рис.3.7. 3.1.4 Синтез комбинационной части цифрового управляющего устройства 3.1.4.1Определение зависимости выходных сигналов цифрового управляющего устройства от входных сигналов и внутренних ...

... показана на рисунке 8.4 Величина резистора R выбирается из условия [12] 240 Ом < R < 1,5 кОм.(8.5) Рисунок 8.4 Период генерируемых импульсов (8.6) 9. ФУНКЦИОНАЛЬНЫЕ УСТРОЙСТВА КОМПЬЮТЕРНОЙ (ЦИФРОВОЙ) ЭЛЕКТРОНИКИ 9.1 Комбинационные цифровые устройства (КЦУ) Логические устройства, выходные сигналы которых однозначно определяются комбинацией входных логических ...

... Основная память доступна в любом режиме. В реальном режиме доступна только основная память (convenctention memory ). Этот 1МБ делится на следующие составные части: - верхние 384кБ – для вычислительной системы (A0000…FFFF). - Нижние 640кБ – для программ пользователя (00000…9FFFF). Виды адресного пространства: 1.Основная память – 1МБ (00000…FFFFF) 2. Область верхней памяти = 384кБ ...

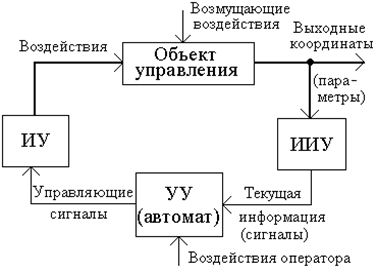

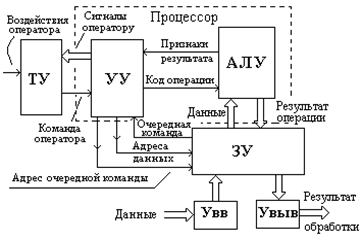

... правило, выполняется в виде одной «большой» ИМС. Схемотехника является частью микроэлектроники, предметом которой являются методы построения устройств различного назначения на микросхемах широкого применения. Предметом же цифровой схемотехники являются методы построения (проектирования) устройств только на цифровых ИМС. Особенностью цифровой схемотехники является широкое применение для описания ...

0 комментариев