Семейство процессоров ADSP-2100 представляет собой совокупность программируемых микропроцессоров с общей структурой, оптимизированную для обработки аналогового сигнала в цифровой форме, а так же для других прикладных целей. Различные микропроцессоры отличаются друг от друга преимущественно типом периферийных устройств, которые дополняют основную структуру. В различных членах семейства могут имеется память, таймер, последовательный и параллельный порты. Кроме того, процессоры ADSP-21msp58/59 включают аналоговый интерфейс для преобразования сигнала звуковой частоты.

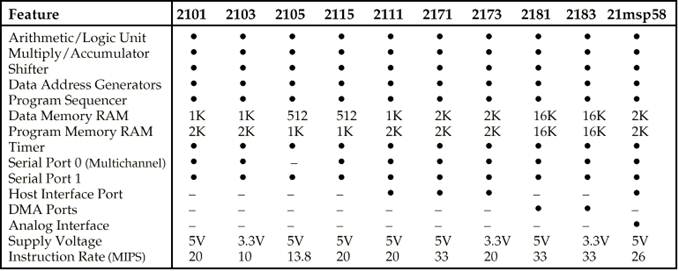

1.1. Функциональные модулиТаблица 1.1 показывает характеристики, которыми обладают отдельные члены семейства.

Таблица 1.1

Computational Units (вычислительный модуль) – каждый процессор семейства ADSP-2100 содержит три полнофункциональных независимых вычислительных модуля: arithmetic/logic unit (ALU) – арифметичиско-логический, multiplier/accumulator (MAC) – накопитель, barrel shifter – сдвиговый расширитель.Все модули оперируют с 16-разрядными словами, а также обеспечивают аппаратную поддержку мультиточности.

Data Address Generators & Program Sequencer (генераторы адресов данных и программа sequencer) – два отдельных генератора адресов обеспечивают адреса для встроенной и внешней памяти. Сдвоенные генераторы адресов данных позволяют процессору генерировать адреса для двух выборок операнда одновременно, что максимизирует производительность.

Memory (память) – в семействе ADSP-2100 применяется архитектура памяти, в которой данные хранятся в секции данных, а в секции программ хранятся как данные так и команды. Все процессоры семейства имеют оперативную память состоящую и этих двух сегментов. Быстродействие внутренней памяти позволяет процессору выбирать два операнда (один из области данных, другой из области программ) в течении одного цикла.

Serial Ports (последовательные порты) – обеспечивают последовательный интерфейс связи с аппаратными средствами, предназначенными для сжатия, хранения и обработки данных. Интерфейс совместим с большим числом известных устройств. Каждый порт может использовать как внутренний таймер, так и внешний. Последовательный порт 0 имеет многоканальные возможности.

Timer – 8-разрядный программируемый таймер/счетчик обеспечивает периодическую генерацию прерываний.

Host Interface Port (главный связной порт) – обеспечивает прямое соединение с главным процессором ЭВМ. Например Motorola 68000, Intel 8051 или другой процессор семейства ADSP-2100 могут быть легко соединены с главным интерфейсом.

DMA Ports (порты DMA) – в ADSP-2181 внутренний (IDMA) и байтовый (BDMA) DMA порты обеспечивают эффективную передачу данных из внутренней памяти и в неё. IDMA порт имеет мультиплексный адрес и 16-битную шину данных. IDMA порт полностью асинхронный данные в него могут записываться, в то время когда ADSP-2181 полностью занят.

Analog Interface (аналоговый интерфейс) – процессоры ADSP-21msp58/59 имеют встроенную схему для цифровой обработки аналогового сигнала. Эта схема содержит АЦП (ADC) и ЦАП (DAC), аналоговые и цифровые фильтры и параллельный интерфейс связи с ядром процессора.

Архитектура семейства ADSP-2100 приспособлена к выполнению задач с помощью цифрового сигнального процессора и построена таким образом, что устройства за один такт могут выполнять следующие действия:

· генерировать следующий адрес программы;

· выбирать следующую команду;

· выполнять один или два шага программы;

· модифицировать один или два указателя адреса данных;

· выполнять вычисление.

В этом же такте процессоры, которые имеют релевантные модули могут:

· принимать и/или передавать данные через последовательный порт;

· принимать и/или передавать данные через главный порт интерфейса;

· принимать и/или передавать данные через DMA порты;

· принимать и/или передавать данные через аналоговый интерфейс.

1.2. Системный интерфейс и интерфейс памятиВ каждом процессоре семейства ADSP-2100 четыре внутренних шины соединяют внутреннюю память с другими функциональными модулями:

- шина адреса;

- шина данных;

- шина памяти программ;

- шина памяти данных.

Внешние устройства могут получать контроль над шинами посредством сигналов предоставления (BR,BG). Процессоры ADSP-2100 могут работать в то время когда шины предоставлены другому устройству, пока не требуется операции с внешней памятью.

Схема начальной загрузки дает возможность автоматической загрузки внутренней памяти после того как ее содержимое было стерто. Это можно осуществлять с помощью интерфейса памяти из EPROM, из главного компьютера, посредством главного порта интерфейса, а так же через BDMA порт процессора 2181. Программы могут загружаться без применения каких-либо дополнительных аппаратных средств.

1.3. Система командПроцессоры семейства ADSP-2100 используют единую систему команд для совместимости с устройствами с более высокой интеграцией. Микропроцессоры ADSP-2171, ADSP-2181 и ADSP-21msp58/59 имеют ряд дополнительных команд. Система команд позволяет выполнять мультифункциональные команды за один такт процессора, с другой стороны каждая команда может быть выполнена отдельно в своем такте. Ассемблер имеет алгебраический синтаксис, для повышения удобочитаемости легкости кодирования.

1.4. Эффективность сигнального процессораСигнальный процессор должен быть не только очень быстродействующим, но удовлетворять некоторым требованиям в следующих областях:

· Быстрая и гибкая арифметика – архитектура процессоров ADSP-2100 позволяет в одном производить такие операции, как умножение, умножение с накоплением, произвольное смещение, а так же ряд стандартных арифметических и логических операций в одном цикле процессора.

· Расширенный динамический диапазон – 40-разрядный аккумулятор имеет восемь резервных бит защиты от переполнения при последовательном суммировании, которые гарантируют, что потери данных быть не может.

· Выборка двух операндов за один цикл – при расширенном суммировании на каждом цикле процессора необходимо два операнда. Все члены семейства ADSP-2100 способны поддерживать обработку данных с двумя операндами, сохранены ли данные в памяти или нет.

· Аппаратные циклические буферы – большой класс алгоритмов обработки цифро-аналоговых сигналов, включая цифровые фильтры требуют наличия циклических буферов. Архитектура семейства ADSP-2100 имеет аппаратные средства для обработки указателя адреса wraparound, что упрощает реализацию круговых буферов.

· Переход по нулю – повторяющиеся алгоритмы наиболее логично выражать через циклы. Программа Sequenser ADSP-2100 поддерживает работу с циклическим кодом с нулем на верху, в объединении со структурой clearest это повышает эффективность системы. Также нет препядствий для работы с условными переходами.

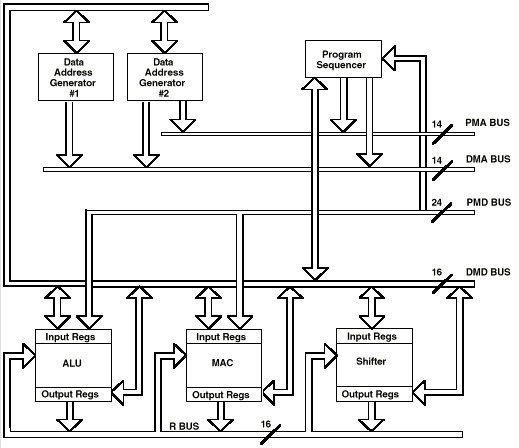

2. Основная архитектураВ этом разделе описывается основная архитектура процессоров семейства ADSP-2100, схема которой приведена на рис. 2.1.

2.1. Вычислительные модулиКак уже говорилось выше каждый процессор семейства ADSP-2100 содержит три независимых вычислительных модуля:

- арифметико-логический (ALU);

- умножение с накоплением (MAC);

- расширитель (shiffter).

Эти устройства работают с 16-разрядными данными и обеспечивают аппаратную поддержку мультиточности.

ALU выполняет ряд стандартных арифметических и логических комманд в дополнене к примитивам деления. MAC выполняет одноцикловые операции умножения, умножения/сложения, умножения/вычитания. Shiffter осуществляет логические и арифметические сдвиги, нормализацию, денормализацию и операцию получения порядка, атак же управление форматом данных,разрешая работу с плавоющей точкой. Вычислительные модули размещаются последовательно друг за другом, таким образом чтобы выход одного мог стать входом другого в следующем цикле. Результаты работы модулей собираются на 16-разрядную R-шину.

Все три модуля содержат входные и выходные регистры, которые доступны черех 16-разрядную DMD-шину. Комманда, выполняемые в модулях, берут в качестве операндов данные находящиеся в регистрах ввода и после выполнения записывают результат в регистры вывода. Регистры являются как бы промежуточным хранилищем между памятью и вычислительной схемой. R-шина позволяет результату одного вычисления стать операндом к другой операции. Это позволяет сэкономить время обходясь без лишних пересылок модуль-память.

|

2.2. Генераторы адресов данных и программа sequencer

Два специализированных генератора адресов данных (DAGs) и мощная программа sequencer гарантируют эффективное использование вычислительных модулей. DAGs обеспечивают адреса памяти, когда необходимо поместить данные из памяти в регистры ввода вычислительных модулей, либо сохранить в результат из выхоных регистров. Каждый DAG отвечает за четыре указателя адреса. Если указатель используется для косвенной адресации то измениятся значение некоторого регистра. С двумя генераторами процессор может выдавать два адреса одновременно для выборки из памяти двух операндов.

Для автоматической адресации модуля круговых буферов значение длины операнда может быть связано с каждым указателем. (Круговая буферная особенность также используется последовательными портами для автоматической передачи данных).

DAG1 обеспечивает адреса только для данных, DAG2 – для данных и программ. Когда в регистре состояния (MSTAT) установлен соответствующий бит режима, адрес вывода DAG1 прежде чем попасть на шину адреса инвертируется. Эта особенность облегчает работу в двоичной системе.

Программа Sequenсer обеспечивает последовательность команд и адресацию памяти программы. Sequencer управляется регистром команд, который указывает на команду, которая в данный момент выполняется. Выбранные команды записываются в регистр команд за один такт процессора и выполняются в течении следующего. Чтобы уменьшить количество циклов, sequencer поддерживает работу с условными переходами.

2.3. ШиныПроцессоры семейства имеют пять внутренних шин. Шины адреса программы (PMA) и адреса данных (DMA) связаны с адресами памяти данных и программы. Шина данных программы (PMD) и шина данных (DMD) используются для передачи информации связанной с областями памяти. Шины мультиплексированы в одну внешнюю шину адреса и одну внешнюю шину данных. R-шина предназначена для передачи промежуточных результатов непосредственно между вычислительными модулями.

Адресная шина PMA шириной 14 бит обеспечивает достум к 16Кбайтам смешанной системы команд и данных. 24-разрядная шина PMD предназначена для работы с 24-битными командами.

Адресная шина DMA шириной 14 бит, обеспечивает прямой доступ к 16Кбайтам области данных. 16-разрядная шина DMD предназначена для внутренних пересылок между любыми регистрами процессора и регистров с памятью в одиночном цикле. Адрес памяти данных исходит из двух источников: абсолютное значение, определенное в системе команд (прямая адресация) или вывод данных адресует генератор (косвенная адресация). Воспользоваться данными из области команд можно лишь с помощью косвенной адресации.

Шина данных памяти программы (PMD) предназначена для передачи данных в вычислительные модули и считывания результата вычислений через PMD-DMD модуль обмена. Этот модуль позволяет передавать данные от одной шины к другой. Он имеет аппаратные средства для перехода от 8-разрядной шины к другой.

3. Внутренние переферийные устройства

Этот раздел описывает дополнительные функциональные модули, которые включены в различные процессоры ADSP-2100 семейства.

3.1. Последовательные порты

Большенство процессоров семейства ADSP-2100 имеют по два последовательных двунаправленных порта. Порты – синхронные и используют кадровые сигналы для контроля за приемом-передачей данных. Каждый порт имеет внутренний генератор частоты, но в то же время может использовать внешний генератор. Сигналы синхронизации могут вырабатываться как самим портом, так и внешним устройством. Длина кадра обмена может меняться от трех до шести бит. Последовательный порт SPRT0 имеет многоканальные возможности и пзволяет обмен данными произвольной длины от 24 до 32 байт. Второй порт SPORT1 может быть сконфигурирован с помощью внешних прерываний IRQ0 и IRQ1.

3.2. ТаймерРегистр счета (16-разрядов) определяет время генерации прерываний, прерывание вырабатывается когда значение регистра равно нулю.

3.3. Главный интерфейсный порт (HIP)Главный интерфейсный порт – параллельный порт ввода-вывода осуществляет прямое соединение с процессором. Через него производится обмен между ADSP-2100 и памятью главной ЭВМ. HIP состоит из регистров, через которые ADSP-2100 и главный процессор обмениваются информацией о состоянии и данными. HIP может быть сконфигурирован следующим образом:

- 8-разрядная или 16-разрядная шина;

- мультиплексная шина данных/шина адреса или отдельно шина данных и шина адреса;

- чтение стробирующих сигналов READ/WRITE.

3.4. DMA порты (ADSP-2181)ADSP-2181 два DMA порта внутренний (IDMA) порт и байтовый (BDMA). IDMA порт обеспечивает эффективную связь между главной системой и сигнальным процессором. Он используется для связи с внутренней памятью программы и памятью данных за один такт процессора. IDMA порт имеет 16-разрядный мультиплексный адрес и шину данных. IDMA порт полностью ассинхронный и может работать даже когда процессор полностью занят.

Байт памяти контроллера DMA позволяет загружать и сохранять комманды программ и данные, находящиеся в памяти. BDMA схема способна обращаться к ячейке памяти, в то время как процессор работает в обычном режиме, используя только один такт процессора для передачи 8-,16- или 24-разрядных данных.

3.5. Аналоговый интерфейсВходной аналоговый интерфейс состоит из входных усилителей и 16-разрядного аналогоцифрового преобразователя (ADC). Аналогично на выходе находится цифроаналоговый преобразователь и выходной дифференциальный усилитель.

4. ADSP-2100 - средства разработкиСемейство ADSP-2100 сопровождается полным набором программного обеспечения и аппартных средств для разработки. Система средств разработки для ADSP-2100 включает утилиты программного обеспечения для разработки программы и EZ-комплект для отладки аппаратных средств.

Программное обеспечение включает:

· System Builder (системный составитель программы) – определяет структуру аппаратной системы. Он описывает количество внешней памяти и доступные порты ввода/вывода.

· Assembler (ассемблер) – транслирует исходный код и модули данных и обеспечивает синтаксис высокого уровня. В дополнение к полной диагностике системы Ассемблер обеспечивает макро обработку: включение файлов и модульную обработку кода.

· Linker (компановщик) – связывает раздельные модули программы, получая связанный код, и направляет его к аппаратным средствам, описанным с помощью System Builder.

· Simulator (тренажер) – выполняет интерактивное моделирование аппаратной конфигурации описанной System Builder. Он отмечает запрещенные команды и поддерживает полную символическую трансляцию и дизассемблирование.

· PROM Splitter – этот модуль по выходным данным компановщика генерирует код совместимый с форматом памяти PROM.

· C compiler (С транслятор) – читает исходники написаные на С в формате ANSI и код на языке семейства ADSP-2100, готовый к ассемблированию.

Вычислительные модули

1. Краткое описание 1.1. Двоичные строкиДвоичные строки - самое простое представление чисел в процессорах семейства ADSP-2100. Этот формат, например, используют элементарные логические функции: NOT, OR, AND, XOR и т.д. Вычислительный модуль ALU обрабатывает эти числа ввиде двоичных последовательностей не привлекая возможности работы с плавающей точкой и знаковым разрядом.

1.2. Беззнаковые числаПод двоичными числами без знака понимаются положительные числа. Диапазон их представления в процессоре в два раза больше чем у чисел со знаком. Числа большой точности обрабатываются как беззнаковые.

1.3. Числа со знаком: двойное дополнениеРасматривая арифметику семейства ADSP-2100 знаковые числа можно отнести к числам с двойным дополнением. Дольшенства операций процессора поддерживают работу с двойным дополнением. Процессоры семейства ADSP-2100 не поддерживают работу с остатками и BCD-форматом.

1.4. Дробное представление: 1.15Арифметики ADSP-2100 приспособленна для работы с числами в дробном двочном формате, называемом 1.15. В этом формате имеется один знаковый разряд (MSB) и пятнадцать дробных битов.

Далее представленны весовые значения битов в формате 1.15:

–20 2 –1 2 –2 2 –3 2 –4 2 –5 2 –6 2 –7 2 –8 2 –9 2 –10 2 –11 2 –12 2 –13 2 –14 2 –15

| Числа в формате 1.15 | Десятичный эквивалент |

| 0x0001 0x7FFF 0xFFFF 0x8000 | 0.000031 0.999969 –0.000031 –1.000000 |

Все комманды ALU обрабатывают операнды, как двоичные 16-разрядные последовательности. Биты состояния: AV- переполнение, AN – знак.

Логика бита переполнения основана на арифметике двойного дополнения. Например при сложении двух положительных чисел получается положительный результат, но может повлечь за собой переполнение. При сложении двух чисел с разными знаками результат может быть как положительным так и отрицательным, но переполнение в этом случае невозможно.

Логика бита переноса основана на арифметике чисел без знака. Он устанавливается если перенос сгенерирован 16-ым битом (MSB).

1.6. Арифметика MACОперациив модуле MAC производятся над числами, представленными ввиде двоиных последовательностей и результет выдается в том же виде.

Процессоры семейства ADSP-2100 поддерживают два режима корректировки формата: дробный режим – для дробных операндов (формат 1.15) и целочисленный режим для целых чисел формата 16.0.

Когда процессор умножает два операнда в формате 1.15 в результате получается число 2.30 (два знаковых и 30 дробных разряда). В дробном режиме МАС автоматически сдвигает результат на один бит влево перед пересылкой его в регистр результата (MR). Этим сдвигом результат приводится к виду 1.31, который может быть округлед до формата 1.15.

В целочисленном режиме сдвига влево не происходит. Напрмер при умножении операндов 16.0 результат представляется ввиде 32.0. Сдвиг влево в этом случае не нужен, т.к. он изменит числовое представление результата.

1.7. РезюмеТаблица 1.1 обобщает некоторые арифметические характеристики процессоров семейства ADSP-2100.

Таблица 1.1

| Операции | Арифметические форматы | |

| Операнды | Результат | |

| ALU | ||

| Сложение | Знаковые или без знака | Установка флагов |

| Вычитание | Знаковые или без знака | Установка флагов |

| Логические операции | Двоичные строки | Тот же, что и операнды |

| Деление | Явно знаковые/без знака | Тот же, что и операнды |

| Переполнение ALU | Знаковые | Тот же, что и операнды |

| Бит коррекции ALU | 16-разрядные без знака | Тот же, что и операнды |

| Насыщение ALU | Знаковые | Тот же, что и операнды |

| MAC (дроб.) | ||

| Умножение (Р) | 1.15 Явно знаковые/без знака | 32 разряда (2.30) |

| Умножение (MR) | 1.15 Явно знаковые/без знака | 2.30 сдвинутый к 1.31 |

| Умножение с накоплением | 1.15 Явно знаковые/без знака | 2.30 сдвинутый к 1.31 |

| Умножение с вычитанием | 1.15 Явно знаковые/без знака | 2.30 сдвинутый к 1.31 |

| Насыщение МАС | Знаковые | Тот же, что и операнды |

| МАС(цел.) | ||

| Умножение (Р) | 1.15 Явно знаковые/без знака | 32 разряда (2.30) |

| Умножение (MR) | 16.0 Явно знаковые/без знака | 32.0 без сдвига |

| Умножение с накоплением | 16.0 Явно знаковые/без знака | 32.0 без сдвига |

| Умножение с вычитанием | 16.0 Явно знаковые/без знака | 32.0 без сдвига |

| Насыщение МАС | Знаковые | Тот же, что и операнды |

| Shifter | ||

| Логические сдвиги | Баз знака/двоичные строки | Тот же, что и операнды |

| Арифметические сдвиги | Знаковые | Тот же, что и операнды |

| Определение порядка | Знаковые | Тот же, что и операнды |

Модуль ALU предоставляет набор стандартных арифметических и логических функций. Арифметические функции: сложение, вычитание, отрицание, инкремент, декремент и модуль.Они дополненны двумя примитивами деления, с помощью которых возможна реализация цикла многократного деления. Логические: OR, AND, XOR (исключающее ИЛИ) и NOT.

2.1. Блок-схема ALUНа рисунке 2.1 показана структурная схема вычислительного модуля ALU.

|

ALU – это 16-разрядное устройство с двумя 16-разрядными портами ввода данных X и Y,и одним портом вывода - R . ALU генерирует шесть сигналов состояния: ноль (AZ), негатив (AN), перенос (AC), переполнение (AV), знак (AS) и quotient (AQ). В конце каждого цикла эти сигналы сохраняются в регистре состояния процессора (ASTAT).

Порт ввода X может принимать данные из двух источников: из регистра АX и с шины результатов R. R-шина соединяет выходные регистры всех вычислительных модулей. Регистр AX предназначен только для порта X и состоит из двух частей AX0 и AX1. Эти регистры подключенны к DMD-шине. Система команд позволяет чтение регистра AX и с помощью PMD-шины, но прямого соединения с ней нет, эта операция использует модуль DMD-PMD обмена. Выводы регистров AX0 и AX1 реализованы таким образом, чтобы один обеспечивал ввод в ALU, а другой в это время управлял DMD-шиной.

Порт ввода Y также принимает данные из двух источников: из регистра AY и регистра обратной связи ALU – AF. Регистр AY привязан к порту Y и состои из двух регистров AY0 и AY1. Эти регистры даступны для чтения и записи с DMD-шины и перезаписываемы с PMD-шины. Система комманд позволяет читать регистры AY0 и AY1 с помощью PMD-шины, но то же с использованием DMD-PMD модуля. Выводы ругистров AY0 и AY1 реализованы аналогично регистрам AX0 и AX1.

Выход ALU подключен к выходному регистру результата AR и через регистр обратной связи AF на вход. AF – внутренний регистр ALU, который позволяет результату вычисления использоваться в качестве следующего операнда. Регистр AR имеет выход на DMD- и R-шины. В системе комманд предусмотрена возможность чтения регистра AR посредством PMD-шины аналогично двум предыдущим случаям.

Любой из регистров ALU доступен для записи и чтения в течении цикла процессора (для чтения в начале цикла, для чтения - в конце). Таким образом, новое значение, записанное в конце одного цикла, может быть прочитанно лишь в начале следующего. Это позволяет входным регистрам записать в ALU опренд в начале цикла и считать следующий в конце того же цикла. Это так же позволяет сохранить содержимое регистра результата в памяти и прооперировать со следующим результатом в одном цикле.

ALU имеет двойные банки регистров AX, AY, AF и AR (на рис.2.1 это показано тенями). Но в один момент времени доступен только один банк. Доплнительный банк может быть активизирован для чрезвычайно быстрого контекстного переключения. В этом случае новая задача, подобно подпрограмме обработке прерывания, может выполнияться без сохранения текущих данных в памяти.

Выбор главного или альтернативного банка регистров определяется битом 0 регистра режимоа процессора MSTAT. Если этот бит – 0, то выбран главный банк, если – 1, то дополнительный.

2.2. Стандартные функцииСтандартные функции ALU перечисленны в таблице 2.1.

Таблица 2.1

| Функция | Назначение |

| R= X+Y | Сложение операндов X и Y |

| R= X+Y+CI | Сложение операндов X и Y и бита коррекции |

| R= X-Y | Вычитание операндов X из Y |

| R= X-Y+CI-1 | Вычитание операндов X из Y с заемом |

| R= -X | Инверсия X |

| R= -Y | Инверсия Y |

| R= X+1 | Инкремент X |

| R= Y+1 | Инкремент Y |

| R= X-1 | Декремент X |

| R= Y-1 | Декремент Y |

| R= PASS X | Операнд X не изменяет результата |

| R= PASS Y | Операнд Y не изменяет результата |

| R= 0 | Очистка результата |

| R= ABS X | Модуль X |

| R= X AND Y | Логическое умножение операндов X и Y |

| R= X OR Y | Логическое сложение опреандов X и Y |

| R= X XOR Y | Исключающее ИЛИ операндов X и Y |

| R= NOT X | Отрицание X |

| R= NOT Y | Отрицение Y |

Регистры ввода ALU перечисленны ниже.

Регистры для порта X: AX0, AX1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для порта Y: AY0, AY1, AF.

Регистры для порта R: AR, AF.

Регистры MR0, MR1, MR2 являются регистрами результатов модуля MAC, а SR0, SR1 – модуля Shifter.

2.4. Возможность мультиточностиОперации мультиточности в ALU связаны с сигналом carry-in и битом переноса AC. Операция сложение с переносом предназначена для сложения старших частей мультиточных чисел, также как, вычитание с заемом – для их вычитания.

2.5. Режим насыщения ALUРегистр AR имеет режим работы - насыщение, в котором он устанавливается в минимальное отрицательное значение или максимальное положительное, если операция заканчивается переполнением. Эта функция регистра AR становится возможной при установке 3 регистра MSTAT.

Таблица 2.2.

| Переполнение (AV) | Carry (AC) | Содержимое AR |

| 0 | 0 | Результат на выходе ALU |

| 0 | 1 | Результат на выходе ALU |

| 1 | 0 | 0111111111111111 (положит.) |

| 1 | 1 | 1000000000000000 (отриц.) |

Режим блокировки переполнения разрешается при установки бита 2 регистра MSTAT. В этом режиме при переполнении бит AV устанавливается и при последующих операциях остается в этом состоянии, таким образом следующее переполнение уже не генерируется. Бит состояния AV можно очистить непосредственно с DMD-шины.

2.7. ДелениеALU поддерживает методы деления. Деление осуществляется путем сложения и циклического сдвига с помощью двух специальных примитивов. Делить можно знаковые и без знаковые числа, однако делитель и делимое должны быть одного типа.

Обычная точность деления (32-разрядное делимое, 16-разрядный делитель, 16-разрядный остаток) реализуется за 16 циклов. Может быть получена большая или меньшая точность остатка. Делитель может быть сохранен в регистре AX0, AX1 или в любом регистре результатов R. Старший байт знакового делителя должен находиться либо в регистре AY1, либо в AF, без знакового – в AF. Младший байт делителя любого типа должен находиться в AY0. Остаток после деления будет записан в регистр AY0.

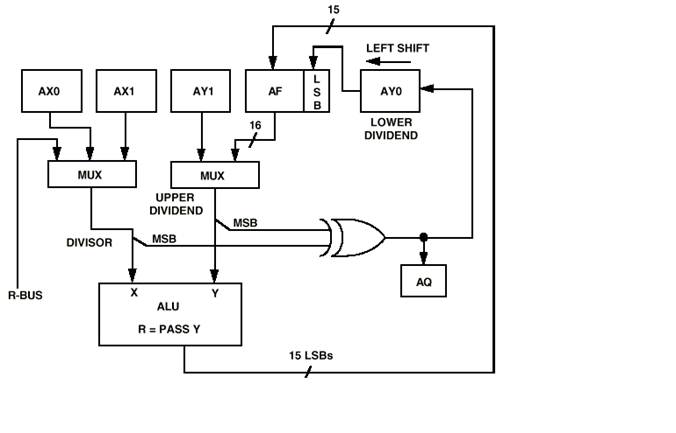

Первый из двух примитивов - это команда «деление-знак» (DIVS), преназначена для деления чисел со знаком. Она вычисляет знаковый бит остатка выполняя операцию исключающее-ИЛИ для знаковых разрядов делителя и делимого. Регистр AY0 сдвигается на одну позицию таким образом, чтобы знаковый разряд переместился в позицию LSB. Вычисленный зныковый разряд сохраняется в бит AQ регистра состояния. Структура операции DIVS показанна на рисунке 2.2.

При делении чисел без знака операция DIVS не применяется. В этом случае бит AQ устанавливается в 0 вручную. Он показывает, что остаток должен быть положительным.

|

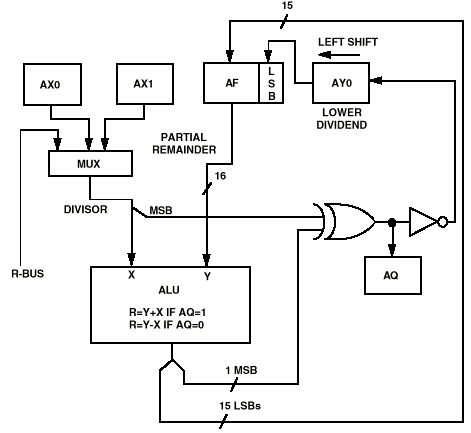

Второй примитив из раздела деления – это команда DIVQ, которая выполняется неоднократно и генерирует по одному биту частного. При простой точности деления чисел без знака команда DIVQ выполняется 16 раз, для такой же точности деления чисел со знаком операция выполняется 15 раз после вычисления знакового разряда с помощью команды DIVS. DIVQ сдвигает регистр AY0 влево на один разряд так, чтобы новый бит частного оказался в позиции LSB. Состояние бита AQ, которое генерируется на предыдущей операции, определяет операцию ALU для вычисления частичного результата. Если AQ=1, то ALU добавляет делитель к частичному результату в AF. Если AQ=0, то ALU вычитает делитель из частичного результата в AF. Так же как и в операции DIVS ALU выводит результат в регистр AF. Операция DIVQ проиллюстрирована на рис.2.3.

Второй примитив из раздела деления – это команда DIVQ, которая выполняется неоднократно и генерирует по одному биту частного. При простой точности деления чисел без знака команда DIVQ выполняется 16 раз, для такой же точности деления чисел со знаком операция выполняется 15 раз после вычисления знакового разряда с помощью команды DIVS. DIVQ сдвигает регистр AY0 влево на один разряд так, чтобы новый бит частного оказался в позиции LSB. Состояние бита AQ, которое генерируется на предыдущей операции, определяет операцию ALU для вычисления частичного результата. Если AQ=1, то ALU добавляет делитель к частичному результату в AF. Если AQ=0, то ALU вычитает делитель из частичного результата в AF. Так же как и в операции DIVS ALU выводит результат в регистр AF. Операция DIVQ проиллюстрирована на рис.2.3.

|

|

Иногда необходимо некоторое изменение формата делимого и делителя. Например, если оба операнда знаковые и дробные (делимое в формате 1.31, а делитель – 1.15), то результат запишется в формате 1.15, т.о. для правильного результата необходимо, чтобы делимое было меньше делителя.

Чтобы разделить два целых числа (делимое в формате 32.1, а делитель – 16), необходимо перед делением привести делимое к формату 31.1, т.е. сдвинуть его влево на один разряд.

Делимое: BBBBB.BBBBBBBBBBBBBBBBBBBBBBBBBBB

NL NR

Делитель: BB.BBBBBBBBBBBBBB

DL DR

Частное: BBBB.BBBBBBBBBBBB

(NL–DL+1) (NR–DR–1)

Алгоритм переполняется, если результат не представляется в формате частного, как вычислено выше и когда делитель равен нулю или меньше делимого.

2.8. Регистр состояния ALUНазначение битов регистра ASTAT описано ниже:

· AZ – ZERO - логическое сложение всех битов регистра результатов ALU. Устанавливается в 1, если результат операции равен нулю.

· AN – NEGATIV - знаковый разряд результата ALU. Единица, если результат отрицательный.

· AV – OVERFLOW – устанавливается в единицу, если происходит переполнение ALU.

· AC – CARRY – бит переноса.

· AS – SIGN – знаковый разряд входного X-порта ALU. Необходим только для команды ABS.

· AQ – QUOTIENT – бит частного. Генерируется только командами DIVS и DIVQ.

3. Вычислительный модуль умножения с накоплением (MAC)Вычислительный модуль МАС обеспечивает быстрое умножение, умножение с добавлением, умножение с вычитанием, функции насыщения и очистка в ноль. Функция обратной связи позволяет части результата в одном цикле быть одним из сомножителей в следующем.

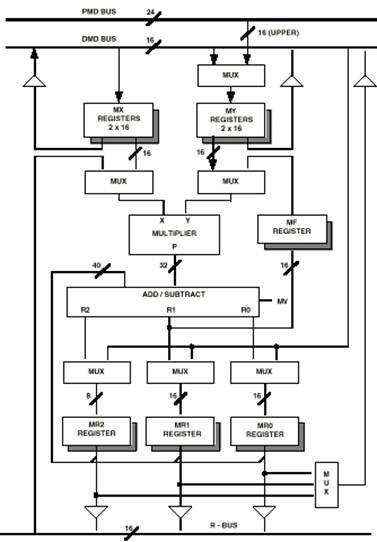

3.1. Описание блок-схемы МАСНа рисунке 3.1. показана блок-схема вычислительного модуля умножения с накоплением.

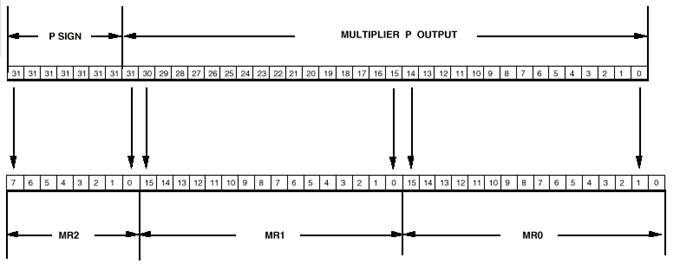

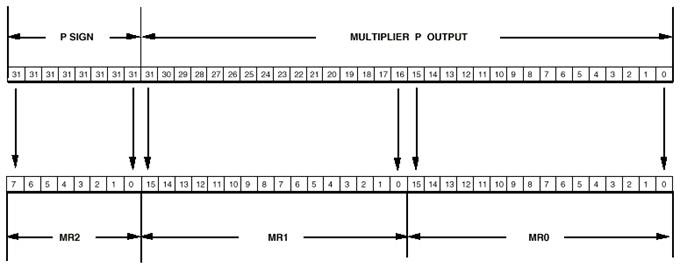

МАС имеет два входных 16-разрядных порта X и Y и 32-разрядный порт вывода результата P. 32-разрядный результат поступает в 40-разрядный блок сложения/вычитания, который либо прибавляет, либо вычитает текущий результат из регистра результата МАС (MR), либо передает текущий результат непосредственно в MR (регистр MR имеет 40 разрядов). Фактически регистр MR состоит из трех (MR0 и MR1 – 16-разрядные и MR2 – 8-рахрядный) регистров.

|

Блок сложения/вычитания имеет более 32 разрядов затем, чтобы учесть промежуточные переполнения в ряде операции умножения с накоплением. Бит признака МV (переполнение) устанавливается в единицу, если значение аккумулятора превышает 32 разряда, т.е. в старшей части регистра результата MR есть девять значащих битов (без знака).

Регистры ввода-вывода подобны регистрам ALU.

Порт Х может принимать данные из регистра MX или из любого другого регистра на R-шине (результата). R-шина соединяет выходные регистры всех вычислительных модулей, для непосредственного использования результатов вычислений в качестве входных операндов. Регистр MX состоит из двух: MX0 и MX1. Они читаются и записываются с DMD-шины. Выводы регистров MX0 и MX1 устроены таким образом, что один поставляет множитель в блок умножения, а другой управляет DMD-шиной.

Порт Y принимает данные из регистра MY или регистра обратной связи MF. MY так же разбит на два регистра (MY0 и MY1), доступ к которым осуществляется с DMD-шины и возможна запись в низ с PMD-шины. Система команд предусматривает чтение этих регистров с помощью PMD-шины, но прямого доступа для этой операции нет, в этом случае используется модуль DMD-PMD обмена. Выводы регистра MY устроены аналогично MX.

Результат умножения поступает либо в блок сложения/вычитания, либо в регистры MY или MF. Регистр обратной связи MF позволяет 16-31-разрядному результату вычисления в предыдущем цикле становится операндом умножения на входе Y, в следующем. 40-разрядный регистр MR разделен на три секции (MR0, MR1, MR2). Содержимое любой из них может быть выведено на DMD- или R-шину и записано с DMD-шины.

Любой из регистров МАС может читаться и записываться в одном цикле (чтение в начале цикла, запись - в конце). Прочитанное содержимое регистра в начале одного цикла записано в конце предыдущего, следовательно новое значение регистра может быть прочитано только в течении следующего цикла. Это позволяет входному порту предоставлять операнд для МАС в начале цикла и оперировать со следующим значением из памяти в конце того же цикла. Это относится и к выходному регистру.

Регистры MR, MF, MX, MY продублированы во вторичном банке (на рис.3.1. он показан на заднем плане). Одновременно доступен лишь один из банков. Дополнительный банк регистраторов может быть активизирован для чрезвычайно быстрого контекстного переключения. Таким образом новая задача, типа подпрограммы обработки прерывания, может выполняться без сохранения текущих данных в памяти.

Выбор первичного или дополнительного банка регистров определяется установкой нулевого бита в регистре MSTAT состояний процессора. Если этот бит установлен в 0, то выбран первичный банк.

3.2. Операции МАСВ этом разделе описываются операции вычислительного модуля МАС, входные форматы данных, обработка переполнения и насыщения.

3.2.1. Стандартные функцииНабор стандартных операций перечислен в таблице 3.1.

Таблица 3.1

| Название | Назначение |

| X×Y | Умножение X на Y |

| MR+X×Y | Умножение и сложение с MR |

| MR-X×Y | Умножение и вычитание из MR |

| 0 | Очистка MR |

ADSP-2100 обеспечивают два режима работы операции умножения с накоплением: работы с дробными числами (1.15) и работа с целыми числами (16.0).

В дробном режиме выходной регистр P корректирует формат, т.е. прежде чем добавить значение в MR оно сдвигается на один разряд влево. Таким образом, бит 31 регистра P запишется в бит 32 регистра MR, а 0-ой бит – в первый. В позицию LSB, при этом записывается ноль. На рисунке 3.2. показан дробный формат работы модуля умножения.

|

В целочисленном формате (рис.3.3) регистр P не сдвигается прежде чем прибавиться к MR.

|

Выбор режима осуществляется установкой 4 бита регистра MSTAT процессора. Если этот бит в 1, то выбран целочисленный режим. В любом формате блок умножения формирует 32-разрядный результат и передает его в блок сложения/вычитания, где получается конечное значение операции, которое записывается в MR.

3.2.2. Входные форматыДля облегчения умножения входные операнды могут находится в любых форматах. Входные форматы определяются, как часть команды и выбираются динамически при обращению к блоку умножения.

1. Знаковый ´ знаковый – используется при умножении двух знаковых чисел простой точности или двух старших частей знаковых чисел двойной точности.

2. Без знака ´ знаковый (знаковый ´ без знака) - используется при умножении верхней части знакового числа на нижнюю часть другого или для умножения знакового числа простой точности с числом той же точности без знака.

3. Без знака ´ без знака – используется при умножении чисел простой точности без знака, или нижних частей знаковых чисел двойной точности.

3.2.3. Регистры ввода вывода МАСРегистры для входного порта X – MX0, MX1, AR, MR0, MR1, MR2, SR0, SR1.

Регистры для входного порта Y – MY0, MY1, MF.

Регистры для выходного порта R – MR (MR0, MR1, MR2), MF.

3.2.4. Операции над регистром MRКак показано на рис.3.1 регистр MR разбит на три секции: MR0 (биты 0-15), MR1 (биты 16-31) и MR2 (биты 32- 39). Каждая из них может быть загружена с DMD-шины и выведена на R- или DMD-шину. Регистр MR2 связан с младшими восемью разрядами этих шин. Когда MR2 выводится на R- или DMD-шину это означает, что знак расширен до 16 разрядов.

3.2.5. Насыщение и переполнение МАСПосле каждой операции блок сложения/вычитания генерирует сигнал переполнения MV, который подключен регистру состояния арифметики процессора ASTAT. Бит MV устанавливается в 1 если результат сложения выходит за границы регистров MR1/MR2 – 32 бита, т.е. если один из девяти старших разрядов регистра MR не 0, или все нули.

Регистр MR имеет возможность насыщения в определённом положительном или отрицательном значении, если происходит переполнение. Насыщение зависит от состояния бита MV регистра состояний арифметики ASTAT и бита MSB регистра MR2. Таблица 3.2. описывает операцию насыщения.

Таблица 3.2

| MV | MSB | Содержимое регистра MR после операции |

| 0 | 0 или 1 | Без изменений |

| 1 | 0 | 00000000 0111111111111111 1111111111111111 (положит.) |

| 1 | 1 | 11111111 1000000000000000 0000000000000000 (отрицат.) |

Насыщение в МАС является скорее командой, чем режимом, как в ALU. Она используется при завершении последовательности умножений с накоплением, таким образом, чтобы промежуточные переполнения не привели сумматор к насыщению.

Переполнение больше MSB недопустимо. В обратном случае знаковый разряд будет потерян и насыщение не будет правильным. Однако, чтобы достигнуть этого состояния требуется 255 переполнений.

3.2.6. ОкруглениеСумматор может округлять 40-разрядный результат до 15-16 разряда. Округление можно отнести к системе команд микропроцессора. Округленный результат направляется либо в MR, либо в регистр обратной связи MF. Когда для вывода используется MF, в него записывается 16-разрядный округленный результат. Аналогично, если для вывода выбран MR, то в MR1 записываются 16 разрядов округленного результата, а в MR2 – эффект округления, таким образом получается 24-разрядный округленный результат.

Сумматор использует несмещенную схему округления. Стандартный метод смещенного округления состоит в записи 1 в 15-ю разрядную позицию. Этот метод вызывает ряд положительных смещений, начиная с середины (когда MR=0х8000), округляя результат вверх. Сумматор же устраняет это смещение, устанавливая 16 бит в 0, когда значение регистра MR достигает середины. При этом четные значения MR1 округляются вниз, а нечетные вверх. Таким образом получается однородная последовательность смещений.

Пример типичной операции округления:

MR2 MR1 MR0

Неокругленное значение : xxxxxxxx xxxxxxxx00100101 1xxxxxxxxxxxxxxx

Бит 15 = 1

Прибавляем 1 к 15 разряду и смещаем 1

Округленное значение : xxxxxxxx xxxxxxxx00100110 0xxxxxxxxxxxxxxx

MR2 MR1 MR0

Неокругленное значение : xxxxxxxx xxxxxxxx01100110 1000000000000000

Бит 15 = 1 и биты 0-14 = 0

Прибавляем 1 к разряду 15 и сдвигаем 1

xxxxxxxx xxxxxxxx01100111 0000000000000000

Сейчас бит 16 = 1, устанавливаем его в 0

Округленно значение : xxxxxxxx xxxxxxxx01100110 0000000000000000

В последнем случае 16 бит устанавливается в 0. Этот алгоритм применяется на каждой операции округления.

3.2.7. Смещенное округлениеРежим смещенного округления возможен в процессорах ADSP-217x, ADSP-218x, и ADSP-21msp58/59. Этот режим выбирается путем установки бита BIARND регистра управления SPORT0. Если BIARND=0, то используется операция несмещенного округления, если BIARND=1, то смещенного.

Пример:

MR перед RND Смещенный результат RND Несмещенный результат RND

00-0000-8000 00-0001-8000 00-0000-8000

00-0001-8000 00-0002-8000 00-0002-8000

00-0000-8001 00-0001-8001 00-0001-8001

00-0001-8001 00-0002-8001 00-0002-8001

00-0000-7FFF 00-0000-7FFF 00-0000-7FFF

00-0001-7FFF 00-0001-7FFF 00-0001-7FFF

Этот режим эффективен только, в том случае, когда значение регистра MR0 больше 0х8000. Во всех других случаях работают обычные операции округления. Этот режим позволяет более эффективно реализовывать алгоритмы, использующие смещенное округление, например, подпрограммы речевого сжатия GSM.

4. BARREL SHIFTERShifter предоставляет полный набор сдвиговых функций для 16- и 32-разрядных операндов. Это арифметические сдвиги, логические сдвиги и нормализация. Так же shifter выполняет сортировку. Эти базисные функции могут быть объединены, чтобы реализовать работу с числами любого формата, в том числе с плавающей точкой.

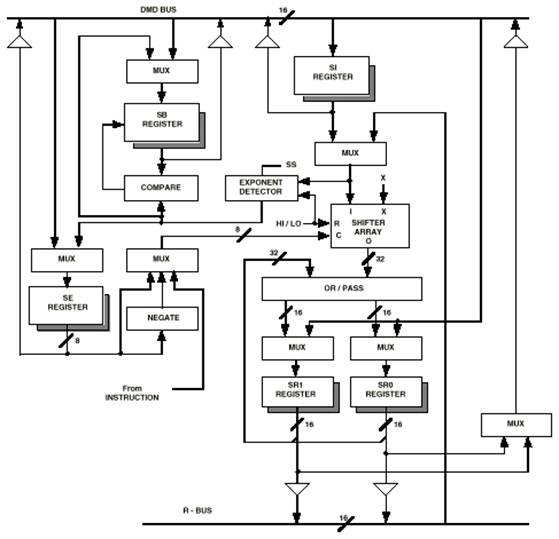

4.1. Описание блок схемыРисунок 4.1 иллюстрирует блок схему модуля сдвига. Shifter может быть разделен на следующие части: массив сдвига, логика OR/PASS, детектор порядка и логика сравнения порядка.

|

Массив сдвига принимает 16-разрядные данные и в одном цикле может поместить их в любой позиции 32-разрядного поля вывода. Это дает 49 возможных размещений в поле вывода. Размещение 16-ти входных разрядов определяется кодом управления C и сигналом ссылки HI/LO.

Массив сдвига и связная логика OR/PASS окружены набором регистров. Входной регистр Shifter (SI) содержит данные для массива сдвига и детектора порядка. SI-16-разрядный, записывается и читается с DMD-шины. В качестве входных регистров для массива сдвига и детектора порядка могут служить AR, SR или MR, подключенные через R-шину. Выходной 32-разрядный регистр SR разделен на две части по 16 разрядов: SR0 и SR1. Они могут быть загружены с DMD шины и выведены на R- или DMD-шину. Также SR подключен к блоку OR/PASS логики для проведения сдвигов двойной точности.

Похожие работы

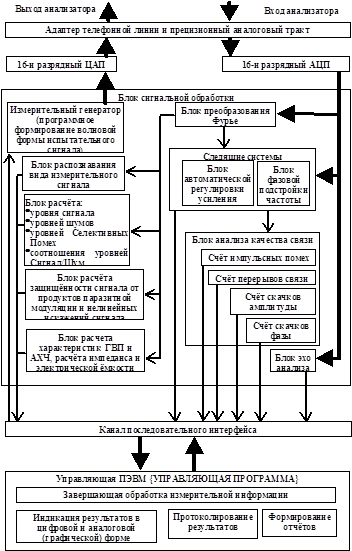

... 10 Литература.................................................................................................................................... 11 Назначение и основные параметры анализатора телефонных каналов. Анализатор телефонных каналов предназначен для проведения измерений параметров каналов тональной частоты (ТЧ) первичных сетей связи, ведомственных телефонных сетей и ...

... преобразование Лапласа от АФЧХ; 3) найти коэффициенты фильтра, взяв дискретные значения импульсной переходной функции k(nT). Определение порядка и синтез коэффициентов Цифровых фильтров, входящих в состав эквалайзера. Предположим, что ФЧХ равна 0. Тогда для получения импульсной переходной функции полосового фильтра с полосой пропускания fi-1 ÷ fi достаточно взять обратное ...

... неявно путем считывания только старших битов результата и отбрасывания младших. 5. Арифметико-логическое устройство (ALU) ALU выполняет арифметические операции над данными с фиксированной и плавающей точкой и логические операции над данными с фиксированной точкой. Команды ALU с фиксированной точкой оперируют над 32-разрядными операндами с фиксированной точкой и выдают 32-разрядный ...

... порту в терминал. Рисунок 4.4. - Блок - схема передачи данных в терминал. Далее после окончания приема или передачи данных , в терминал передается команда "устройство свободно", что разрешает дальнейшие запросы на обмен данными. Перезагрузка программы в память и инициализация происходят при нажатии кнопки RESET. Полная блок-схема алгоритма предоставленна в приложении. Данный алгоритм ...

0 комментариев