Шифратор (кодер) это комбинационное устройство, имеющее 2n входов и n выходов. При подаче активного сигнала на один из его входов на выходе должен образоваться двоичный код, выражающий номер входа, на который подан активный сигнал. Особенность шифратора в том, что в любой момент времени только на одном из входов может присутствовать логическая 1 (или логический 0). Наличие 1 (или 0) более, чем на одном входе рассматривается как запрещенное состояние.

Можно сказать, что шифратор преобразует унитарный код в двоичный.

Некоторые из шифраторов снабжаются входом разрешения работы. Наличие такого входа позволяет выделять сигнал в определенный момент времени.

Таблица 1. Таблица истинности шифратора

|

N |

Входные сигналы |

Выходной код |

|||||||||

|

x0 |

x1 |

x2 |

x3 |

x4 |

x5 |

x6 |

x7 |

y3 |

y2 |

y1 |

|

|

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

|

2 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

|

3 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

|

4 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

|

5 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

|

6 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

|

7 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

Рассмотрим вариант построения восьмивходового полного шифратора с нулевыми активными значениями входных сигналов. Закон функционирования такого шифратора представлен в таблице истинности 1.

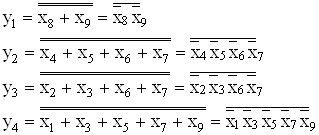

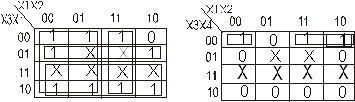

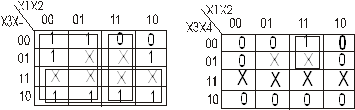

Можно заметить, что исходная функция принимает нулевое значение в каждой строке всего лишь один раз, что упрощает решение задачи. Нетрудно заметить, что логическая единица на выходе y3 получается в случае, если перемножить аргументы x4, x5, x6 и x7, а результат проинвертировать:

![]() .

.

Для остальных сигналов

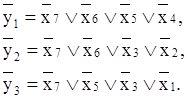

![]() ,

,

![]() .

.

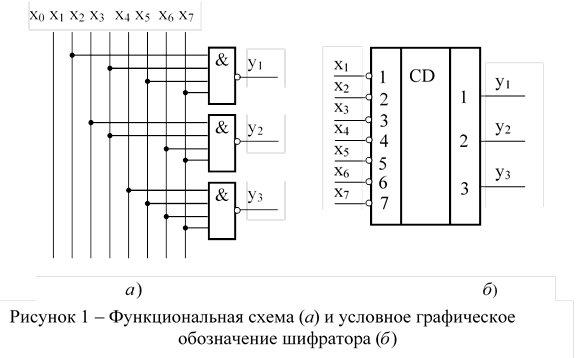

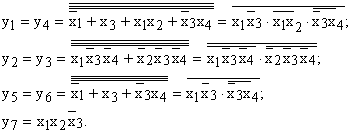

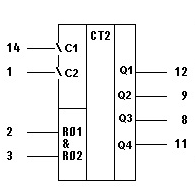

Для реализации данного шифратора требуется три ЛЭ 4И-НЕ (рисунок 1 а). Судя по полученным выражениям, входной сигнал x0 не участвует в формировании выходного кода. Отсутствие сигнала на любом из остальных выходов x1 - x7 указывает на то, что установлен нулевой набор. На рисунке 1, б представлено условное графическое обозначение данного шифратора, здесь символ CD образован из букв, входящих в английское слово CODER. На входах показано инверсное управление, поскольку активным уровнем является лог. 0.

Следует отметить, что шифратор может иметь и инверсные выходы. В этом случае выходные сигналы в соответствии с законом отрицания могут быть описаны следующими выражениями:

Приоритетный шифратор означает то, что при одновременном запросе с нескольких каналов (одновременном нажатии нескольких кнопок) на выходе будет сформирован код старшего канала. Приоритетный шифратор вырабатывает на выходе двоичный номер старшего запроса. Легко видеть, что при наличии всего одного возбужденного входа приоритетный шифратор работает так же, как и двоичный.

Поэтому в сериях элементов двоичный шифратор как самостоятельный элемент может отсутствовать. Режим его работы — частный случай работы приоритетного.

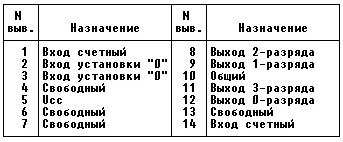

Таблица полностью характеризует работу приоритетного шифратора при всех возможных комбинациях сигналов: El — сигнала разрешения работы данного шифратора; ![]() сигналы на входах шифратора; A2…A0 — значений разрядов выходного двоичного кода, формирующего номер старшего запроса. Все перечисленные сигналы формируются при условии EI = 1 (работа шифратора разрешена). При EI = 0 независимо от состояний входов запросов все выходные сигналы шифратора становятся нулевыми.

сигналы на входах шифратора; A2…A0 — значений разрядов выходного двоичного кода, формирующего номер старшего запроса. Все перечисленные сигналы формируются при условии EI = 1 (работа шифратора разрешена). При EI = 0 независимо от состояний входов запросов все выходные сигналы шифратора становятся нулевыми.

Таблица 2 Таблица истинности приоритетного шифратора

|

EI |

R7 |

R6 |

R5 |

R4 |

R3 |

R2 |

R1 |

R0 |

A2 |

A1 |

A0 |

|

1 |

1 |

X |

X |

X |

X |

X |

X |

X |

1 |

1 |

1 |

|

1 |

0 |

1 |

X |

X |

X |

X |

X |

X |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

X |

X |

X |

X |

X |

1 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

X |

X |

X |

X |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

1 |

X |

X |

X |

0 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

X |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

0 |

X |

X |

X |

X |

X |

X |

X |

X |

0 |

0 |

0 |

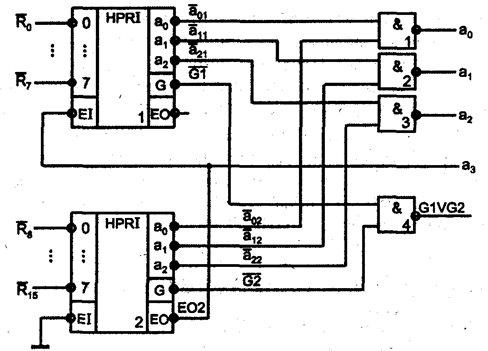

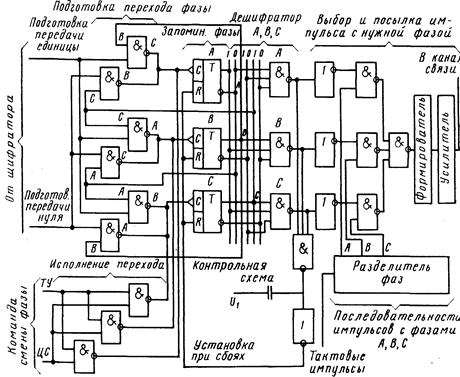

На рисунке 2 показано наращивание числа входов шифратора вдвое (от 8 до 16). При этом показаны шифраторы с инверсными входами и выходами, как это свойственно большинству серий элементов.

Если на входах шифратора 2 запросов нет, он разрешает работу младшего, вырабатывая сигнал ЕО2 = 0 и приводит свои выходы a2…a0 в пассивное единичное состояние. Теперь на выходы a схемы в целом передаются инвертированные значения выходов a01, a11, a21 младшего шифратора, что вместе с нулем в разряде аз соответствует номерам от нуля до семи.

Рисунок 2. Схема наращивания размерности приоритетного шифратора

Таким образом, строится схема с 16 входами запросов, причем вход ![]() имеет старший приоритет. Выход элемента 4 принимает единичное значение при наличии хотя бы одного запроса в любом из шифраторов.

имеет старший приоритет. Выход элемента 4 принимает единичное значение при наличии хотя бы одного запроса в любом из шифраторов.

Шифраторы применяются в контроллерах прерываний работы микропроцессора внешними устройствами, в параллельном преобразователе напряжения в код. Они также применяются в устройствах автоматики, особенно в устройствах ввода/вывода информации. На клавиатуре ввода имеются клавиши с десятичными цифрами, буквенный алфавит, а при нажатии клавиши позиционный код должен преобразоваться в двоичный.

Похожие материалы

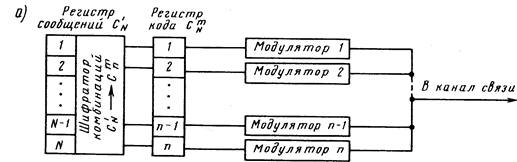

... по определенным правилам синтезировать логические схемы с заданными характеристиками. Выполнение предлагаемого задания позволит приобрести основные необходимые для инженера навыки. 1. Порядок синтеза схемы шифратора и кодопреобразователя для управления 1-разрядным 7-сегментным индикатором Проиллюстрируем методику решения задачи на примере. 1. Входные данные вводятся в унитарном коде. ...

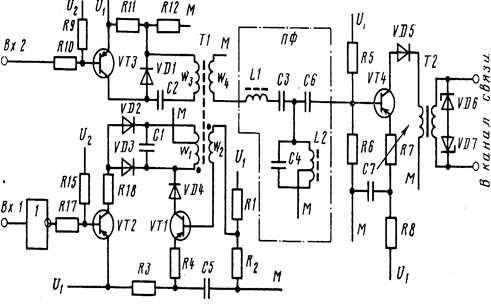

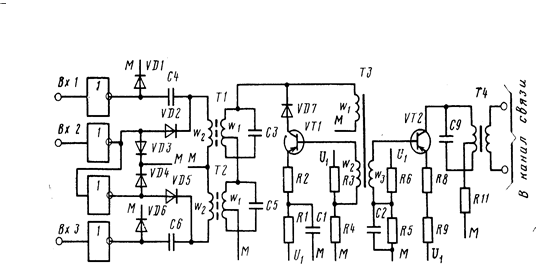

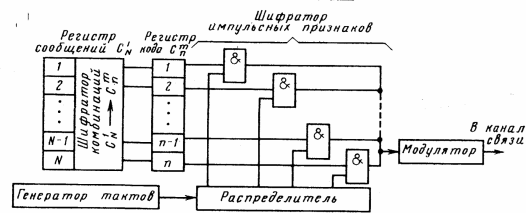

... признаками (рис. 4.28) при включении реле ПЛ или МЛ в линию связи посылается ток определенной полярности, т. е. эти реле составляют схему генератора импульсных признаков. б) Рис. 5. Функциональная схема шифратора импульсных признаков при параллельной и последовательной передаче элементов сигнала. Рис. 6. Схема релейного шифратора полярной системы телемеханики Цепи управления реле ...

... входа В ряде случаев с целью экономии оборудования выгодно дешифратор реализовать не на стандартных логических элементах, а в виде специальной схемы, помещаемой в одном корпусе. Шифратор выполняет противоположную дешифратору функцию, то есть преобразует одноразрядный код с основанием Е=2n в n-разрядный двоичный код. При построении шифратора на ПЭ и ФН можно использовать ...

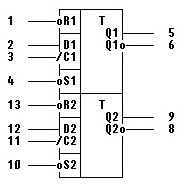

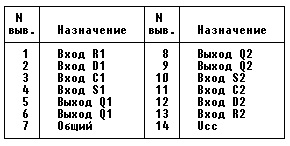

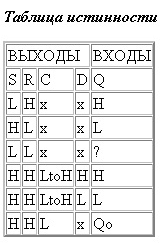

... на входе R устанавливает все выходы микросхемы в 0. Описание работы схемы шифратора Кнопки управления S1:1 – кнопка занесения информации в блок хранения и обработки информации S8:1 – кнопка начала кодирования S3:1, S4:1, S5:1, S6:1, S7:1, S9:1 – кнопки установки начального состояния ДПСЧ Датчик псевдослучайных чисел (ДПСЧ) Цель ДПСЧ генерация гамма кода, который ...

... » использовались раньше, а в наши дни они заложены практически в любой, даже самой сложной программе шифрования. Каждый из рассмотренных методов реализует собственный способ криптографической защиты информации и имеет собственные достоинства и недостатки, но их общей важнейшей характеристикой является стойкость. Под этим понимается минимальный объем зашифрованного текста, статистическим анализом ...

0 комментариев