Навигация

Суперскалярні мікропроцесори

Зміст

Вступ

Суперскалярні мікропроцесори 1.Структурний паралелізм мікропроцесорів 2.Структурні конфлікти та причини їхнього виникнення 3. Конфлікти за даними 4. Архітектура СМП 5. Основні прийоми підвищення швидкодії в СМП 6 .Напрямок розвитку суперскалярної архітектуриВисновок

Література

Вступ

Тема реферату «Суперскалярні мікропроцесори» з дисципліни «Мультімікропроцесорні системи».

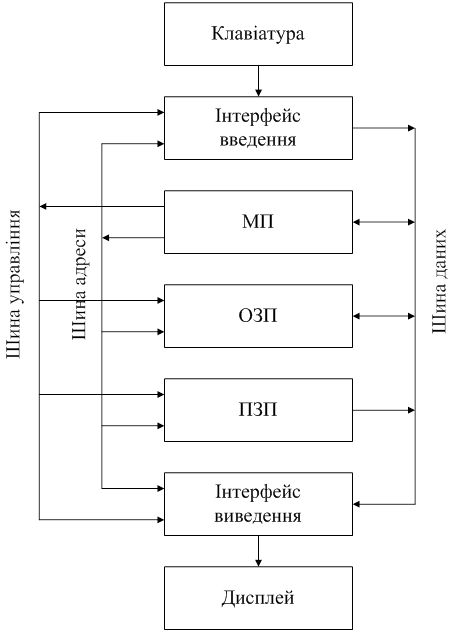

Мультімікропроцесорні системи (ММПС) - це системи, що мають два й більше компонент, які можуть одночасно виконувати команди. Підпорядкованими процесорами можуть бути спецпроцесори, розраховані на виконання певного типу завдання або процесори широкого застосування. Спецпроцесори - співпроцесори, процесори вводу-виводу.

Суперскалярні мікропроцесори (далі – СМП) ─ це такі мікропроцесори, система команд яких не містить ніяких вказівок на паралельну обробку усередині мікропроцесора (мал. 1).

Ідея розвитку СМП - побудова можливо більшої кількості паралельних структур при збереженні традиційних послідовних програм, тобто компілятори й апаратури. МП самі, без участі програміста, забезпечують завантаження паралельно працюючих функціональних пристроїв у мікропроцесорі.

мікропроцесор конфлікт суперскалярна архітектура

1.Структурний паралелізм мікропроцесорів

Конвеєрна організація виконання команд. Конфлікти й способи їхнього усуненняСучасні процесори містять 10 і більше обробних пристроїв, кожне з яких представляє із себе конвеєр. Ефективне завантаження кожного пристрою забезпечується або апаратурами процесора або компілятором, на вхід якого надходить послідовність команд. Основний метод проектування процесорів полягає в сполученні операцій, тобто в певний момент часу процесор виконує 2 і більше операції. Цей метод досягається шляхом впровадження структурного паралелізму й конвеєризації.

- При структурному паралелізмі: сполучення операцій досягається шляхом відтворення в декількох копіях апаратної структури.

- При конвеєризації: поділ виконує команди, що, на дрібні частини (щабля), і виділення для кожного щабля окремого функціонального блоку апаратури.

Розглянемо наступні щаблі:

1. Вибірка команди (1);

2. Декодування (2);

3. Виконання (3);

4. Звертання до пам'яті (4);

5. Запам'ятовування результату (5).

При конвеєрній обробці виникають ситуації, що перешкоджають виконанню наступної команди (конфлікти) :

1. Структурні конфлікти. Виникають, коли апаратні засоби не можуть підтримувати всі можливі комбінації виконуваних команд у режимі одночасного виконання зі сполученням.

2. Конфлікти за даними. Виконання наступної команди залежить від результату виконання попередньої команди.

3. Конфлікти по керуванню. Виникають у випадку виконання команд умовного й безумовного переходів, що змінюють стан програмного лічильника.

2. Структурні конфлікти. Причини їхнього виникнення

Способи мінімізаціїТакі конфлікти виникають у машинах з функціональними пристроями, конвеєризованими не повністю. Час роботи такого пристрою - кілька тактів синхронізації конвеєра. У цьому випадку послідовні команди не можуть надходити на даний пристрій у кожному такті.

Недостатнє дублювання деяких ресурсів, що приводить також до припинення конвеєра (приклад - наявність тільки одного порту запису в регістровий файл, але при певних обставинах може знадобитися дві записи в регістровий файл за один такт).

Наявність однієї пам'яті для команд і даних ( немає роздільної кеш-пам'яті команд і кеш-пам'яті даних). Коли одна команда містить звертання до пам'яті за даними, вона буде конфліктувати із вибіркою більше пізньої команди з пам'яті.

При виконанні четвертої команди на першому етапі відразу виникає конфлікт при звертанні до пам'яті, тому що перша команда здійснює звернення до пам'яті, а перша команда повинна здійснювати вибірку коду операції з пам'яті. У цьому випадку здійснюється припинення конвеєра на один такт (stall), виникає так званий "конвеєрний міхур" тому що він проходить по всьому конвеєрі, але не виконує ніякої корисної роботи.

3. Конфлікти за даними

Конфлікти цього типу виникають у тому випадку, коли застосування конвеєрної обробки може змінити порядок обігу за операндами так, що він буде кардинально відрізнятися від порядку проходження операндів при послідовному виконанні команд.

Таблиця 1

| ADD R1,R2, R3 | 1 | 2 | 3 | 4 | 5 | ||||

| SUB R4, R1, R5 | 1 | 2 | 3 | 4 | 5 | ||||

| AND R6, R1, R7 | 1 | 2 | 3 | 4 | 5 | ||||

| OR R8,R1, R9 | 1 | 2 | 3 | 4 | 5 | ||||

| XOR R10,R1,R11 | 1 | 2 | 3 | 4 | 5 |

Приклад: відповідно до вищенаведеної таблиці всі команди, що випливають за АDD, використають її результат, але для такого конвеєрного виконання команда SUB прочитає неправильний результат, тому що команда додавання ще не встигла записати результат виконання.

Ця проблема вирішується з використанням схемних рішень, називаних пересиланням даних (просування, обхід або закоротка). У цьому випадку результат операції АЛУ знову подається на вхід АЛУ. Якщо апаратури виявляє, що попередня операція записує свій результат у регістр, що є джерелом для наступної операції, то логічні схеми керування вибирають як входи результат, що надходить по ланцюгах обходу, а не значення, прочитане з регістрового файлу. Така техніка обходів може бути узагальнена й використана не тільки для АЛУ, але й для інших функціональних пристроїв у мікропроцесорі.

Конфлікти за даними класифікуються в такий спосіб:

- читання після читання (RAR). Залежність відсутня. Порядок виконання команд не важливий;

- читання після запису (RAW). j-я команда намагається прочитати результат i-й команди перш, ніж i-я запише цей результат. Усувається механізмом обходу;

- запис після читання (WAR).j-я команда намагається записати в приймач перш, ніж його вміст считається i-й командою, у результаті i-я команда може некоректно одержати нове значення;

- запис після запису (WAW). j-я команда намагається записати операнд перш, ніж буде записаний результат i-й. Виникає в конвеєрах при записі з багатьох щаблів, або що дозволяють виконуватися наступній команді, коли попередня припинена.Конфлікти за даними, що приводять до припинення конвеєра.Приклад послідовності команд, яка приводить до такого рода конфликтів приведен в таблиці 2.

Таблиця 2

| LW R1,32,(R6) | 1 | 2 | 3 | 4 | 5 | ||||

| ADD R4,R1,R7 | 1 | 2 | 6 | 3 | 4 | 5 | |||

| SUB R5,R1,R8 | 1 | 6 | 2 | 3 | 4 | 5 | |||

| AND R6,R1,R7 | 6 | 1 | 2 | 3 | 4 | 5 |

Команда LW (завантаження регістра 1 з пам'яті за адресою, що перебуває в регістрі 6) має затримку, що не усувається механізмом обходу. Це така ж ситуація (міхур), як і для структурного конфлікту . Для даного випадку використається апаратури внутрішніх блокувань конвеєра.

Похожие работы

... команд називається суперскалярною. Завдяки використовуванню даної технології і забезпечується додаткова ефективність в порівнянні з процесором 486. Суперскалярна архітектура звичайно асоціюється з мікросхемами RISC (Reduced Instruction Set Computer — комп'ютер із спрощеною системою команд). Процесор Pentium — одна з перших мікросхем CISC (Complex Instruction Set Computer — комп'ютер з складною ...

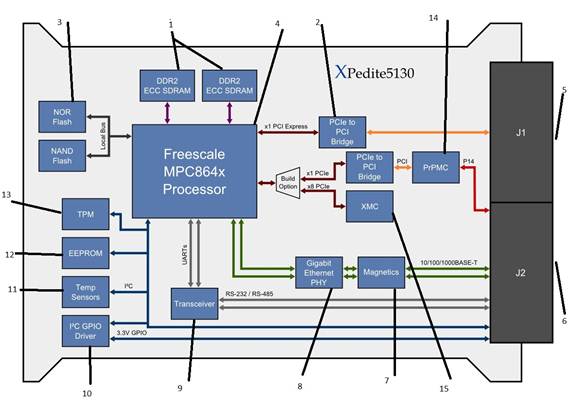

... , винайдена послідовність інструкцій, які зберігають всі модулі виконання максимально зайнятими на обох ядрах. 5. Ці числа живлення тільки для моделей MC8640Dwxx1067Nz і MC8640wxx1067Nz. VDD_Coren = 0.95 V і 1.2 Архітектура мікропроцесора MPC8640D Блок цього процесора включає в себе 2 ядра процесора та 1Мб кеш-пам’яті другого рівня (L2) (чотири блоки по 32Кб Cache SRAM). Високошвидкісна ...

обачив світло спрощений варіант процесора Pentium II, назва ,що отримала Celeron. В ньому вдвічі зменшений вторинний кеш і, немовби, прибрана підтримка багатопроцесорних систем. Однак шляхом “хірургічного” втручання підтримку багатопроцесорності можна повернути. Це пояснюється тим, що в Celeron застосоване ядро Pentium II без будь-яких змін. В 1999 році з'явився процесор Pentium III. В ньому ...

... "ВНІЇЕМ-3", а також надшвидкодіюча БЕСМ-6 з продуктивністю 1 млн операцій в секунду. 2.3 Третє покоління комп'ютерів Поява інтегрованих схем започаткувала новий етап розвитку обчислювальної техніки - народження машин третього покоління. Інтегрована схема, яку також називають кристалом, являє собою мініатюрну електронну схему, витравлену на поверхні кремнієвого кристала площею приблизно 10 ...

0 комментариев