Навигация

Аналіз заданої топології

3. Аналіз заданої топології

Технологія комутації сегментів Ethernet була запропонована фірмою Kalpana в 1990 році у відповідь на зростаючі потреби в підвищенні пропускної здатності зв'язків високопродуктивних серверів із сегментами робочих станцій.

Головною причиною підвищення продуктивності мережі при використанні комутатора є паралельна обробка декількох кадрів. Перевага комутатора, завдяки якій він завоював дуже гарні позиції в локальних мережах, це його висока продуктивність, то розробники комутаторів намагаються випускати так звані що не блокують(non-blocking) моделі комутаторів.

Комутатор, що не блокує, - це такий комутатор, що може передавати кадри через свої порти з тією же швидкістю, з якої вони на них надходять, при умові, що не відбувається блокування кадрів через обмежену швидкість вихідного порту.

Широкому застосуванню комутаторів, безумовно, сприяло та обставина, що впровадження технології комутації не вимагало заміни встановленого в мережах обладнання - мережевих адаптерів, концентраторів, кабельної системи. Порти комутаторів працювали у звичайному напівдуплексному режимі, тому до них прозоро можна було підключити як кінцевий вузол, так і концентратор, що організує цілий логічний сегмент. Незважаючи на те що в комутаторах працюють відомі й добре відпрацьовані алгоритми прозорих мостів і мостів з маршрутизацією від джерела, існує велика розмаїтість моделей комутаторів. Вони відрізняються як внутрішньою організацією, так і набором виконуваних додаткових функцій, таких як трансляція протоколів, підтримка алгоритму покриваючого дерева, утворення віртуальних логічних мереж і ряду інших.

Особливості технічної реалізації комутаторів. Після того як технологія комутації привернула загальну увагу й отримала високі оцінки фахівців, багато компаній зайнялися реалізацією цієї технології у своїх пристроях, застосовуючи для цього різні технічні рішення. Багато комутаторів першого покоління були схожі на маршрутизатори, тобто ґрунтувалися на центральному процесорі загального призначення, пов'язаному з інтерфейсними портами по внутрішній швидкісній шині.

Комутатор на процесорі загального призначення

Основним недоліком таких комутаторів була їхня низька швидкість.

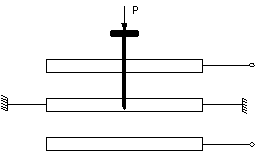

Комутаційна матриця забезпечує основний і найшвидший спосіб взаємодії процесорів портів, саме він був реалізований у першому промисловому комутаторі локальних мереж.

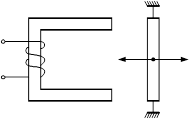

Реалізація комутаційної матриці 8x8 за допомогою двійкових перемикачів

Особливістю комутаційної матриці залишається технологія комутації фізичних каналів. Відомим недоліком цієї технології є відсутність буферизації даних усередині комутаційної матриці - якщо складений канал неможливо побудувати через зайнятість вихідного порту або проміжного комутаційного елемента, то тоді дані повинні накопичуватися в їхньому джерелі, у цьому випадку - у вхідному блоці порту, що прийняв кадр. Основні переваги таких матриць - висока швидкість комутації й регулярна структура, що зручно реалізовувати в інтегральних мікросхемах.

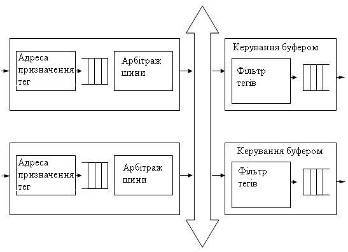

У комутаторах із загальною шиною процесори портів зв'язують високошвидкісною шиною, яка використовується в режимі поділу часу. Щоб шина не блокувала роботу комутатора, її продуктивність повинна дорівнювати принаймні сумі продуктивності всіх портів комутатора.

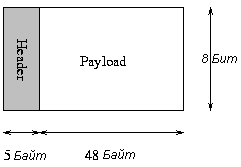

Архітектура комутатора з загальною шиною

Кадр повинен передаватися по шині невеликими частинами, по декілька байт, щоб передача кадрів між декількома портами відбувалася в псевдопаралельному режимі, не вносячи затримок у передачу кадру в цілому. Вхідний блок процесора поміщає в комірку, прийнятний по шині, тег, у якому вказує номер порту призначення. Кожен вихідний блок процесора порту містить фільтр тегів, що вибирає теги, призначені даному порту. Шина, так само як і комутаційна матриця, не може здійснювати проміжну буферизацію, але тому що дані кадру розбиваються на невеликі комірки, то затримок з початковим очікуванням доступності вихідного порту в такій схемі немає - тут працює принцип комутації пакетів, а не каналів.

Третя базова архітектура взаємодії портів – двовхідна поділювана пам'ять.

Архітектура поділюваної пам'яті

Вхідні блоки процесорів портів з'єднуються з входом перемикачем, що, поділяє пам'ять, а вихідні блоки цих же процесорів з'єднуються перемикачем з виходом цієї пам'яті. Перемиканням входу й виходу поділюваної пам'яті управляє менеджер черг вихідних портів. У поділюваній пам'яті менеджер організує кілька черг даних, по одній для кожного вихідного порту. Вхідні блоки процесорів передають менеджерові портів запити на запис даних у чергу того порту, що відповідає адресі призначення пакета. Менеджер по черзі підключає вхід пам'яті до одному із вхідних блоків процесорів і той переписує частину даних кадру в чергу певного вихідного порту. По мірі заповнення черг менеджер робить також почергове підключення виходу поділюваної пам'яті до вихідних блоків процесорів портів, і дані із черги листуються у вихідний буфер процесора.

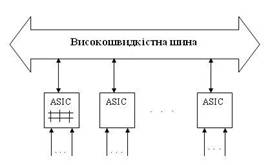

Комбіновані комутатори. У кожної з описаної архітектури є свої переваги й недоліки, тому часто в складних комутаторах ці архітектури застосовуються в комбінації одна з одною.

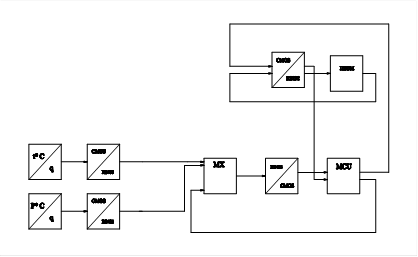

Комбінування архітектури комутаційної матриці й загальної шини

Комутатор складається з модулів з фіксованою кількістю портів (2-12), виконаних на основі спеціалізованій ВІС, що реалізує архітектуру комутаційної матриці. Якщо порти, між якими потрібно передати кадр даних, належать одному модулю, то передача кадру здійснюється процесорами модуля на основі наявної в модулі комутаційної матриці. Якщо ж порти належать різним модулям, то процесори спілкуються по загальній шині. При такій архітектурі передача кадрів всередині модуля буде відбуватися швидше, ніж при міжмодульній передачі, тому що комутаційна матриця - найбільш швидка, хоча й найменш масштабований спосіб взаємодії портів. Швидкість внутрішньої шини комутаторів може досягати десятки Гбіт/с.

Похожие работы

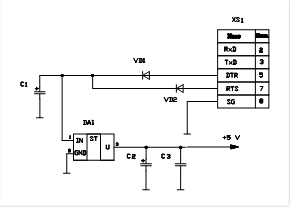

... виході мікроконтролера в рівні RS-232 використовується відповідний перетворювач, як це наведено на структурній схемі. 3. Розробка електричної принципової схеми комп’ютерного засобу вимірювання тиску і температури у кліматичній камері Електрична принципова схема розробленого пристрою наведена у графічній частині курсового проекту. Пристрій розрахований на підключення двох перетворювачів, але ...

... ї комп’ютерної мережі авіакомпанії «Північна компанія» 2.3.1 Програмний пакет проектування і моделювання гетерогенних комп'ютерних мереж NetCracker Professional Призначення системи: автоматизоване проектування і моделювання локальних і корпоративних комп'ютерних мереж в цілях мінімізації витрат часу і засобів на розробку, верифікацію проектів. Функції: створення проекту мережі; анімаційне ...

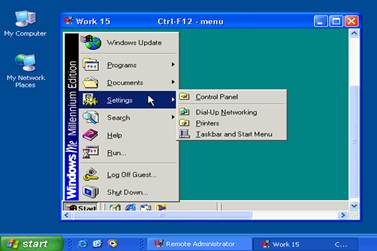

... до ПК - це атака ззовні і не допустити підключення. 3.1.1. Віддалене управління засобами Telnet У наш час існує безліч засобів для віддаленого управління і адміністрування комп'ютерів мережі. Засіб управління комп'ютером може бути підключене і до віддалених машин для виконання досить широкого кола задач, але далеко не всіх. Велика кількість проблем пов’язані з обслуговуванням, адмініструванням ...

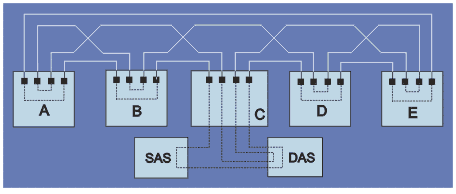

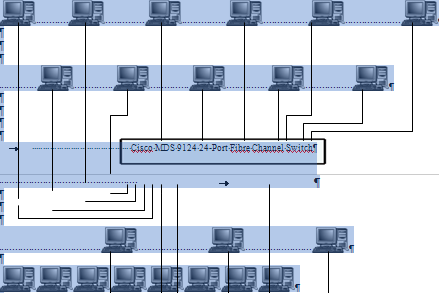

... всіх сторедж ресурсів, а це, у свою чергу, значно зменшує витрати на їх підтримку, вартість якої, як правило, становить більше 50% від вартості обладнання. Вибір обладнання та розробка структури мережі мережева топологія зірка комп'ютер Вибираємо комутатор фірми Cisco MDS 9124 24-Port Fibre Channel Switch (DS-C9124-K9=) та мережеві адаптери фірми Brocade 825. Так як наша мережа будується по ...

0 комментариев