Сигналы и данные

Всё, что нас окружает, и с чем мы сталкиваемся ежедневно, относится либо к физическим телам, либо к физическим полям. Из физики известно, что состояния вечного покоя не существует, а физические объекты находятся в состоянии непрерывного движения и изменения, которое сопровождается обменом энергии и переходом энергии из одной формы в другую.

Все виды обмена энергией сопровождаются появлением сигналов. При взаимодействии сигналов с физическими телами, в этих телах возникают определённые изменения их свойств, т. е. происходит регистрация сигналов. Такие изменения можно наблюдать, измерять или фиксировать иными способами, при этом возникают данные.

Данные - это зарегистрированные сигналы. Они несут в себе информацию о событиях, произошедших в материальном мире. Однако данные и информация не одно и то же.

Для того чтобы данные были преобразованы в информацию необходимо наличие метода извлечения информации из полученных данных.

Пример: Текст, написанный на иностранном языке, может содержать некоторую информацию, но человек не знающий этого языка не способен её извлечь, т. е. можно сказать, что метод извлечения информации ему недоступен.

Таким образом, информация это результат взаимодействия данных и соответствующих им методов.

Кодирование информации

Для автоматизации работы с данными очень важно их унифицировать, т. е. сделать наиболее универсальной их форму представления - для этого используется такой приём как кодирование.

Кодирование это выражение данных одного типа через данные другого тина.

Пример: Естественный человеческий язык это система кодирования понятий посредством слов и предложений. В то же время азбука - это система кодирования элементов языка (слов и предложений) с помощью графических символов - букв.

Можно привести другие примеры систем кодирования из различных областей техники, науки и культуры:

· запись математических выражений и формул — способ кодирования математических законов;

· нотная запись - способ кодирования музыкальной информации;

· телеграфная азбука — способ кодирования сообщений для передачи их по проводам.

В вычислительной технике существует своя система кодирования, в основе которой лежит представление данных в виде последовательностей из двух знаков: «0» и «1». Такая система называется двоичной системой кодирования, а знаки «1» и «0» - двоичными цифрами - битами. (От английского "binary digit” - "bit").

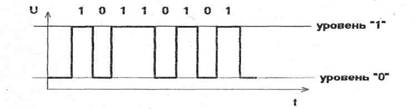

С точки зрения электрических сигналов, способы представления цифровой информации бывают различными. Наиболее распространёнными являются потенциальный код и импульсный код.

Потенциальный код - представляет «нули» и «единицы» разными уровнями напряжения. «Единице» соответствует высокий уровень напряжения, «нулю» - низкий.

Двоичное число 10110101 представленное потенциальным кодом будет выглядеть таким образом:

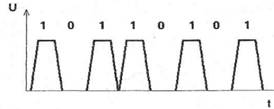

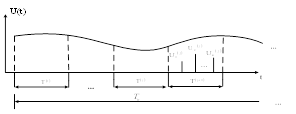

Импульсный код - представляет «нули» и «единицы» как отсутствие и присутствие импульса некоторой формы. Если «единице» соответствует наличие импульса, а «нулю» - отсутствие импульса, то двоичное число 10110101 в импульсном коде будет выглядеть так:

Возможны и другие способы представления цифровой информации: фазовый код, частотный код и более сложные смешанные системы, например, фазово-частотный способ кодирования.

Кодирование цифровых данных

Понятие «системы счисления»

Проблема представления в ЭВМ цифровой информации тесно связана с понятием систем счисления.

Система счисления - набор правил для обозначения чисел.

Различают позиционные и непозиционные системы счисления.

В непозиционной системе счисления каждая цифра, где бы она ни располагалась, означает одно и то же число. Например, римская систем нумерации где «I» всегда означает «1». «V» - «5», «X» - «10». Запись «XXX» означает «30» т. е. «три раза десять». Недостаток непозиционных систем счисления - трудность записи больших чисел и сложность выполнения арифметических операций.

В позиционной систем счисления значения каждой цифры зависит от её места в ряду цифр, изображающих число. Например, десятичная система счисления.

Количество различных цифр, употребляемых в позиционной системе, называется её основанием. Десятичная система счисления имеет основанием число десять и использует цифры: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9.

Всякое число в десятичной системе счисления изображается последовательности цифр, разделённой запятой на две части: целую и дробную. Цифры целой части справа налево от запятой выражают собой количество единиц, десятков и сотен и т. д., т. е. положительных целых степеней десяти, содержащихся в этом числе. Цифры дробной части слева направо от запятой выражают собой количество десятых, сотых и т. д. долей единицы, т. е. отрицательных степеней числа 10.

Пример:

236,52 =2*102+3*101+6*100+5*10-1+2*10-2

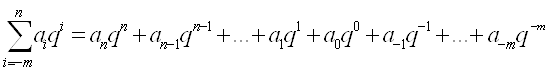

Любая позиционная система счисления представляет собой числа в виде последовательности цифр при степенях основания qi т. е.

где:

q - основание системы (целое положительное число);

ai - количество единиц 1-го разряда числа.

Пример: В двоичной системе счисления, число 111 — представляет собой запись десятичного числа «семь» потому, что

1*22+1*21 +1*20=4+2+1=7

Двоичное число 1010 равно десятичному числу «десять», так как

1*23 +0*22 +1*21+0*20=8+0+2+0=10

В шестнадцатеричной системе счисления для записи чисел используются цифры от 0 до 9 и буквы А, В, С, D, Е, F.

Соответствие чисел в шестнадцатеричной (HEX), двоичной (BIN), десятичной (DEC) и восьмеричной (ОСТ) системах:

BCD HEX BIN DEC OCT

0000 0000 0 0000 0 0

0000 0001 1 0001 1 1

0000 0010 2 0010 2 2

0000 0011 3 0011 3 3

0000 0100 4 0100 4 4

0000 0101 5 0101 5 5

0000 0110 6 0110 6 6

0000 0111 7 0111 7 7

0000 1000 8 1000 8 10

0000 1001 9 1001 9 11

0001 0000 A 1010 10 12

0001 0001 B 1011 11 13

0001 0010 C 1100 12 14

0001 0011 D 1101 13 15

0001 0100 E 1110 14 16

0001 0101 F 1111 15 17

0001 0110 10 10000 16 20

0001 0111 11 10001 17 21

0001 1000 12 10010 18 22

0001 1001 13 10011 19 23

0010 0000 14 10100 20 24

0010 0001 15 10101 21 25

0010 0010 16 10110 22 26

0010 0011 17 10111 23 27

0010 0100 18 11000 24 30

0010 0101 19 11001 25 31

0010 0110 1A 11010 26 32

0010 0111 1B 11011 27 33

0010 1000 1C 11100 28 34

0010 1001 1D 11101 29 35

0011 0000 1E 11110 30 36

0011 0001 1F 11111 31 37

0011 0010 20 100000 32 40

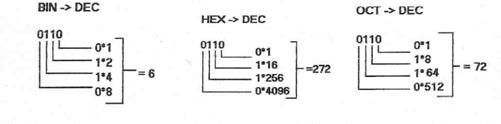

Пример: Преобразование данных в десятичную систему счисления

Специальная кодировка BCD (Binary Coded Decimal) предназначена для кодирования десятичных чисел в двоичной форме. В этой кодировке каждая цифра составного десятичного числа кодируется своим двоичным эквивалентом. Используются коды только для цифр от 0 до 9. Таким образом, кодировка обладает чрезвычайной кодовой избыточностью, но позволяет проще выполнять элементарные арифметические операции: сложение и вычитание. (Подробнее смотри таблицу перекодировок).

Кодирование текстовых данных

Понятие «кодовая таблица».

Если каждому символу (букве) алфавита сопоставить определённое целое число (например, его порядковый номер в алфавите), то с помощью двоичного кода можно кодировать и текстовую информацию. Восьми двоичных разрядов достаточно для кодирования 256 различных символов. Этого хватит для того, чтобы выразить все символы английского и русского языков, как строчные, так и прописные (заглавные), а также знаки препинания, символы основных арифметических действий и некоторые общепринятые символы, например, символ «№». Таблица соответствия символов языка и их кодов, выраженных в числовой форме, называется кодовой таблицей.

В ЭВМ используется несколько кодовых таблиц для кодирования текстовой информации: ASCII, KOI8, Win1251 и т. д. В различных кодовых таблицах одни и те же буквы русского алфавита могут иметь различные цифровые коды.

Пример: В кодовой таблице KOI8, широко распространённой в странах бывшего СССР, заглавные буквы русского алфавита имеют коды от 128 для "А " до 159 , для "Я".

В кодовой таблице Win 1251, используемой в русифицированной версии популярной операционной системы Windows, те же самые заглавные буквы русского алфавита имеют коды от 182 для «А» до 223 для «Я».

Существование различных кодовых таблиц для текстовых данных приводит к частичной несовместимости текстовых документов, созданных с использованием разных систем кодирования. Для устранения этой проблемы в большинстве современных программ редактирования и набора текста применяются специальные модули перекодировки, позволяющие правильно читать текст в любой из доступных кодировок.

Кодирование графических данных

При кодировании графических изображений в современных ЭВМ используются два подхода: растровое кодирование и векторное кодирование.

Растровое кодирование.

Понятие «растр изображения»

Если рассмотреть с помощью увеличительного стекла черно-белое графическое изображение, напечатанное в газете, то можно увидеть, что оно состоит из мельчайших точек, образующих характерный узор. Узор этот называется растром. Размеры и яркость каждой точки можно выразить с помощью целых чисел и таким образом осуществить кодирование растра с использованием цифрового (двоичного) кода.

Для черно-белых иллюстраций принято представление в виде комбинации точек с 256 оттенками серого цвета, для чего достаточно 8-разрядного двоичного кода.

Векторное кодирование

Понятие «графический примитив».

Некоторые виды изображений проще представить в виде набора простейших геометрических фигур: кругов, квадратов, овалов, кривых и прямых линий. Для изображения каждого из этих элементов (их ещё называют графические примитивы) необходимо указать только некоторые основные параметры.

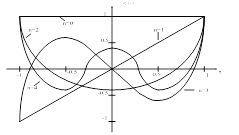

Пример: Для изображения окружности достаточно заказать её центр, длину радиуса и, возможно, толщину линии обводки. Для изображения квадрата достаточно указать координаты верхнего левого, и нижнего правого углов, и толщину линию обводки. , Кривые линии могут быть построены с использованием множества уравнений кривых второго порядка (y=ax2+bx1+c), кривых третьего порядка (у=ах3+Ьх2+сх+а) и кривых Безье.

Такой способ кодирования фигур и изображений позволяет сократить количество данных, необходимых для их описания.

Каждый из двух описанных выше способов кодирования графической информации имеет свои недостатки и преимущества и находит своё применение в различных областях. Растровое кодирование чаще применяется при работе с фотографиями, или какими-либо другими изображениями, на которых трудно выделить регулярные формы. Векторное кодирование находит широкое применение при создании всевозможных чертежей, схем и логотипов

Кодирование звуковой информации

Понятия «звуковой синтез» и «волновая таблица».

При кодировании звука в ЭВМ используется несколько методов. Рассмотрим наиболее распространённые из них: метод частотной модуляции и метод таблично-волнового синтеза.

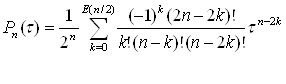

Метод частотной модуляции. Основан на том, что теоретически любой сложный звук можно разложить на последовательность простейших гармонических сигналов разных частот, каждый из которых представляет собой правильную синусоиду, а следовательно может быть описан числовыми параметрами, т. е. кодом.

В природе звуковые сигналы имеют непрерывный спектр, то есть являются аналоговыми. Их представление в виде дискретных цифровых сигналов выполняют специальные устройства - аналогово-цифровые преобразователи (АЦП). Обратное преобразование для воспроизведения звука, закодированного числовым кодом, выполняют цифро-аналоговые преобразователи (ЦАП).

Метод таблично-волнового синтеза. Этот метод упрощённо можно охарактеризовать так: в ЭВМ в заранее подготовленных таблицах хранятся образы звуков для множества различных музыкальных инструментов. Числовые коды выражают тип инструмента, номер его модели, высоту тона, продолжительность звучания и другие параметры. Звук, воспроизводимый в ЭВМ, получается в результате синтеза отдельных звуков в специальном устройстве - синтезаторе. Такой синтезатор является неотъемлемой частью всех современных электронных устройств воспроизведения звука, входящих в состав компьютеров и именуемых «звуковой картой».

Логические схемы и основы алгебры логики

Все устройства ЭВМ состоят из элементарных логических схем. Работа этих схем основана на законах и правилах алгебры логики, которая оперирует двумя понятиями: истинности и ложности высказывания. В соответствии с такой двоичной природой высказываний их условились называть логическими двоичными переменными и обозначать «1» в случае истинности (true) и «0» в случае ложности (false).

Две логические переменные X1 и X2, принимающие независимо друг от друга значения «0» и «1», могут образовывать логические функции. Всего, для двух независимых переменных, можно составить 16 различных функций. Рассмотрим некоторые из них.

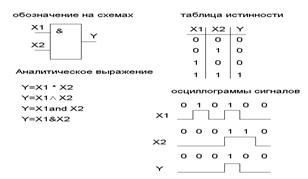

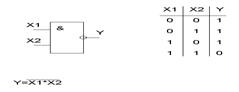

Логическое умножение «И»

- логическое умножение двух переменных Х1 и Х2 есть логическая функция Y, которая истинна только тогда, когда одновременно истинны обе входные переменные.

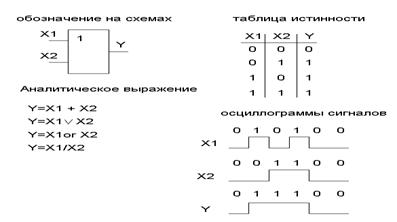

Логическое сложение «ИЛИ»

- логическое сложение двух переменных X1 и X2 это логическая функция Y, которая истинна, когда хотя бы одна из входящих переменных истинна.

-

Логические функции часто характеризуют таблицей истинности.

Таблица истинности – это таблица соответствия всех возможных комбинаций входных логических переменных и соответствующей им выходной логической функции.

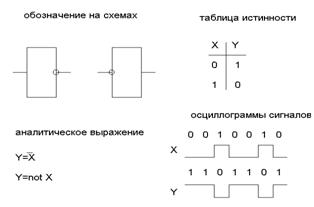

Логическое отрицание «НЕ»

- логическое отрицание переменной Х это логическая функция Y, которая истинна только тогда, когда Х ложно и, наоборот, ложна тогда, когда Х истинна.

Три рассмотренные функции позволяют реализовать любую логическую зависимость. На основе их строятся более сложные логические функции.

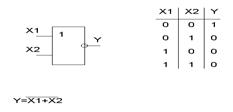

Функция «ИЛИ-НЕ» (операция стрелка Пирса)

- функция обратная к «ИЛИ»

Функция «И-НЕ» - (операция штрих Шеффера)

- функция обратная к «И»

-

Функционально полная система логических элементов – это такой набор элементов, используя который можно реализовать любую сколь угодно сложную логическую функцию.

Ввиду того, что любая логическая функция представляет собой комбинацию простейших функций «И», «ИЛИ» и «НЕ», то набор этих элементов является функционально полным.

То же самое можно сказать и об элементах, реализующих функции «И-НЕ»и «ИЛИ-НЕ». Каждый из них является функционально полным, то есть в любом из них может быть реализована любая логическая функция.

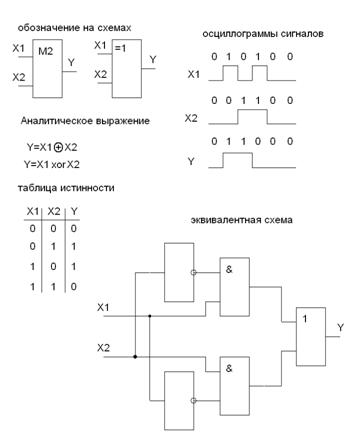

Исключающее «ИЛИ» (сумма по модулю 2 – операция XOR)

- суммой по модулю 2 двух переменных X1 и X2 является логическая функция Y, которая истинна только тогда, когда одна из входных переменных истинна, а другая ложна.

(Эта функция реализует операцию неравнозначности).

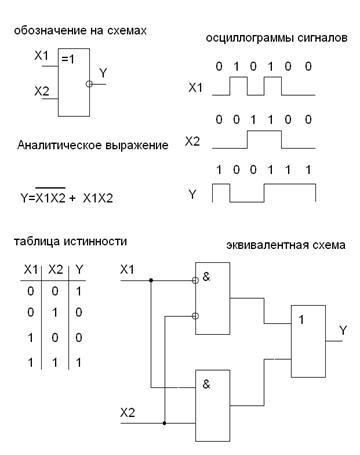

Схема равнозначности

- логическая функция Y истинна, только тогда, когда обе входные переменные X1 и X2 равнозначны, то есть либо одновременно «ложны», либо одновременно «истинны»

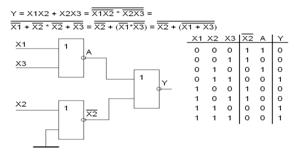

Синтез логических схем

«Отличие науки от искусства заключается в том, что наука базируется на формализованных методах решения однотипных задач».

Множество состояний комбинационного устройства может быть охарактеризовано функцией алгебры логики (ФАЛ), которая описывает входные и выходные состояния этого устройства.

ФАЛ может быть задана в виде:

- словесного описания;

- таблицы истинности;

- числовой последовательности;

- аналитического выражения.

Пример: Функция алгебры логики задана в виде числовой последовательности:

Y={3,6,7}#10x1x2x3

Эта запись означает:Y принимает значение «1» при подаче на входы трехвходовой комбинационной схемы двоичных эквивалентов десятичных чисел «3», «6» и «7».

Таблица истинности такой функции выглядит так:

| X1 | X2 | X3 | Y |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

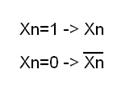

Запишем логическое выражение для этой функции:

Для этого для каждого состояния «Y=1» запишем логическое произведение переменных по правилу если Xn=1, то в произведение запишем его прямое значение; если Xn=0, то в произведение запишем его инверсное значение.

Записанные логические произведения объединим логической суммой.

Полученное выражение будет иметь следующий вид:

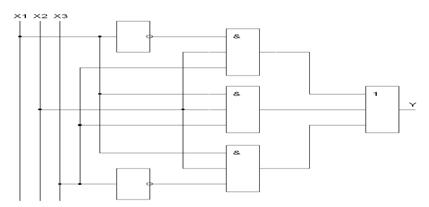

![]()

Для схемотехнической реализации полученной логической функции потребуется три трехвходовых схемы И, одна трехвходовая схема ИЛИ и два инвертора НЕ.

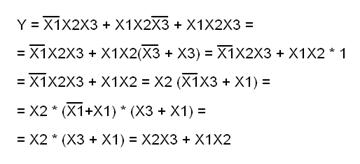

Правила алгебры логики позволяют преобразовать полученное выражение к более простому и удобному виду:

Для практической реализации этой функции потребуется два двухвходовых элемента «И» и один двухвходовой элемент «ИЛИ».

Для практической реализации этой функции потребуется два двухвходовых элемента «И» и один двухвходовой элемент «ИЛИ».

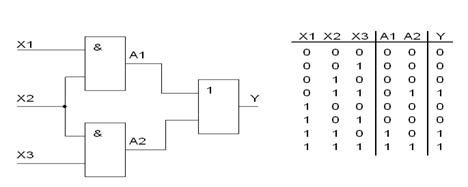

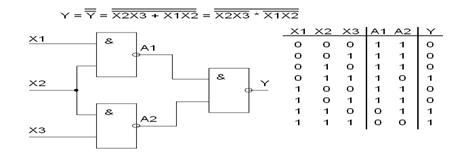

Применив правило де-Моргана, можно преобразовать выражение к виду, удобному для реализации схемы на других элементах.

Допустим, что для построения схемы мы можем использовать только элементы И-НЕ, тогда:

Допустим, что мы можем использовать только элементы ИЛИ-НЕ, тогда:

Комбинационные и последовательностные устройства

Все устройства, оперирующие с двоичной (дискретной) информацией, подразделяются на два больших класса: комбинационные схемы (дискретные автоматы без памяти) и последовательностные устройства (дискретные автоматы с памятью).

Комбинационные схемы.

Комбинационной схемой или логическим устройством называют такое устройство, у которого сигналы на выходах в любой момент времени однозначно определяются сочетанием сигналов на входах и не зависят от предыдущих состояний данного устройства.

Схемным признаком таких устройств служит отсутствие цепей обратной связи, то есть замкнутых петель для прохождения сигналов с выходов устройства на его входы.

Примером комбинационных схем могут служить отдельные логические элементы, наборы электронных ключей, шифраторы, дешифраторы, мультиплексоры, демультиплексоры и большинство арифметических устройств: сумматоры, полусумматоры, перемножители и т.д.

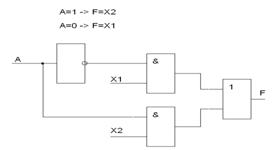

Мультиплексоры.

Назначение мультиплексора – коммутация в желаемом порядке информации, поступающей с нескольких входных линий на одну выходную.

С помощью мультиплексора осуществляется разделение во времени информации, поступающей по разным каналам. Мультиплексор можно рассматривать как бесконтактный многопозиционный переключатель.

Мультиплексор «два к одному».

Для переключения входных сигналов используется один внешний сигнал.

Мультиплексоры обладают двумя группами входов и одним, реже двумя – взаимодополняющими выходами.

Одни входы информационные, а другие – управляющие. К управляющим относятся адресные и разрешающие (стробирующие) входы.

Набор сигналов на адресных входах определяет конкретный информационный вход, который будет соединён с выходом.

Разрешающий вход управляет одновременно всеми информационными входами, независимо от состояния адресных входов. Запрещающий сигнал на этом входе блокирует действие всего устройства. Наличие разрешающего входа расширяет функциональные возможности мультиплексора, позволяя синхронизировать его работу с работой других узлов цифровой схемы.

Мультиплексор «четыре к одному».

Содержит четыре информационных входа D0 .. D3, два адресных входа A и B и разрешающий вход V.

Двоичные числа, характеризующие сигналы на входах A и B, эквивалентны индексу задействованного информационного входа.

Таблица истинности.

| Входы | Выход F | ||

| V | A | B | |

| 0 | 0 | 0 | D0 |

| 0 | 0 | 1 | D1 |

| 0 | 1 | 0 | D2 |

| 0 | 1 | 1 | D3 |

| 1 | X | X | 0 |

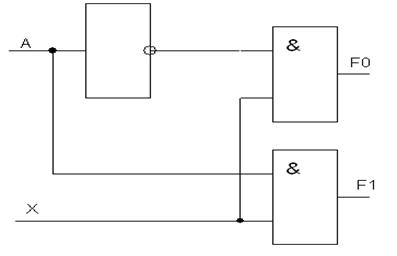

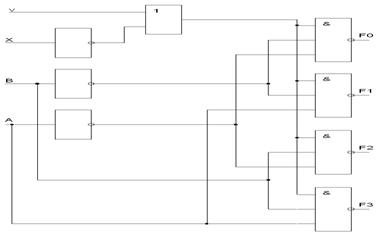

Демультиплексоры.

Демультиплексоры в функциональном отношении противоположны мультплексорам.

Сигналы с одного информационного входа распределяются в желаемой последовательности по нескольким выходам. Выбор нужной выходной линии обеспечивается кодом на адресных входах.

При m адресных входах демультиплексор может иметь до 2m выходов.

Демультиплексоры «один к двум».

Вход X – информационный.

Вход А – адресный, потенциал на этом входе определяет, к какому из выходов будет подключен вход Х.

A=0 -> F0=X

A=1 -> F1=X

Демультиплексор «один к четырем»

А и В – адресные входы;

Х – информационный вход;

V – разрешающий вход.

| Входы | Выходы | ||||||

| B | A | X | V | F0 | F1 | F2 | F3 |

| 0 | 0 | 0/1 | 0 | X | 1 | 1 | 1 |

| 0 | 1 | 0/1 | 0 | 1 | X | 1 | 1 |

| 1 | 0 | 0/1 | 0 | 1 | 1 | X | 1 |

| 1 | 1 | 0/1 | 0 | 1 | 1 | 1 | X |

| 0 | 0 | 0/1 | 1 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0/1 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0/1 | 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0/1 | 1 | 1 | 1 | 1 | 0 |

Шифраторы и дешифраторы

При вводе данных в ЭВМ производится их преобразование из одной системы счисления в другую. Например, из десятичной системы в двоичную систему. При выводе результатов вычислений может понадобиться преобразовать данные обратно. Эти операции выполняют специальные устройства: шифраторы и дешифраторы.

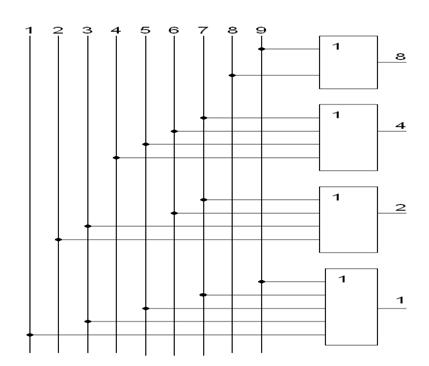

Шифратор – это комбинационная схема, которая из сигналов, полученных по m входным линиям, генерирует код на n выходных линиях.

Элементарный шифратор можно построить на элементах ИЛИ. Если шифратор имеет m=2n входов, то он может иметь n выходов. Такой шифратор называется полным.

Десятично-двоичный шифратор.

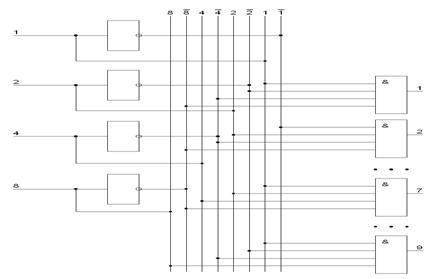

Дешифратор – это комбинационная схема, которая может быть построена на элементах И, и которая имеет n входов и 2n выходов (но может быть выходов и меньше). Дешифратор осуществляет преобразование комбинации сигналов на его входах, в сигнал на одном из его выходов. То есть определённая комбинация входных сигналов соответствует активному состоянию одного из выходов дешифратора.

Двоично-десятичный дешифратор.

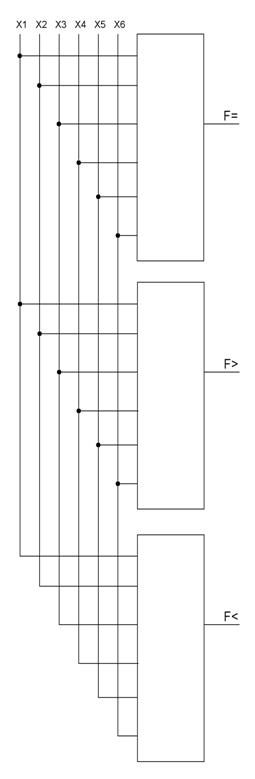

Цифровые компараторы

(Схемы сравнения кодов).

- комбинационные логические устройства, предназначенные для сравнения чисел, представленных в виде двоичных кодов.

Число входов компаратора определяется разрядностью сравниваемых кодов. На выходах компаратора обычно формируются три сигнала:

F= - равенство кодов;

F> - числовой эквивалент первого кода больше числового эквивалента второго кода;

F< - числовой эквивалент первого кода меньше числового эквивалента второго кода;

Работу одноразрядного компаратора поясняет таблица истинности:

| Входы | Выходы | |||

| X1 | X2 | F= | F> | F< |

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 |

Логические выражения для выходов будут иметь вид:

F= = X1’X2’+X1X2

F> = X1X2’

F< = X1’X2

Выражение для F= имеет в цифровой схемотехнике большое значение и называется Исключающее ИЛИ-НЕ и является инверсией для другой функции, которая называется «Исключающее ИЛИ», «сумма по модулю 2» или «операция XOR».

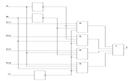

Многоразрядные схемы сравнения

На практике гораздо чаще приходится сталкиваться с задачей построения схем для сравнения многоразрядных двоичных кодов. Такая схема может быть построена на основе поразрядных схем сравнения, но может быть синтезирована и как специальная структура.

Рассмотрим подробнее второй способ. Для его реализации нужно записать таблицу истинности для необходимых входных кодов и по этой таблице составить аналитические выражения для каждого из выходов. Полученные выражения можно попробовать собрать в комбинации и упростить.

Пример: построение компаратора для неполной кодовой последовательности.

Построить схему сравнения кодов для чисел {3,6,7}

Составим таблицу истинности, описывающую состояния данного устройства:

| Входы первого числа | Входы второго числа | Выходы компаратора | ||||||

| Х1 | Х2 | Х3 | Х4 | Х5 | Х6 | F= | F> | F< |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 | |||

| 1 | 1 | 1 | 0 | 0 | 1 | |||

| 1 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | |||

| 1 | 1 | 1 | 0 | 0 | 1 | |||

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | |||

| 1 | 1 | 1 | 1 | 0 | 0 | |||

F= = X1’X2Х3Х4’X5X6 + X1X2X3’X4X5X6’ + X1X2X3X4X5X6

F= = X2Х3X5X6 ( X1’X4’ + X1X4 ) + X1X2X4X5 ( X3’X6’ + X3X6 )

F= = X2X5 [ X3X6 ( X1’X4’ + X1X4 ) + X1X4 ( X3’X6’ + X3X6 ) ]

F> = X1X2X3’X4’X5X6 + X1X2X3X4’X5X6 + X1X2X3X4X5X6’

F> = X1X2X5 ( X3’X4’X6 + X3X4’X6 + X3X4X6’ )

F> = X1X2X5 ( X4’X6 + X3X4’X6 )

F< = X1’X2X3X4X5X6’ + X1’X2X3X4X5X6 + X1X2X3’X4X5X6

F< = X2X4X5 ( X1’X3X6’ + X1’X3X6 + X1X3’X6 )

F< = X2X4X5 ( X1’X3 + X1X3’X6 )

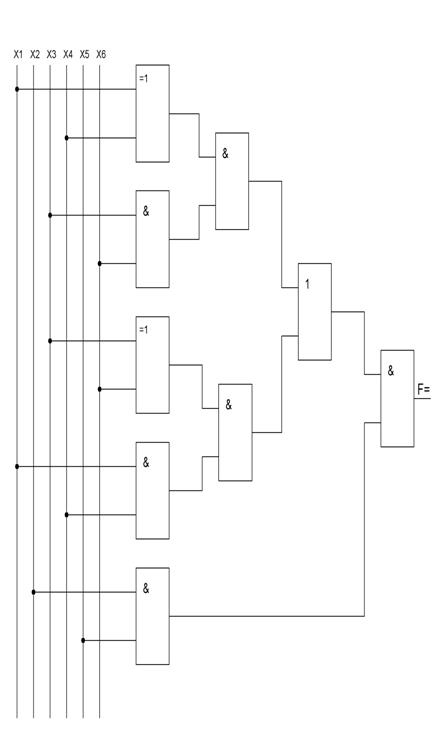

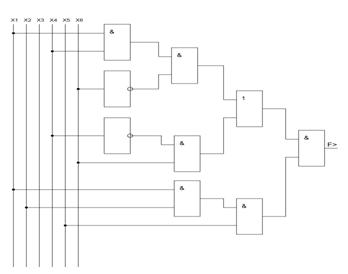

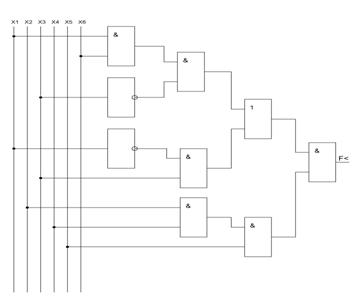

В итоге мы получим сложное устройство, состоящее из трёх комбинационных схем, которое в общем виде можно изобразить так:

Каждую из отдельных схем в составе устройства можно изобразить отдельно.

Формирователь выхода «Равенство кодов»

Формирователь выхода «Больше»

Формирователь выхода «Меньше».

Арифметические устройства

Другой класс приборов, используемых в дискретной технике предназначен для выполнения арифметических действий с двоичными числами: сложения, вычитания, умножения, деления.

К арифметическим устройствам относятся также схемы, выполняющие специальные арифметические операции, такие как выявление чётности заданных чисел и сравнение двух чисел.

Особенность арифметических устройств состоит в том, что сигналам приписываются не логические, а арифметические значения «1» и «0» и действия над ними подчиняются законам двоичной арифметики.

Основы двоичной арифметики.

Двоичное сложение.

Сложение в DEC:

| 1 | 1 | 2 | 5 | 6 | |

| + | + | ||||

| 1 | 9 | 7 | 7 | ||

| 3 | 0 | 3 | 3 | 3 |

Таблица сложения в BIN:

0+0=0 0+1=1 1+0=1 1+1=10

При сложении двух единиц получается ноль и единица переноса в более старший разряд.

Примеры двоичного сложения:

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | ||||

| + | + | + | + | |||||||||||

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | |||||||

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |

Сложение в ЭВМ выполняют специальные устройства – сумматоры.

Двоичное умножение.

Таблица умножения в BIN:

0*0=0 0*1=0 1*0=0 1*1=1

Примеры умножения в двоичной системе

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | ||||||

| * | * | * | * | |||||||||||||

| 1 | 1 | 1 | 1 | 1 | 0 | |||||||||||

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | ||||||

| + | + | |||||||||||||||

| 1 | 1 | 0 | 1 | 1 | 1 | |||||||||||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 0 |

Как видно из примеров операция умножения может быть заменена операциями сложения со сдвигом влево.

Число дополнение.

Если в двоичном числе все нули заменить на единицы, а все единицы на нули (инвертировать число), и прибавить единицу, то получится число дополнение к начальному числу.

Пример: дано число: 10011 Инверпсия: 01100 Дополнение: 01101

Двоичное вычитание.

Вычитание двоичных чисел в ЭВМ может быть заменено операцией сложения первого числа с числом дополнением вычитаемого с учётом старшего разряда результата.

Пример:

10-5=5 1010-101=101

Алгоритм вычитания:

1. Определить дополнение вычитаемого;

2. Сложить полученное дополнение с уменьшаемым;

3. Из полученной суммы вычесть число, состоящее из единицы в старшем разряде и нулей в остальных разрядах.

Двоичное деление.

Двоичное деление может быть заменено многократным сложением со сдвигом вправо.

Поскольку числа в любой системе счисления могут быть представлены в двоичной системе, то операции над ними могут быть произведены в двоичных вычислительных устройствах.

Сумматоры

Сумматоры – функциональные узлы, выполняющие операцию сложения чисел. В устройствах цифровой техники суммирование осуществляется в двоичном или, реже, в двоично-десятичном коде.

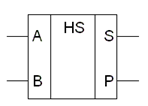

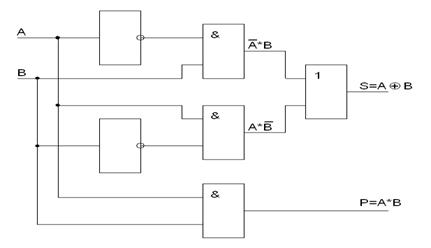

Простейшим суммирующим элементом является полусумматор. Он имеет два входа A и B для двух слагаемых и два выхода: S – сумма и P – перенос.

Таблица истинности полусумматора

| Входы | Выходы | ||

| A | B | P | S |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

Логическая структура полусумматора такова, что состояние выхода S отображает бит суммы , а выход P – бит переноса.

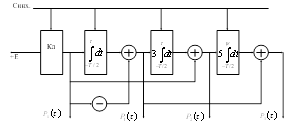

Полный сумматор.

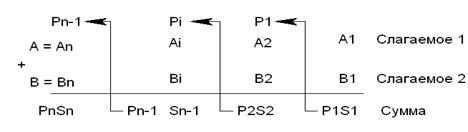

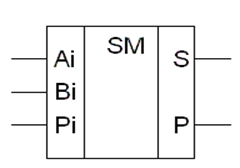

Процедуру сложения двух n-разрядных двоичных чисел можно представить следующим образом.

1. Сложение цифр A1 и B1 младшего разряда даёт бит суммы S1 и бит переноса P1.

2. В следующем (втором) разряде происходит сложение цифр P1, A2 и B2, которые формируют сумму S2 и перенос P2.

3. Операция длится до тех пор, пока не будет сложена каждая пара цифр во всех разрядах. Результатом сложения будет число S=PnSn…S1, где Pn и Si отображают 1 или 0, полученные в результате поразрядного сложения.

Устройство суммирования двух многоразрядных чисел должно иметь, три входа: два для слагаемых Ai и Bi и один для сигнала переноса Pi-1 из предыдущего разряда.

К155ИМ3 четырёхразрядный сумматор.

Вычитатели (субтракторы) – схемы, выполняющие вычитание одного двоичного числа из другого.

В цифровой схемотехнике операции вычитания обычно заменяются сложением уменьшаемого с вычитаемым, представленным в дополнительном коде.

Отдельные микросхемы вычитателей не выпускаются, и могут быть построены на основе сумматоров и преобразователей кодов.

Умножители – умножение двоичных чисел сводится к суммированию множимого, сдвинутого в каждом слагаемом на необходимое количество разрядов. Поэтому умножитель можно построить на сумматорах и сдвигающих регистрах.

В микросхемном исполнении выпускаются устройства умножения для малоразрядных чисел. Например, К564ИП5, К531ИК1П, К531ИК2П

Последовательностные устройства

Последовательностные устройства обладают памятью.

Память – это свойство системы достаточно долго сохранять своё состояние.

При анализе схем последовательностных устройств следует иметь в виду, что при изменении сигналов на входах, состояние выходов меняется с учётом текущего состояния устройства.

Последовательностные устройства собираются на основе комбинационных схем.

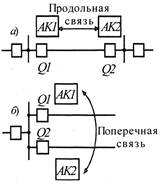

Признаком последовательностного устройства является наличие в схеме обратных связей.

Простейшими примерами последовательностных устройств являются триггеры. К более сложным устройствам относятся счётчики, регистры, запоминающие устройства.

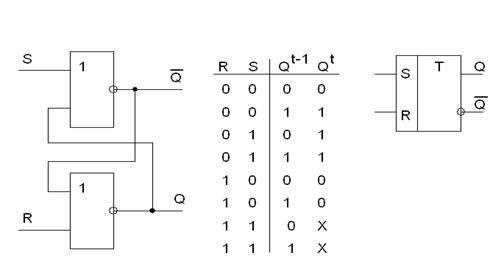

Триггеры.

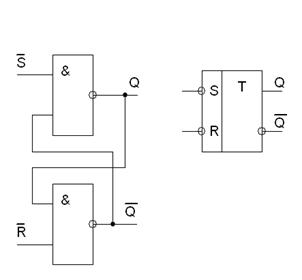

RS-триггер с разделённой установкой в 0 и 1.

Такой триггер имеет два входа R и S. При комбинации на входах:

S=1; R=0 - выход Q=1

S=0; R=1 - Q=0

S=0; R=0 - триггер сохраняет прежнее состояние

S=1; R=1 - состояние неопределённости.

RS-триггер - это элементарный цифровой автомат с двумя устойчивыми состояниями.

Аналогичная схема может быть построена на элементах И-НЕ, но она будет иметь некоторые особенности pаботы.

Асинхронный RS-триггер с инверсными входами.

RS-триггер с инверсными входами изменяет своё состояние под воздействием инверсных значений входных сигналов.

В режиме хранения информации необходимо поддерживать на входах R и S потенциалы: 0 для триггера с прямыми входами и 1 для триггера с инверсными входами.

Синхронный тактируемый RS-триггер.

Синхронный или тактируемый RS-триггер имеет синхровход С, который при С=1 разрешает переключение, а при С=0 триггер не реагирует на сигналы по входам R и S.

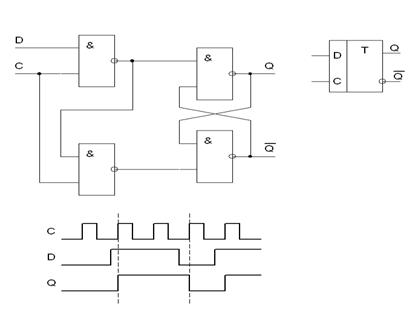

D-триггер задержки.

D-триггер задержки имеет один информационный вход D и вход синхроимпульсов C.

Основное назначение D-триггера это задержка и хранение сигнала, поданного на вход D до прихода следующего синхроимпульса на входе С.

Или иными словами, одноступенчатый D-триггер задерживает распространение входного сигнала на время паузы между синхронизирующими сигналами.

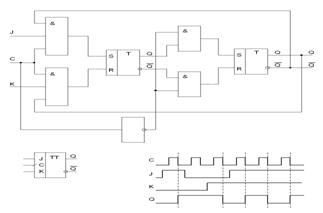

Универсальный JK-триггер.

JK-триггер работает по принципу RS-триггера, но для него комбинация J=1, K=1 не является запрещённой. При такой комбинации сигналов на входах, этот триггер изменяет своё состояние на противоположное с каждым следующим синхроимпульсом.

JK-триггер обычно реализуется по двухступенчатой схеме. При С=1 входная функция записывается в первый триггер, при С=0 входная функция из первого триггера переписывается во второй триггер.

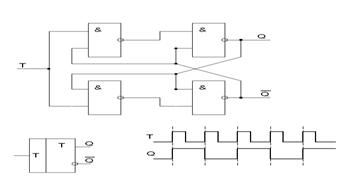

Счётный T-триггер.

T-триггер изменяет своё состояние с приходом каждого входного импульса.

Такой триггер может быть реализован на основе JK-триггера при J=1 и K=1. В этом случае сигнал на входе С становится тактовым сигналом Т и JK-триггер начинает работать как счётный Т-триггер.

Счетчики.

Счетчик – это узел ЭВМ, подсчитывающий количество электрических импульсов на его входе.

Счётчики строятся на основе JK-триггеров и счётных D-триггеров.

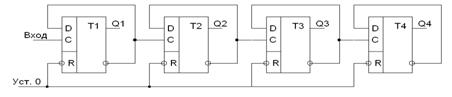

При построении счётчика на основе D-триггеров счётные входы триггеров соединяют с инверсными выходами предыдущих триггеров.

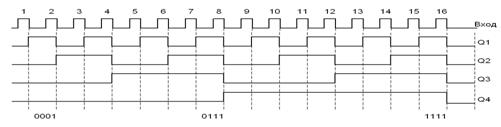

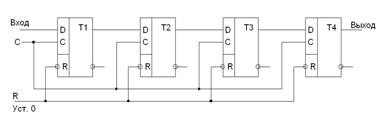

Диаграммы двоичного четырёхразрядного счётчика на D-триггерах.

Как видно, каждый последующий триггер осуществляет деление частоты входных, для него, импульсов на два. По этой причине счётчики часто используют как делители частоты импульсов.

Состояние счётчика (количество поступивших на его вход импульсов после установки в «0») однозначно определяется состоянием его триггеров.

В частности, для четырехразрядного счётчика состояние q может быть определено по формуле:

q=p1Q1+p2Q2+p3Q3+p4Q4

где: Qi = «0» или «1» – состояние I-го триггера;

Pi = 2i-1 вес I-го разряда счётчика.

Счётчик может быть построен так, что работает в весовом коде 1-2-4-8, а может быть построен так, что его весовой код будет другим.

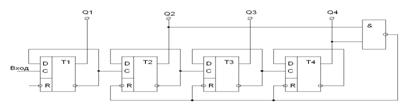

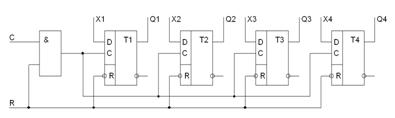

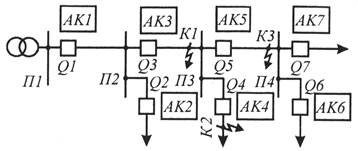

Счётчик с коэффициентом пересчёта отличным от 2n.

Принцип построения счётчика с чётным коэффициентом счёта отличным от 2n рассмотрим на примере десятичного счётчика.

Для реализации этого принципа необходимо чтобы при достижении счётчиком состояния 10, был подан импульс установки всех его разрядов в нуль, после чего счётчик начнёт счёт сначала. Число 10 в двоичной системе выражается как 1010bin , то есть триггеры 4-х разрядного счётчика должны при достижении состояния Q1=0, Q2=1, Q3=0, Q4=1 активизировать схему установки всех разрядов в нуль.

Проще всего объединить сигналы с выходов Q4 и Q2 с помощью схемы «И-НЕ» и подать сигнал на входы R для установки триггеров в нуль.

Вход R триггера T1 не обязательно связывать с выходом элемента «И-НЕ», так как в момент сброса триггера Т1 и так находится в нулевом состоянии. Аналогично может быть построен любой счётчик с любым коэффициентом пересчёта.

Регистры.

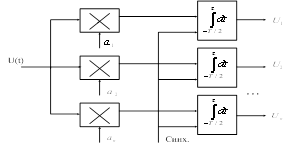

Регистр – узел ЭВМ, предназначенный для временного хранения информации, а также для её преобразования.

Основу регистров составляют триггерные схемы.

Количество триггеров в регистре определяет разрядность записываемых и хранимых в регистре слов данных. При этом, каждый триггер используется для записи одного разряда слова.

4-х разрядный параллельный регистр.

Все разряды двоичного числа вводятся одновременно по входам X1 .. X4.

На вход R подаётся сигнал, высокий уровень этого сигнала разрешает подачу тактового импульса на вход С. Низкий уровень сигнала на входе R устанавливать триггеры регистра в нулевое состояние (очистка регистра).

На входы X1 .. X4 поступают разряды двоичного числа, которые при наличии тактового сигнала на входе С одновременно вводятся в регистр.

Регистр предназначенный для последовательного ввода информации (поразрядно), называют последовательным или сдвиговым, так как последовательный ввод связан с перемещением содержимого регистра.

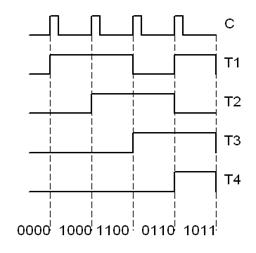

4-х разрядный последовательный регистр

Для полного ввода и вывода 4-х разрядного числа, потребуется 4 тактовые импульса на входе С.

Например, наш необходимо записать в регистр число 1011bin = 11dec .

Числу 1011 соответствует такая последовательность импульсов подаваемых на вход: регистра.

Одновременно с ними на вход С должны подаваться тактовые импульсы и состояние регистров триггера будет изменяться так:

При последовательном считывании данных, на вход С нужно подавать 4 тактовые импульса и считывать, поразрядно, значения введенного слова на выходе. При этом состояние триггеров будет изменяться так:

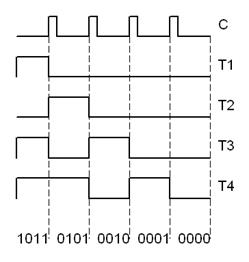

Организация памяти в системе

Запоминающие устройства предназначены для сохранения информации и обмена ею с другими устройствами.

По функциональному назначению микросхемы памяти делятся на два вида: оперативное запоминающее устройство (ОЗУ) и постоянное запоминающее устройство (ПЗУ).

ОЗУ (RAM – Random Access Mamory) – предназначены для кратковременного хранения информации.

В процессе работы вычислительной системы информация в ОЗУ может изменяться. ОЗУ работает в режимах записи, чтения и хранения информации. После отключения питания информация в ОЗУ стирается.

Оперативная память подразделяется на два типа: с динамической (Dynamic RAM, DRAM) и статической (Static RAM, SRAM) выборкой.

В динамической памяти значение бита информации в ячейке определяется наличием или отсутствием заряда на миниатюрном конденсаторе, который управляется 1-2 транзисторами.

В статической памяти применены специальные элементы триггеры, имеющие два устойчивых состояния, реализованные на 4-6 транзисторах.

Быстродействие статической памяти SRAM выше, чем быстродействие динамической памяти DRAM, но статическая память SRAM значительно дороже из-за большего числа транзисторов на ячейку'.

(Обычно модули памяти DRAM применяют в оперативной и видеопамяти, а модули SRAM - в качестве быстрой буферной кэш-памяти в процессорах, на системных платах, на жестких дисках.)

Содержимое динамической памяти остаётся неизменным в течение очень короткого промежутка времени, поэтому она должна периодически обновляться. Запоминающим элементом динамической памяти является конденсатор, который может находиться в заряженном или разряженном состоянии. Если конденсатор заряжен, то в ячейку записана логическая единица (1), если разряжен - логический ноль (0). В идеальном конденсаторе заряд может сохраняться сколь угодно долго, но в реальном конденсаторе существует ток утечки, поэтому информация, записанная в динамическую память, со временем будет утрачена, так как конденсаторы ячеек памяти полностью разрядятся. Процесс обновления динамической памяти называется регенерацией памяти (Refresh).

Процессор имеет доступ к данным, находящимся в динамической памяти только в течение циклов, свободных от регенерации. Специальная схема через определённые промежутки времени (например, каждые 2 мс) осуществляет чтение и запись всех ячеек памяти. В эти моменты процессор находится в состоянии ожидания. Автоматическая регенерация памяти происходит также при выполнении каждой операции чтения или записи ячейки памяти.

Ячейки в динамической памяти образуют матрицу, состоящую из строк и столбцов. При считывании данных содержимое одной строки целиком переносится в буфер, который реализован на элементах статической памяти. После этого в строке считывается значение нужной ячейки. При считывании информации из ячеек памяти, происходит её разрушение, поэтому производится перезапись считанной информации, т.е. содержимое буфера вновь записывается в прежнюю строку динамической памяти.

Необходимость периодически обновлять заряд на ячейках динамической памяти приводит к чрезмерному потреблению энергии, что в сою очередь, приводит к разряду батарей ноутбуков, и мобильных телефонов.

ПЗУ (ROM – Read Only Memory) – содержит информацию, которая не изменяется в течение длительного времени во время эксплуатации цифрового устройства.

ПЗУ обычно работает в режимах считывания и хранения информации.

ПЗУ используется для сохранения управляющих программ, стандартных программ решения типовых задач, табличных данных (BIOS) и т.д.

Микросхемы ПЗУ разделяются на те, в которые информация записывается одноразово – то есть, однократно программируемые, и те, в которые информация может записываться многократно – перепрограммируемые.

ROM - это память, доступная только для чтения. Используется в BIOS для хранения постоянных данных. Она не требует энергопитания, т. е., информация в таких микросхемах не стирается, даже если выключить питание компьютера.

Отличие оперативной памяти от постоянной памяти в том, что информация хранится в ней временно, только при включении питания. Но ОЗУ обеспечивает более высокую скорость доступа к данным.

Кроме этого, в современных вычислительных системах существуют специальные виды памяти:

Сверхоперативное ЗУ (СОЗУ) – как правило, встраивается в кристалл процессора и называется кэш (cache), имеет быстродействие, соизмеримое с быстротой процессора, и служит для хранения данных, необходимых для выполнения некоторой текущей последовательности команд программы.

Внешние ЗУ (ВЗУ) – предназначены для хранения больших объёмов информации, но при этом обладают сравнительно низкой скоростью чтения-записи. Обычно выполняются на основе устройств с магнитной записью информации, но могут быть выполнены и на микросхемах, например, на флэш-картах. В этих носителях используются элементы на основе транзисторов с накоплением объёмного заряда. Стирание информации в них выполняется не по-битово, а большими блоками. Это позволяет упростить схемы запоминающих устройств и схемы управления, а значит снизить стоимость системы.

Матричная модель запоминающего устройства.

Микросхемы большой информационной ёмкости реализуют в виде матриц, запоминающие элементы расположены в узлах матрицы. Каждый элемент связан с одной вертикальной и одной горизонтальной адресными шинами.

Основные параметры микросхем запоминающих устройств.

Информационная ёмкость – максимально возможный объём информации, который сохраняется в микросхеме. Рассчитывается в единицах информации – битах, или в словах данных – байтах. Бит сохраняется одним элементом памяти, слово сохраняется в ячейке из группы элементов в 8 бит. Информационная ёмкость современных микросхем измеряется в тысячах (кило), миллионах (мега) и миллиардах (гига) единиц.

Организация запоминающего устройства – может быть различной, поэтому микросхемы одинаковой информационной ёмкости могут иметь различную организацию. Например, существуют микросхемы с организацией 8к*1 и 1к*8. они имеют одинаковую информационную ёмкость 8192 бита, но различную структуру.

Быстродействие микросхем памяти определяется временем чтения, временем записи и продолжительностью цикла чтение-запись.

Время чтения – это интервал времени между моментами появления сигнала чтения на управляющем входе микросхемы и сигналом данных на выходе микросхемы.

Время записи – интервал времени с момента появления сигнала записи на соответствующем управляющем входе и до того момента, когда запоминающие элементы устанавливаются в состояние, соответствующее состоянию записываемых данных.

Длительность цикла «чтение» - «запись» - минимально допустимый интервал времени между режимами чтения и записи, которые наступают последовательно друг за другом.

АЛУ (Арифметическое Логическое Устройство) – устройство, выполняющее в соответствии с кодом на входах арифметические и логические преобразования двоичной информации.

По сравнению с устройствами, работающими по жёсткой, наперёд заданной логической функции, АЛУ представляют собой устройства более высокого класса.

В общем виде операндами АЛУ могут быть: целые и дробные числа, десятичные числа в специальных кодах, алфавитно-цифровые коды, группы однобитовых переменных и т.д.

При построении микропроцессорных систем АЛУ используется в сочетании с регистрами, оперативными запоминающими устройствами и другими узлами.

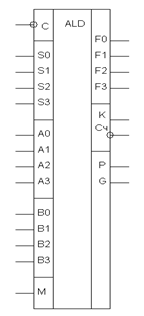

К155ИП3

Микросхема предназначена для выполнения действий с двумя четырёхразрядными двоичными числами: A=A3A2A1A0 и B=B3B2B1B0.

Вид операции, выполняемый этой микросхемой над данными, задаётся 5-ти разрядным кодом на входах M и S3S2S1S0.

Всего АЛУ К155ИП3 способно выполнить 32 операции, из них 16 логических и 16 арифметических.

Например:

- код M=1 и Sx=0000 приводит к выполнению операции инвертирования числа А;

- код M=1 и Sx=1011 – логическое умножение A и B;

- код М=1 и Sx=1110 – логическое сложение A и B;

- код M=1 и Sx=0110 – операция XOR для А и В;

- код М=0 и Sx=1011 – арифметическое умножение А и В и так далее

(подробнее: «Справочник по схемотехнике для радиолюбителей» под редакцией к.т.н. В.Н. Боровского, издательство «Техника», Киев 1987 год, страница 328 - 329).

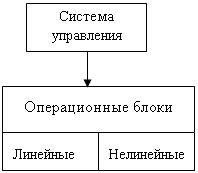

Возможна блочная и многофункциональная структура АЛУ.

В блочном АЛУ содержится набор устройств для выполнения отдельных видов операций.

В многофункциональном АЛУ все операции над любыми числами выполняются в одном устройстве. В составе АЛУ могут быть, например, такие блоки: блок десятичной арифметики, матрица умножения для целых чисел, устройство сложения/вычитания для чисел с плавающей точкой, устройство для логических преобразований и т. д.

Внутреннее построение микропроцессора

Рассмотрим упрощённую схему микропроцессора. (См. рисунок ниже.) Процессор состоит из трёх основных блоков: АЛУ, регистров и устройства управления. Для передачи данных между этими блоками используется внутренняя шина данных.

Внутренняя шина данных:

Ø Каждый операционный блок МП подключен к внутренней шине данных, однако воспользоваться ею может только после получения соответствующего сигнала от схем управления.

Ø Большинство узлов в составе МП могут посылать и принимать данные с внутренней шины данных.

Схемы управления:

Ø Поддерживают требуемую последовательность функций всех звеньев МП. Одна из которых – декодирование команды выдача сигналов для её выполнения.

Ø Линии управления соединяют схемы управления со всеми составляющими МП, а также внешними по отношению к процессору блоками в составе ЭВМ.

Ø Соединены линией связи с тактовым генератором для синхронизации во времени работы отдельных частей МП. Также управляют процессами прерываний.

АЛУ:

Ø Выполняет арифметические и логические операции над данными, изменяет данные, выполняет все виды обработки данных, то есть используется тогда, когда необходимо изменить или проверить значение слова данных.

Ø Функции АЛУ определяют архитектуру МП в целом, так как в АЛУ на аппаратном уровне «зашиты» все возможные для данного процессора команды по обработке данных.

Ø Оперирует одним или двумя словами данных в зависимости от вида выполняемой операции.

Ø Входные и выходные порты АЛУ – это входы и выходы схем «вычислителя». Через эти порты идёт обмен данными АЛУ и других блоков МП.

Регистры:

Ø Основное назначение – временное хранение данных на период выполнения какой-либо операции.

Ø Некоторые регистры имеют специальное назначение, другие являются многоцелевыми.

Регистр Слова Состояния Процессора:

Ø Предназначен для хранения результатов некоторых проверок, осуществляемых в процессе выполнения программы, что позволяет делать переходы и строить программы с разветвляющейся структурой.

Ø Позволяет организовывать работу МП так, чтобы при определённых условиях менялся порядок выполнения команд.

Буферные регистры АЛУ:

Ø Подключены к входным портам АЛУ.

Ø Необходимость связана с отсутствием в АЛУ своих запоминающих устройств, так как АЛУ представляет собой набор комбинационных схем.

Ø Недоступны программисту при написании программ управления процессором.

Блок регистров общего назначения (РОН):

Ø Содержит многоцелевые регистры, именуемые регистрами общего назначения.

Ø Предоставлены в распоряжение программиста при написании программ.

Регистр аккумулятор:

Ø Главный регистр МП при различных манипуляциях с данными.

Ø Большинство арифметических и логических операций выполняется с использованием АЛУ и аккумулятора.

Ø Любая из операций над двумя словами данных предполагает размещение одного из них в аккумуляторе, а другого в памяти или ещё в каком-либо регистре.

Ø Результат выполненной операции АЛУ тоже обычно размещает в аккумуляторе.

Ø МП может выполнять некоторые операции непосредственно в аккумуляторе, например инвертирование слова данных.

Ø Количество разрядов аккумулятора соответствует длине слова данных МП, но может быть и кратной этой длине. (Например, аккумулятор двойной длины.)

Ø Некоторые МП имеют не один, а группу аккумуляторов, и в этом случае в наборе команд такого процессора предусмотрены команды обращения к каждому отдельному аккумулятору.

Счётчик команд:

Ø Следит за тем, какая команда будет выполнена следующей.

Ø Может получать данные об адресах программы из любого блока МП, подключенного к внутренней шине данных.

Ø При начале работы, по команде начальной загрузки, в счётчик команд загружается адрес первой команды программы начальной загрузки, заданный проектировщиком ЭВМ.

Ø Перед запуском программы пользователя начальный адрес этой программы загружается в счётчик команд. После выполнения этой команды счётчик получает соответствующее приращение.

Регистр адреса памяти:

Ø Указывает адрес области памяти, которая подлежит использованию.

Ø Выход подключен к адресной шине.

Ø Вход подключен к внутренней шине данных и может загружаться из различных источников.

Регистр команд:

Ø Предназначен для хранения текущей исполняемой команды.

Ø Только принимает данные с внутренней шины данных.

Ø Выход является частью дешифратора команд.

Ø Число разрядов иногда совпадает с длинной слова данных, а иногда нет. (Если длина регистра меньше, то команда обрабатывается по частям.)

Похожие работы

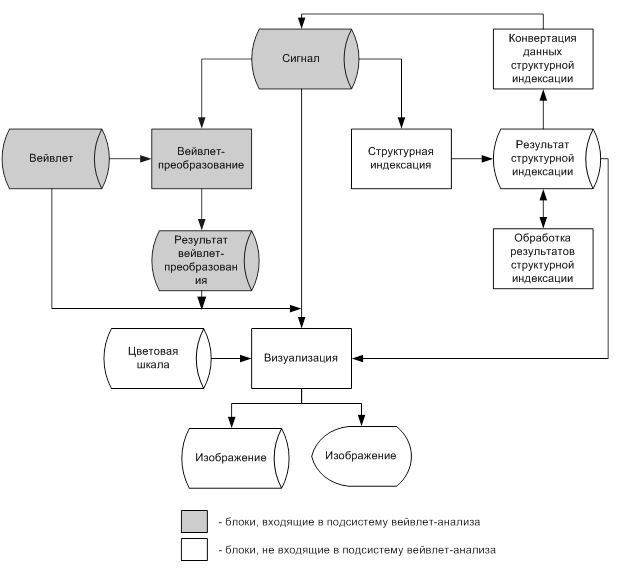

... для выявления нестационарных составляющих сигнала, что крайне полезно при подборе способов фильтрования сигнала с помощью структурной индексации. В результате построения подсистемы вейвлет-анализа система многомасштабного анализа дискретных сигналов (МАДС) дополнит свои функциональные возможности способностью выделения из исходного сигнала наиболее четких его составляющих, что должно быть учтено ...

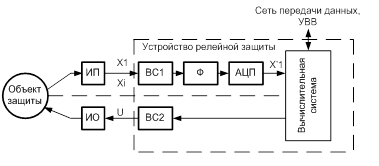

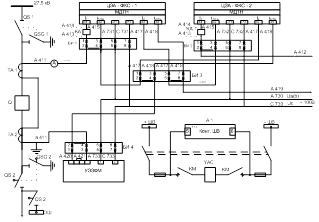

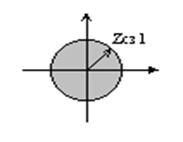

... задаются в поле задания уставок. 6. Безопасность и экологичность проекта В основной части дипломного проекта рассмотрены вопросы, связанные с модернизацией релейной защиты РУ-27,5 кВ тяговой подстанции Заудинск ВСЖД. Наличие на подстанции высоковольтного оборудования и значительных по величине токов определяет выбор темы, и содержание раздела "Безопасность и экологичность проекта", связанных ...

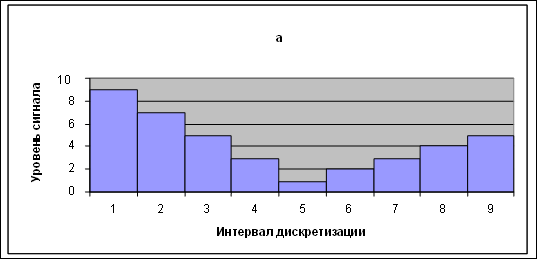

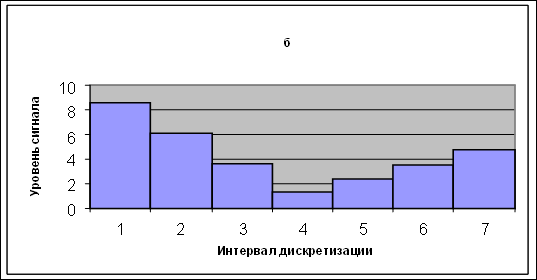

... аналоговых выборок, которые формируются через определенные интервалы времени (используются АИМ, ШИМ, ВИМ). Дискретно-квантованное представление отличается от дискретно-аналогового тем, что выборки формируются в цифровой форме. При обобщенном дискретном представлении координаты сообщения представляют собой коэффициенты некоторого ряда, это позволяет сократить количество координат, т.е. объем выб

... из одного состояния в другое и распределение времени пребывания процесса в каждом состоянии (в виде функции распределения F(t) или в виде плотности распределения f(t)) Классификация систем массового обслуживания В общем случае СМО классифицируется по следующим признакам: · закону распределения входного потока · числу обслуживающих приборов · закону распределения времени обслуживания в ...

0 комментариев