Навигация

Разработка функциональной цифровой ячейки от функциональной логической схемы проектируемого узла до печатной платы узла

1. Задание на курсовую работу

Простановка номеров цепей в соответствие с техническим заданием

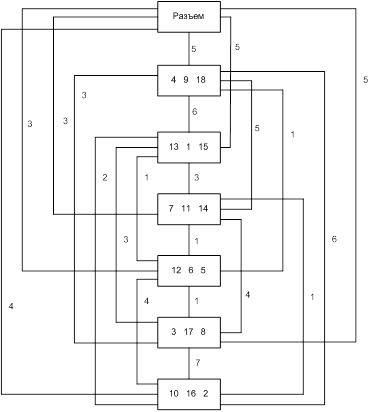

Первым этапом работы является простановка номеров цепей на принципиальной схеме в соответствие с техническим заданием. В нашем случае цепи представляют собой выводы, соединенные с общей шиной, которая, в свою очередь соединена с разъемом. Всего на схеме 18 элементов. В соответствие с техническим заданием они представляют собой 6 отдельных микросхем К155ЛА4 в корпусе DIP 14 по 3 «ЗИ-НЕ» (3 секции) с 4 выводами (3 входа и один инверсный выход). Поэтому был создан элемент: символ элемента в Symbol Editor, посадочное место и тип корпуса элемента (в Pattern Editor), затем символ и посадочное место были объединены в компонент и сохранены в библиотеке с помощью Library Executive [1, 2]. В редакторе Schematic работают с принципиальной схемой. Вместо компонента на шаблоне ставится созданный элемент. Используется Place Port. Стирают цепи и номера цепей, затем элемент соединяется проводом с шиной посредством Place Wire. Затем назначается номер новых цепей (Place Wire+ Port Properties/Net Name). Номера цепей, подходящих к разъему, назначаются произвольно (из списка номеров в техническом задании). Результатом является исходная функционально-логическая схема проектируемого узла (задание на курсовой проект).

2. Компоновки логических элементов в корпуса

Компоновка типовых элементов конструкции

Компоновка – первый этап конструкторского синтеза, при котором определяется однозначное соответствие между функционально-логическим, схемотехническим и конструкторским делением проектируемого устройства. Предполагается, что конструкция разбивается на унифицированные и неунифицированные элементы нескольких уровней конструкторской иерархии.

На этапе компоновки могут решаться задачи типизации, покрытия и разрезания.

Типизация – это процедура выделения в схеме частей, повторяющих друг друга, при этом число типов может быть задано, либо определяться в процессе типизации.

Покрытие – это определение минимального числа корпусов, покрывающих логические элементы принципиальной схемы, то есть задача покрытия решается на этапе перехода от логической схемы к электрической.

Разрезание – это разбиение общей схемы на части, число которых либо задано, либо определяется в процессе разрезания, при этом стремятся обеспечить минимум суммы межблочных связей.

В курсовой работе решается задача разрезания заданной схемы устройства на подсхемы с целью определения принадлежности логических элементов отдельным микросхемам.

Алгоритм разрезания схемы состоит из двух этапов:

– предварительное разрезание (быстрое получение результата)

– окончательная компоновка (улучшение результата итерационным методом).

Последовательный алгоритм предварительной компоновки:

1. Построение матрицы смежности взвешенного графа схемы А.

2. Для каждого элемента рассчитывается его суммарная тяга к остальным элементам.

3. Выбирается элемент, имеющий максимальную локальную степень.

4. Выбранный элемент помечается меткой т. Вначале выполнения алгоритма m=0.

5. Выбираются все элементы, связанные с выбранными ранее, но непомеченные метками.

6. Увеличивается метка m=m+l. Помечаются выбранные в блоке 5 элементы метками т.

7. Выполняются блоки 5, 6, 7 пока не будут помечены все элементы.

8. Выбирается очередной модуль верхнего уровня М j для компоновки.

9. Компонуются в Mj элементы с младшими метками, не вошедшие в компоновку ранее.

10. Компоновка в Mj заканчивается, когда модуль полностью заполнен.

11. Продолжается выполнение блоков 8–11, пока не будут заполнены все модули или пока не будет исчерпан список элементов.

12. Выход из алгоритма.

Итерационный алгоритм улучшения компоновки:

Процесс оптимизации выполняется путем последовательной перестановки элементов из разных модулей.

Пусть элемент Ej установлен в модуль Ms, а элемент Ej установлен в модуль Mt.

Рассчитываем показатель качества перестановки:

Rij = R внш it + R внш jt – R внт i – R внт j – 2 Rij, где

Rвнш it – количество связей Ei с элементами в Mt, Rbhui jt количество связей Ej с элементами в Ms, R внт i – количество связей Ei внутри модуля, R внт j – количество связей Ej внутри модуля. Выбираем ту пару, для которой показатель качества перестановки максимален.

Алгоритм:

1. Ввод начальной компоновки.

2. Расчет матриц связности Cs и Cst и заполнение их.

3. Расчет матрицы эффективности перестановок Rij для всех пар модулей.

4. Выбирается из этих матриц максимальный элемент.

5. Проверка: если показатель качества перестановок отрицательный, переход к блоку 7, иначе к блоку 6.

6. Перестановка элементов Ei и Ej и возврат к блоку 2.

7. Выход из алгоритма. Дальнейшее улучшение с помощью данного

алгоритма невозможно [3].

Таким образом, 18 логических элементов размещаются в 6 микросхемах (по 3 элемента в каждой) оптимальным образом. Для этого используем программу PROG (18 элементов, 6 блоков максимальные значения входных данных для компоновки). Алгоритм работы в этой программе:

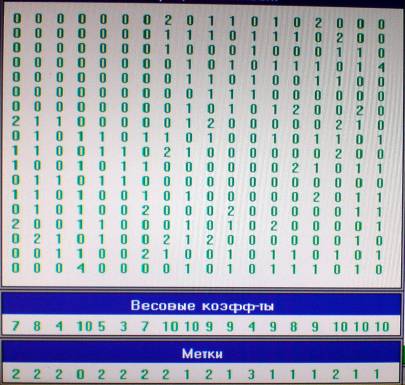

1) В соответствии со своей принципиальной электрической схемой заполняют симметричную матрицу смежности. В этой матрице у нас будет 18 строк и 18 столбцов, что соответствует количеству логических элементов. Последовательно перебирая все элементы, ищут номера повторяющихся цепей. На пересечении i-той строки и j-ro столбца ставят цифру (от 1 до 4), которая и означает количество связей, одинаковых цепей i-ro элемента с j-тым. Главная диагональ такой матрицы – нули. Заполнив матрицу, смотрят предварительную схему соединений (F2). В ней 64 внешних связей и 7 внутренних. Таким образом, на данном этапе используют последовательный алгоритм предварительной компоновки, предварительное разрезание (быстрое получение результата) в автоматическом режиме. Полученная матрица представлена ниже:

Таблица 1

Где весовой коэффициент – числовой коэффициент, параметр, отражающий значимость, относительную важность, «вес» данного фактора, показателя в сравнении с другими факторами, оказывающими влияние на изучаемый процесс.

Весовые коэффициенты равны количеству связей конкретного элемента с остальными элементами схемы.

Обозначение элементов метками:

1. Выбирается элемент с имеющий максимальную локальную степень (чей весовой коэффициент максимален) – элемент №4. Для данного элемента устанавливается метка М = 0.

2. Выбираются элементы, связанные с элементом с М = 0. Данные элементы помечаются меткой М = 1. Элементы №9, 11, 13, 14, 15, 17, 18

3. Выбираются элементы, связанные с элементами с М = 1 и не имеющими меток. Данные элементы помечаются меткой М = 2. Элементы 1, 2, 3, 5, 6, 7, 8, 10, 16.

4. Выбираются элементы, связанные с элементами с М = 2 и не имеющими меток. Данные элементы помечаются меткой М = 3. Элемент 12.

На этом этап обозначение элементов метками закончен. Далее идет первоначальная компоновка элементов.

|

|

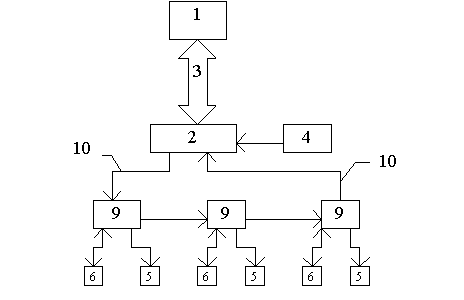

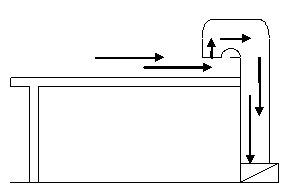

| Рис. 2. Предварительная схема соединений |

Применение этого алгоритма приводит к постепенному ослаблению внутриблочных связей от первого блока до последнего.

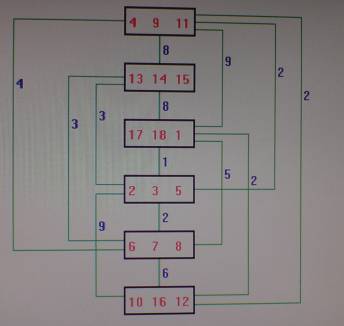

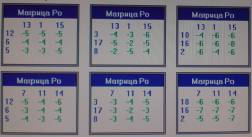

2) Работают с матрицами Ро. Их 15 штук (фактически, это схема соединений в матричном виде). Выбираем из матриц ту, у которой максимальное значение элемента матрицы (4,3 и т.д.). В ней меняют местами компоненты, пересечение которых и дает этот элемент матрицы. Смотрят промежуточный результат компоновки: видно, что количество внутренних связей увеличивается по сравнению с первоначальным числом (клавиша F2 для просмотра схемы соединений), а количество внешних связей уменьшается. Затем снова выбирают матрицу с максимальным значением элемента. Продолжать до тех пор, пока все элементы всех матриц не станут отрицательными, либо равными нулю. На данном этапе улучшают начальную компоновку итерационным алгоритмом. То есть основная идея этого алгоритма и этого этапа заключается в межблочных перестановках пар элементов с целью минимизации общего количества межблочных связей. Итоговый вид всех матриц Итоговый вид всех матриц:

|

|

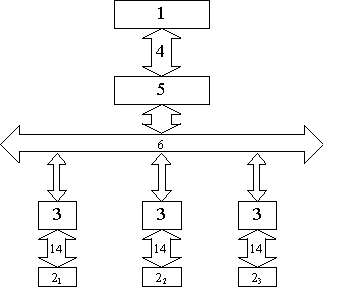

| Рис. 3. Итоговый вид всех матриц |

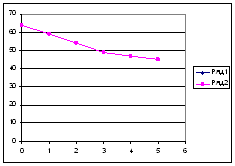

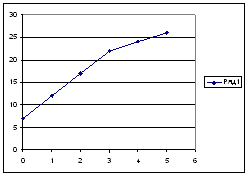

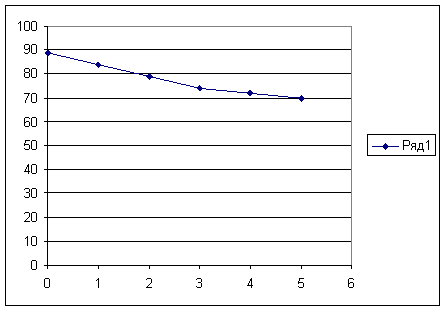

0 итераций (нет перестановок). Внешних связей: 64, внутренних связей: 7.

1 итерация (1-ая перестановка). Внешних связей: 59, внутренних связей: 12.

2 итерация (2-ая перестановка). Внешних связей: 54, внутренних связей: 17.

3 итерация (3-я перестановка). Внешних связей: 49, внутренних связей: 22.

4 итерация (4-ая перестановка). Внешних связей: 47, внутренних связей: 24.

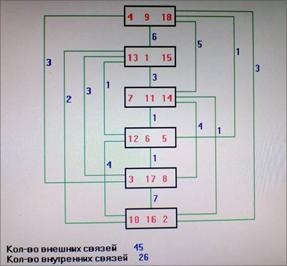

5 итерация (5-ая перестановка). Внешних связей: 45, внутренних связей: 26.

Рис. 4. График зависимости числа внешних связей от числа итераций

Рис. 5. График зависимости числа внутренних связей от числа итераций

3) После работы с матрицами на экран выводится схема соединений. Это и есть оптимальное расположение (компоновка) элементов в конструкции (элементов в микросхемах и микросхем между собой).

Рис. 6. Схема соединений

Видно, что процесс оптимизации связан с увеличением внутренних связей и уменьшением внешних. После каждой перестановки число внутренних связей увеличивается, а число внешних – уменьшается. Это связано с тем, что меняются местами элементы из разных микросхем, которые являются компонентами матриц Ро. В результате задача оптимизация будет выполнена: в заданное количество блоков (микросхем) расположили с минимальным количеством внешних связей между ними по 3 элемента. Это облегчит дальнейшие этапы моделирования.

4) Осталось скомпоновать разъем с микросхемами, так как у него тоже есть электрические связи с элементами и он является частью конструкции. Фактически, повторяется п. 1 нашего алгоритма, но без заполнения матрицы смежности, так как программа не предусматривает компоновку с количеством блоков, равным 7. Для каждой микросхемы, начиная с первой, смотрят номера цепей элементов в ней, которые повторяются с номерами цепей этого разъема. На схеме соединений ставится связь от разъема к микросхеме с цифрой, которая говорит о числе совпадений цепей разъема и микросхемы. Повторять то же самое для оставшихся 5 микросхем. Соответственно, получаем схему соединений, которая будет представлять взвешенный граф с 7-ю элементами: 6 микросхем и 1 разъем. Изменяются и графики зависимостей, так как разъем увеличивает число внешних связей (в данном случае на 46).

Рис. 7. Схема соединений с учетом разъема

|

|

| Рис. 8. График зависимости числа внешних связей от числа итераций внешних связей от числа итераций с учетом разъема. |

Похожие работы

... (ШД), адресов (ША) и управления (ШУ). Однокристальные микропроцессоры получаются при реализации всех аппаратных средств процессора в виде одной БИС или СБИС (сверхбольшой интегральной схемы). По мере увеличения степени интеграции элементов в кристалле и числа выводов корпуса параметры однокристальных микропроцессоров улучшаются. Однако возможности однокристальных микропроцессоров ограничены ...

... : ¾ температура, °С +25±10; ¾ относительная влажность воздуха, % 45...80; ¾ атмосферное давление, мм рт. ст. 630...800. Так как блок интерфейсных адаптеров предназначен для работы в нормальных условиях, в качестве номинальных значений климатических факторов указанные выше принимают нормальные значения ...

... мероприятия по обеспечению однородности выпускаемой продукции. Все эти мероприятия можно объединить в четыре группы: 1. совершенствование технологии производства; 2. автоматизация производства; 3. технологические (тренировочные) прогоны; 4. статистическое регулирование качества продукции. 2.10. Проектирование технологических процессов с использованием средств ...

... . Целью дипломного проекта является разработка и исследование автоматической системы регулирования (АСР) асинхронного высоковольтного электропривода на базе автономного инвертора тока с трехфазным однообмоточным двигателем с детальной разработкой программы высокого уровня при различных законах управления. В ходе конкретизации из поставленной цели выделены следующие задачи. Провести анализ ...

0 комментариев