БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИНФОРМАТИКИ И РАДИОЭЛЕКТРОНИКИ

КАФЕДРА РЭС

РЕФЕРАТ

НА ТЕМУ:

Проектирование сложных логических структур на МДП-транзисторах

МИНСК, 2009

По схемотехнической реализации ЛЭ двухступенчатой логики, выполняемые на биполярных транзисторах подразделяется на:

· Диодно-транзисторные (DTL-2);

· Транзисторно-транзисторные (TTL);

· Транзисторно-транзисторные с диодами Шотки (TTL-S);

· Транзистор-транзисторно-транзисторные (T-TTL).

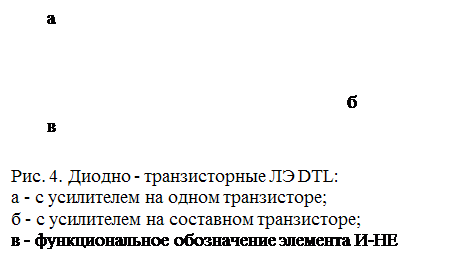

Диодно-транзисторные ИМС (DТЛ-2)

На рис. 1 приведена схема функционального элемента диодно-транзисторной логики, реализующая двухступенчатую функцию И-ИЛИ-НЕ. Реализация логической операции И и ИЛИ в микросхемах DТЛ-2 осуществляется на диодах, а операция НЕ выполняется на транзисторном усилителе-инверторе. Для увеличения логических возможностей по входам И и ИЛИ применяются специальные расширители функций И и ИЛИ.

На смену диодно-транзисторным пришли более совершенные ИМС транзисторно-транзисторной логики.

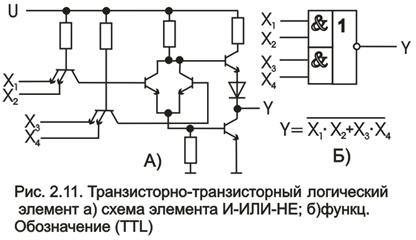

Транзисторно-транзисторные ИМС (TTL)

В базовом TTL-элементе логические операции осуществляются транзисторами, чем определяется название типа логики: транзисторно-транзисторная.

Разработка технологии изготовления многоэмиттерного транзистора (МЭТ), который легко реализуется методами интегральной технологии, послужила определяющим фактором в создании ряда серий ИМС транзисторно-транзисторной логики. Многоэмиттерный транзистор представляет собой интегральный элемент, объединяющий преимущества диодных логических схем и транзисторного усилителя. Его база через резистор соединена с положительным зажимом источника питания, эмиттеры являются входами элемента, а в цепь коллектора включен эмиттерно-базовый переход следующего транзистора. Потенциал базы МЭТ выше потенциала коллектора, поэтому коллекторный переход МЭТ открыт. Режим эмиттерного перехода зависит от ситуации на входах элемента. Если хотя бы на одном входе присутствует низкий потенциал лог. 0 (например X1=0), то потенциал эмиттера ![]() меньше потенциала базы Uб — эмиттерный переход открыт. Таким образом, оба перехода открыты, и он насыщен. При этом практически весь ток базы проходит в цепь эмиттера, а напряжение Uк (МЭТ) на коллекторе составляет доли вольта.

меньше потенциала базы Uб — эмиттерный переход открыт. Таким образом, оба перехода открыты, и он насыщен. При этом практически весь ток базы проходит в цепь эмиттера, а напряжение Uк (МЭТ) на коллекторе составляет доли вольта.

Если же на всех входах элемента высокий потенциал (X1=X2=1), то Uэ>Uб; эмиттерный переход закрыт и ток базы (МЭТ) переключается в цепь коллектора (напряжение на котором составляет около 2 В).

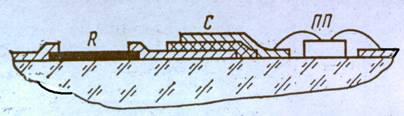

Повторяя структуру диодно-транзисторных ИМС, транзисторно-транзисторные ИМС (рис. 2) позволили значительно увеличить быстродействие (до 20 МГц), повысить уровень помехоустойчивости (Uп=0,7 В), снизить потребляемую мощность.

Выходные усилители TTL-микросхем с симметричным транзисторным выходом обеспечивают высокую нагрузочную способность базовой схемы (n=10) при значительных емкостях нагрузки (Сн=100 пФ). При проектировании аппаратуры на TTL-микросхемах необходимо учитывать, что их выходные каскады в динамическом режиме потребляют мощность в 2…3 раза больше, чем в статическом режиме. Это объясняется появлением значительных импульсных токов на фронтах сигналов.

Одним из наиболее важных достижений в технологии изготовления TTL-ИМС явилось применение диодов Шотки, включение которых между базой и коллектором транзисторов позволило резко повысить быстродействие за счет устранения режима насыщения транзисторов. Обычно структуру диода Шотки со связанными с ним коллектором и базой транзистора называют транзистором Шотки. Она практически полностью повторяет конфигурацию TTL-вентиля, но имеет в 2…3 раза большее быстродействие.

Дальнейшее совершенствование схемотехники TTL с диодами Шотки привело к созданию модификации диодно-транзисторных маломощных ИМС с транзисторами Шотки и логическими диодами Шотки на входе. Схема такого элемента И-НЕ, получила название маломощного TTL-элемента с транзисторами Шотки. Ее особенность состоит в том, что за счет применения быстродействующих диодов Шотки с малым падением напряжения на переходе в открытом состоянии входные многоэмиттерные транзисторы традиционных TTL-ИМС заменены диодными вентильными сборками, что позволило уменьшить площадь вентиля на кристалле при сохранении высокого быстродействия. Потребляемая мощность таких вентилей в 5…10 раз меньше. Этот фактор обеспечил широкое применение маломощных TTL-элементов с диодами Шотки.

Совершенствование технологических приемов, размеров транзисторов и методов проектирования позволили достигнуть для TTLШ-ИМС задержку 1-2 нс на вентиль, что соответствует уровню ECL-ИМС при меньшей в 2…3 раза потребляемой мощности на вентиль.

|

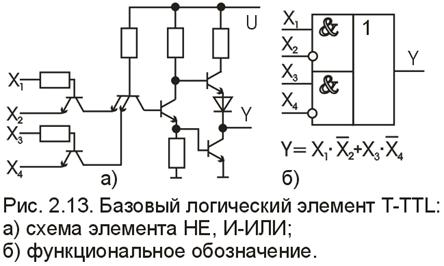

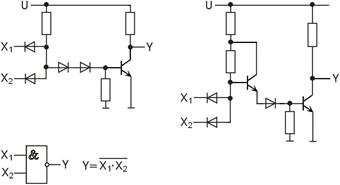

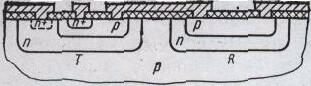

Транзистор-транзисторно-транзисторные ИМС (T-TTL)

Микросхемы транзистор-транзисторно-транзисторной логики относятся к разряду логических микросхем, выполненных на основе модернизации типовых TTL-ИМС. На рис. 4 приведена базовая схема элемента T-TTL, реализующая двухступенчатую логическую функцию с запретом НЕ, И-ИЛИ. Логическая операция И с запретом выполняется на транзисторах, управляемых по базе и эмиттеру, а функция ИЛИ реализуется на МЭТ. В схемах с большим числом входов ИЛИ увеличивается число эмиттеров у МЭТ, но число МЭТ не изменяется. Это создает определенные технологические преимущества T-TTL-элементов перед сложными TTL-элементами, у которых число МЭТ всегда равно числу входов ИЛИ. Наличие запрещающего входа по эмиттеру в схеме И открывает широкие возможности при построении цифровых устройств на основе совместного использования T-TTL и TTL-элементов, которые имеют электрическое согласование.

В ряде случаев T-TTL-элементы полностью заменяют TTL, позволяя более экономично реализовать сложные функциональные узлы. Существование прямых и инверсных входов в T-TTL-элементах позволяет увеличить их нагрузочную способность за счет одновременной работы на группы входов разного вида. Действительно, прямые входы (базы транзисторов) являются потребителями тока, а инверсные входы — источниками тока для выходного усилителя T-TTL-элемента. Поэтому в состоянии логической 1 (высокий уровень на выходе) схема будет отдавать ток, а в состоянии логического 0 потреблять ток от нагрузки. Поскольку ток одного прямого входа меньше тока, потребляемого от инверсного входа, то суммарный ток нагрузки выхода в состоянии логической 1 мал и не снижает высокого уровня на выходе T-TTL-элемента.

Недостатками T-TTL-элементов считают низкий уровень статической помехоустойчивости и увеличенное время задержки переключения при управлении по прямому (базовому) входу элемента НЕ, И.

Существует другая модификация T-TTL-элементов без использования базовых входов. В качестве примера на рис. 5 приведена схема элемента, выполняющего функцию И-ИЛИ. Особенностью схемы является выполнение функций как ИЛИ так и И на многоэмиттерных транзисторах. Поступление логической 1 на все входы МЭТ схемы И (например, на входы X1,X2) приведет к отпиранию коммутирующего транзистора VT2. Транзистор VT5 будет открыт, а выходной усилитель заперт, и на выходе Y сформирован уровень логической 1. При поступлении логической 1 на VT4 отпирается коммутирующий транзистор VT3 и вновь на выходе Y будет уровень логической 1. Управление элементами по входу ИЛИ осуществляется сигналом с уровнем логического 0. Диод в эмиттерных цепях коммутирующих транзисторов обеспечивает необходимый уровень помехоустойчивости по входам И.

Выполнение схемы И на основе МЭТ позволяет увеличить число логических входов путем увеличения числа эмиттеров.

Элементы T-TTL совместно с элементами TTL обеспечивают высокую гибкость проектирования и построения экономичных схем цифровых узлов.

В заключение отметим основные положительные качества элементов T-TTL:

1. наличие прямых и инверсных входов позволяет исключить ряд промежуточных инверторов при реализации сложных функций;

2. простота реализации триггеров однофазного типа, которые обеспечивают уменьшение числа входов, выходов и коммутационных связей при создании БИС;

3. обеспечивается двойная нагрузочная способность при работе на прямые и инверсные входы схем НЕ, И-ИЛИ одновременно;

4. существенно снижается потребляемая мощность в схемах НЕ, И-ИЛИ с большим числом входов по ИЛИ;

5. обеспечивается электрическое согласование с элементами TTL-ИМС и создание экономичных цифровых узлов при совместном использовании TTL и T-TTL-ИМС;

6. значительно снижается потребляемая мощность T-TTL-элементов и повышается быстродействие при использовании диодов Шотки.

Логические элементы на полевых транзисторах

Широкое практическое применение при разработке логических схем получили полевые транзисторы с МДП-структурой.

В отличие от биполярных транзисторов, управляемых током, полевые транзисторы по принципу действия являются аналогами электронных ламп, так как управляются напряжением. Условное Графическое обозначение МДП-транзистора приведено на рис. 6.

Подавая на затвор МДП-транзистора напряжение различного уровня, можно модулировать сопротивление канала сток-исток, то есть изменять значение тока в канале при постоянном напряжении на стоке.

Различают МДП-транзисторы двух типов проводимости: p- и n- типа.

МДП-транзисторы p-типа отпираются при отрицательном, а n-типа – при положительном смещении напряжения затвора относительно стока.

Логические схемы на МДП-транзисторах p-типа с заземленным истоком требуют отрицательного напряжения питания (схемы отрицательной логики). Логические схемы на МДП-транзисторах n-типа с заземлением требуют положительного питающего напряжения (схемы положительной логики). При построении логических элементов на основе дополняющих МДП-транзисторов с каналами р- и n-типов (КМДП-ИМС) возможно создание схем как положительной, так и отрицательной логики.

Комплементарной (то есть взаимодополняющей) считают пару полевых транзисторов, имеющих одинаковые характеристики, но противоположную полярность питающих напряжений, сигналов управления и токов исток-сток.

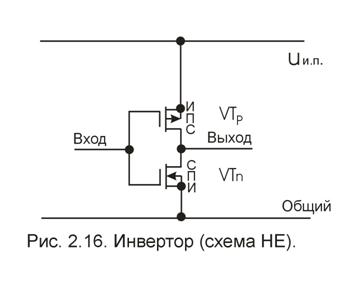

Если такую пару соединить следующим образом (рис 7):

(обратите внимание, верхний транзистор «перевернут») то: при напряжении на объединенном затворе (входе), равном 0 В, верхний транзистор будет открыт, а нижний закрыт и на выходе схемы будет ![]() , так как у открытого транзистора сопротивление исток-сток мало, а у закрытого велико (разрыв цепи исток-сток). При UBX= 1 наоборот.

, так как у открытого транзистора сопротивление исток-сток мало, а у закрытого велико (разрыв цепи исток-сток). При UBX= 1 наоборот.

На рис. 8 приведены четыре варианта выполнения простейших элементов-инверторов на МДП-транзисторах: n-типа (рис. 8,а), р-типа (рис.,б) и на дополняющих транзисторах (рис., в, г). Для схем на дополняющих транзисторах полярность логики зависит от последовательности включения транзисторов р- и n-типов. Если транзистор n-типа непосредственно подключен к общей шине, а транзистор р-типа к источнику питания (рис. 8, г), то элемент работает в режиме положительной логики (уровню логической 1 соответствует U, а уровню логического О соответствует 0 источника питания).

Если транзистор р-типа непосредственно подключен к общей шине, а транзистор n-типа - к источнику питания, то элемент работает в режиме отрицательной логики (уровню логической 1 соответствует «-U», а уровню логического 0 соответствует 0 источника питания).

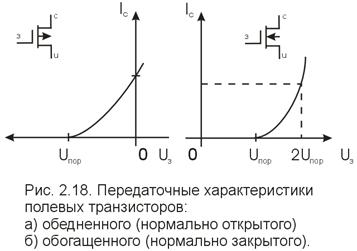

Передаточные характеристики полевых транзисторов имеют следующий вид (рис. 9).

В первом из них зависимость тока стока 1С от напряжения на затворе U3 имеет вид кривой (рис., а). Такой транзистор называют нормально открытым, так как при напряжении затвора, равном нулю, он проводит ток (при U3 = 0, Ic = max). Второй тип полевого транзистора нормально закрытый. При нулевом потенциале на затворе ток стока транзистора равен нулю (при ![]() , Ic = max) (рис., б).

, Ic = max) (рис., б).

Затвор МДП-транзистора называют изолированным, поскольку он отделен от истока и стока изолирующим материалом, имеющим очень большое сопротивление. Тем не менее напряжение на затворе создает электрическое поле, которое увеличивает или уменьшает ток, текущий от истока к стоку. Этот «полевой эффект» дал название транзистору – «полевой транзистор».

По этой причине, независимо от напряжения на затворе, никакой ток практически не течет от затвора к истоку или от затвора к стоку. Сопротивления между затвором и другими выводами очень велики, намного больше мегаома. Ток, протекающий по этим сопротивлениям очень мал, обычно меньше одного микроампера (мкА, ![]() А), и называется током утечки.

А), и называется током утечки.

Само условное обозначение МДП-транзистора напоминает нам, что между затвором и двумя другими выводами нет никакого соединения. Однако изображение МДП-транзистора наводит на мысль, что затвор имеет емкостную связь с истоком и стоком. В быстродействующих схемах мощность, расходуемая при заряде и разряде этих емкостей при каждом изменении входного сигнала, составляет заметную долю потребляемой схемой мощности.

В цифровых электронных устройствах используют преимущественно нормально закрытые полевые транзисторы.

Имеется определенная аналогия между биполярным n-р-n транзистором и полевым нормально закрытым транзистором с каналом n-типа: оба они не проводят ток при нулевом (и отрицательном) смещении на управляющем электроде, оба открываются при положительном смещении на этом электроде, оба достигают тока насыщения.

В логических схемах на МДП-транзисторах одного типа проводимости нагрузкой является нормально открытый МД11-транзистор. В этом случае затвор транзистора-нагрузки подключается к источнику напряжения смещения UCM, который, как правило, имеет более высокий (по абсолютной величине) уровень напряжения, чем коммутируемое напряжение логической схемы.

В дальнейшем для простоты описания логических схем на МДП-транзисторах будем рассматривать схемы с одним источником питания.

Известны три разновидности схем на МДП-транзисторах: статического, квазистатического и динамического действия.

Специфические свойства МДП-транзисторов сверхвысокое входное сопротивление (Rвх >1012Ом) и способность паразитной емкости затвора длительное время сохранять заряд и уровень напряжения на затворе, наиболее широко используются при построении триггерных схем для регистровых и счетных устройств.

Схемы логических элементов статического и динамического действия на МДП-транзисторах n-типа и на дополняющих транзисторах будут рассмотрены ниже.

ЛЭ на одноканальных МДП-структурах

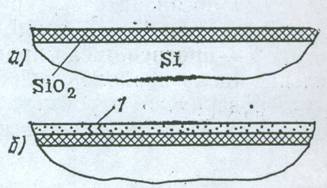

В настоящее время практически полностью осуществлен переход на применение n-канальных МДП-структур для проектирования БИС и СБИС при использовании транзисторов одной структуры. Однако первые достижения при создании МДП-ИМС и БИС связаны с развитием р-канальной технологии, где удалось достигнуть уровня интеграции до 10 транзисторов в кристалле. Однако с распространением р-МДП-ИМС и БИС стали проявляться недостатки р-канальных схем: высокие (по модулю) напряжения питания (-12...-27 В), невысокое быстродействие (менее 1 МГц), значительная потребляемая мощность в статическом режиме (5... 10мВт/вентиль) и сложность согласования с биполярными ИМС, где типовые напряжения питания +3...+5В. По этой причине интенсивное совершенствование МДП-технологии шло в направлении создания n-канальных и КМДП-элементов.

ЛЭ-ты на полевых МДП-транзисторах n-типа, обладая более высоким быстродействием и крутизной передаточной характеристики, позволяют обеспечить единый номинал питающего напряжения +5 В как у биполярных TTL и TTLIII-элементов. По этой причине все основные разновидности логических МДП-элементов статического, квазистатического и динамического действия строятся на одноканальных МДП-транзисторах n-типа.

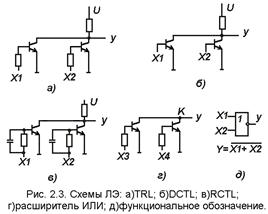

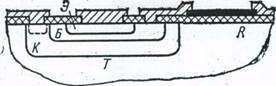

Основные принципы построения логических схем статического действия на МДП-транзисторах одной структуры во много соответствуют принципам построения транзисторных логических схем с непосредственными связями (DCTL). Так, для построения многовходового вентиля ИЛИ-НЕ к одному нагрузочному МДП-транзистору подключаются стоки m-логических транзисторов, а их истоки – к общей шине (рис. 10). На рис. 10,а приведена схема вентильного элемента ИЛИ-НЕ на два входа, содержащая один нагрузочный транзистор и два логических. Ограничение параметра mили (коэффициент объединения но входу) такой схемы определяется снижением уровня логической 1 на входе за счет падения напряжения на нагрузке от суммарного тока утечки I0 цепи сток-исток всех m входных МДП-транзисторов. Поскольку ток I0 МДП-транзисторов достаточно мал, то параметр m логической схемы может достигать 10 и выше.

Обладая сверхвысоким входным сопротивлением по затвору, МДП-транзистор обеспечивает построение ЛЭ с очень высокой нагрузочной способностью (п > 20). Нагрузочная способность МДП-ИМС n-типа ограничивается лишь снижением быстродействия с ростом числа нагрузок, так как увеличивается постоянная времени заряда паразитной емкости нагрузки Сн током, протекающим через нагрузочный МДП-транзистор.

Интегральная технология МДП-структур позволяет использовать последовательное (ярусное) включение МДП-транзисторов, когда в цепь между нагрузкой и общей шиной включен не один, а два, три или четыре МДП-транзистора по схеме И. В этом случае исток нижнего логического МДП-транзистора подключается к общей шине, а его сток к истоку вышестоящего и т. д. Путь току через нагрузку к общей шине открывается лишь в том случае, если будут открыты МДП-транзисторы всех ярусов.

|

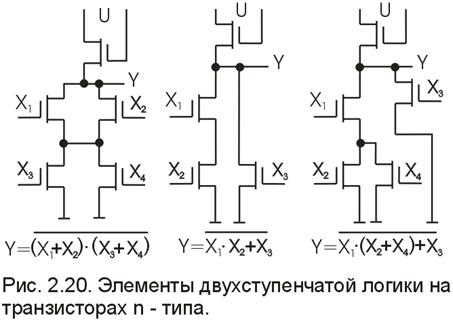

На рис. а, б двухвходовые схемы И-НЕ и ИЛИ-НЕ имеют высокую нагрузочную способность n, но параметр mи значительно уступает параметру

На рис. приводятся варианты n-канальных МДП-ИМС, выполняющих двухступенчатые логические функции типа И-ИЛИ-НЕ. Эти ИМС за счет ярусного и параллельного включения транзисторов имеют только одну ступень задержки тср на преобразование информации, что соответствует биполярным элементам одноступенчатой логики.

Таким образом, за счет гибкости проектирования сложных логических структур на МДП-транзисторах обеспечивается более высокое функциональное быстродействие по сравнению с ЛЭ на биполярных транзисторах.

С ростом степени интеграции транзисторов в МДП-ИМС встал вопрос о снижении потребляемой мощности на вентиль, которая у МДП-ИМС на транзисторах n-типа довольно значительная (1... 10 мВт/вентиль). Снижение мощности за счет увеличения сопротивлений МДП-транзисторов в цепях нагрузки приводит к снижению быстродействия (до 50... 100 кГц) и сужает область применения МДП-БИС. Значительное уменьшение потребляемой мощности при высоком быстродействии достигается в ИМС на дополняющих (комплементарных) МДП-транзисторах.

Литература

1. Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. М.: Мир, 2001. - 379 с.

2. Новиков Ю.В., Скоробогатов П.К. Основы микропроцессорной техники. Курс лекций. М.: ИНТУИТ.РУ, 2003. - 440 с.

3. Пухальский Г.И., Новосельцева Т.Я. Цифровые устройства: Учеб. пособие для ВТУЗов. СПб.: Политехника, 2006. - 885 с.

4. Преснухин Л.Н., Воробьев Н.В., Шишкевич А.А. Расчет элементов цифровых устройств. М.: Высш. шк., 2001. - 526 с.

5. Букреев И.Н., Горячев В.И., Мансуров Б.М. Микроэлектронные схемы цифровых устройств. М.: Радио и связь, 2000. - 416 с.

6. Соломатин Н.М. Логические элементы ЭВМ. М.: Высш. шк., 2000. – 160 с.

Похожие работы

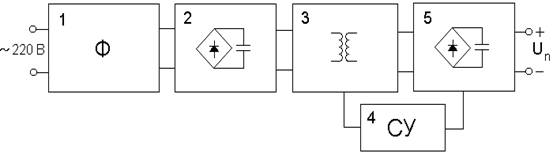

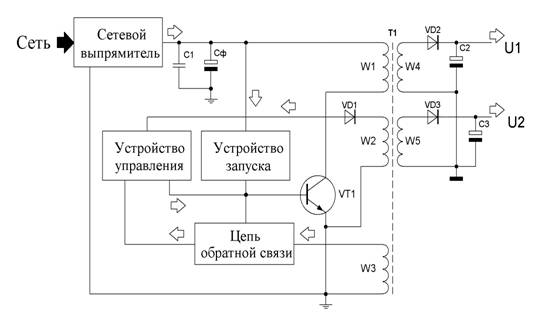

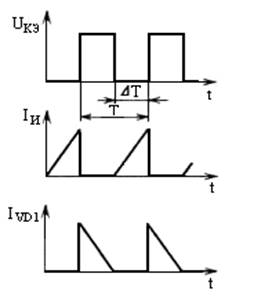

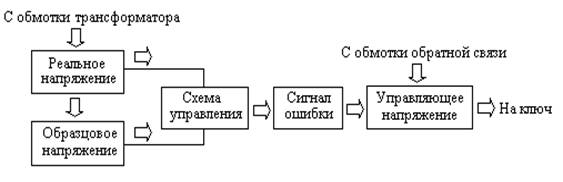

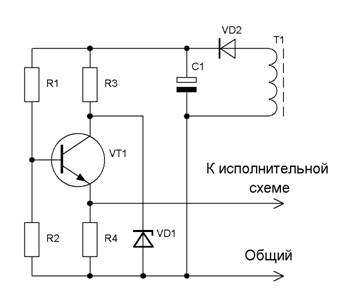

... 2 – управляющее напряжение 2; 3 – выходной сигнал. Рисунок 3.12 – Диаграммы работы буфера управляющего напряжения. Промоделируем динамику работы всей схемы электрической принципиальной (приложение В). Реальный анализ схемы в составе импульсного источника питания в программе проектирования электронных схем не возможен ввиду использования с схеме импульсного трансформатора, модель которого в ...

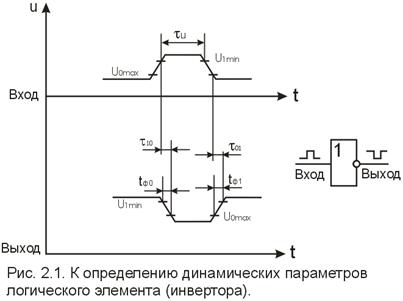

... первой логической ступени выполняется на транзисторах, увеличение параметра m требует значительного увеличения числа компонентов ЛЭ и роста площади кристалла ИМС. В существующих сериях интегральных микросхем основные логические элементы выполняются, как правило, с небольшим числом входов . Увеличение числа входов m обеспечивается за счет введения в серию ЛЭ специального расширителя, подключение ...

... связью (ПЗС), на которых могут быть построены сдвиговые регистры, запоминающие устройства и некоторые логические элементы. 3. Причины ограничивающие минимальные размеры интегральных микросхем Для выбранной структуры ИМС минимальные размеры элементов ИМС в целом зависят от возможностей фотолитографического процесса, которые характеризуются тремя основными параметрами: 1) минимальным размером ...

... легко отображения и использования ключевых слов. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ПРОЕКТИРУЕМОЙ ЗАКАЗНОЙ БИС 5. РАЗРАБОТКА ПРИНЦИПИАЛЬНЫХ ЭЛЕКТРИЧЕСКИХ СХЕМ БАЗОВЫХ ЯЧЕЕК ГРУППОВОГО КАНАЛЬНОГО ИНТЕРФЕЙСА ЦИФРОВОЙ СИСТЕМЫ ПЕРЕДАЧИ .Любое цифровое устройство предназначено для выполнения той или иной логической функции, следовательно, такое устройство можно представить в ...

0 комментариев