Навигация

Управляющие устройства и их виды

Управляющие устройства (УУ): их виды

Операционные устройства позволяют выполнить преобразование некоторых кодов в соответствии с логикой выполняемой операции.

При этом операционное устройство может быть представлено множеством микроопераций, которые могут быть выполнены последовательно или параллельно при инициировании определённых составляющих узлов с помощью выделенных сигналов управления.

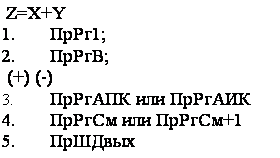

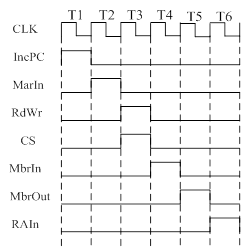

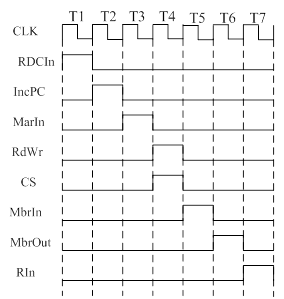

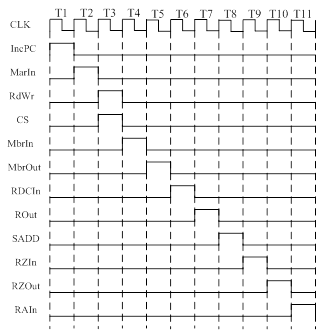

Например, сложение/вычитание двоичных кодов выполняется следующей последовательностью сигналов:

Т.о. возникает необходимость в использовании спец. устройства (устройство управления), которое предназначено для формирования распределённой во времени последовательности управляющих сигналов, подаваемых на компоненты операционного блока вместе с сигналом синхронизации и обеспечивающие выполнение заданной операции.

Существуют 2 принципиально разных подхода к УУ:

1)УУ с жесткой логикой;

2) УУ с микропрограммной логикой или МПУУ

УУ с жесткой логикой строятся на основе жестко заданных связей между его компонентами, реализующих формирование и передачу сигналов управления в требуемой последовательности, учитывая состояние УУ, выполняемую операцию и значения т.н. «осведомительных сигналов», характеризующих результаты выполнения предыдущей операции, а также состояния требуемых компонент операционного устройства.

УУ с жесткой логикой не поддаются модификации и при необходимости изменений должны быть полностью заменены.

Основное их достоинство – высокая производительность, связанная с формированием управляющих сигналов с помощью комбинационных схем.

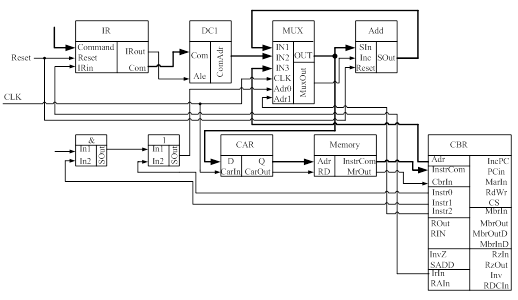

Управляющие устройства с жесткой логикой представлены координационными схемами, который обеспечивают построение распределения во времени последовательности сигналов управления, в зависимости от кода операции и № такта сигнала синхронизации.

При этом учитывается значение осведомительного сигнала от операционного устройства.

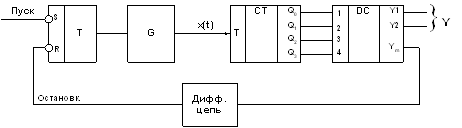

ПоПо ходу операции из Рг команд, дешифратор кода активирует 1 выходную линию, соотв. выполняемой команде. Счетчик тактов запускается с мом. выполнения тек. команды. Дешифратор нового такта активизирует 1 вых. линию, соотв. № такта.

В результате устр. обр. упр. сигналов, в зависимости от № такта и вып. команды, с помощью логических схем «и/или», формирует требуемую последовательность управляющих сигналов, инициализирующих выполняемые последовательности МО в операционных устройствах.

Недостаток данного устройства – ориентация на выполнение команд, требующих одинакового количества тактов, поэтому для ее исп. необх. «выровнять» все команды по команде, треб. max числа тактов.

Команды, треб. min количества тактов – однобайтные команды, или команды с min количеством бит (команды обр. регистров, изм. режимов, команды установки и т.д.).

В отличие от них, длинные команды исп. смешанную адрессацию (регистровую и непосредственную, косвенную).

Поэтому выравнивание команд приводит к неэф-му исп. памяти.

Для повышения эф-ти устр. упр. с ж. л. исп. счетчики тактов, обеспечивающие выполнение требуемого типа команд.

В качестве примера рассмотрим управляемое устройство, обеспечивающее выполнение, или поддержку коротких и длинных команд.

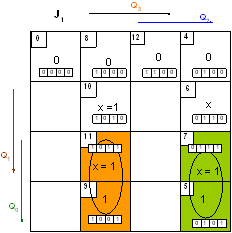

В зависимости от типа команды по длине, схема управления предоставляет возможность активизировать или только счетчик тактов 1, или на определенном такте запускать счетчик тактов 2, реализуя выполнение команд, требующих большего количества тактов.

Рассмотрим, каким образом можно обеспечить образование сигналов управления.

Для этих целей используется комбинации логических элементов «и/или», которые в зависимости от типа команды (код команды), № такта и знач. осведомительных сигналов, формируют необходимые сигналы упр.

На примере форм-я сигнала упр. ВР можно говорить, что этот сигнал генерируется при вып. j-й команды во всех тактах, кроме к-го при наличии освидомит. сигнала L.

Для построения устр. упр. с ж. л. используется объединение микропрограмм, включая все выполняемые микропрограммы, кажд. из кот. соотв. некоторому коду команды.

Микропр-ма предст. собой последовательность, а также разветвление выполнения отдельных микропрограмм, в зависимости от кода вып. команды и знач. осведомит. сигналов.

Объедененная микропрограмма м.б. построена по след. схеме:

Для искл. микроопер., вход. во все микропр-ы, их общие части, связ. с начальной инициализацией, а также корректным завершением выполнения, выделяются в общие части микрокоманды. Исключенные части каждой микропер., инициализируются в зав. от кода выполняемой микропрограммы.

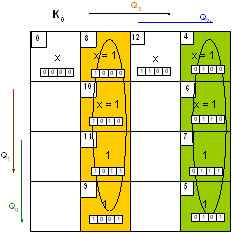

Для исп. понятий автоматов при постр. устр. упр. необходимо выделить состояния устр. упр., а также усл. перехода из 1 сост. в др. Для автомата Мура, в кач. состояний исп. события генерации (возникновение соотв. сигналов упр.).

Некоторые сост. могут порождать в т. сл. формирование нескольких сигналов упр. После этого усл. перехода из сост. в сост. будут иметь значения соотв. осведомит. сигналов.

В т. сл. для хранения инф. о тек. сост. автомата упр. можно исп. набор триггеров, кол-во кот. k=ln r, r – кол-во состояний.

Иными словами мыпронумеруем все сост. и сопоставим всем сост. некоторый 2-й код, соотв. данному сост. Зная порождаемые сигналы упр. каждым сост., можно, исп. логическую схему «или» и дешифратор состояния, обеспечить формир-е требуемых сигналов упр.

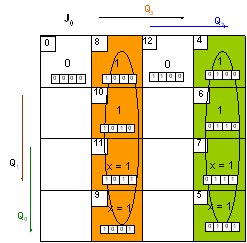

Автомат Мили требует меньшего кол-ва триггеров для отобр. состояний, т.к. описывается меньшим кол-ом состояний, но его недостаток – изменение состояния происходит при изм. освед. сигн., что может повлеч изм. упр. сигн., кот. будут преждевременными для текущей выполняемой команды.

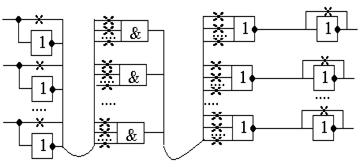

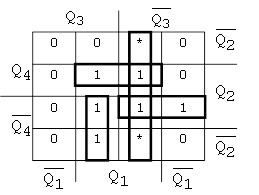

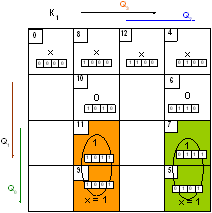

Поэтому аппарат Мили применяют со схемами задержки, либо в комбинации: Мура – Мили. Для построения устр. упр. с ж. л. исп. программируемые логические матрицы, которые содержат слой входных инверторов, слой эл-ов «и», слой эл-ов «или» и слой вых. инверторов. Крестики – возможность разорвать соотв. цепь в процессе программирования матрицы.

Матрица образована т.о., что на любой эл-т «и» м.б. поданы все знач. прямых и инвертных входных сигн. На вход любого эл-та «или» м.б. поданы выходы любого эл-та «и».

МПУУ – требуемый набор управляющих сигналов сохраняется в т.н. «микропрограммной памяти» с доступом только для чтения (read-only).

Каждый набор таких сигналов соответствует некоторой микрооперации и представлен в виде микрокоманд.

В соответствии с логикой выполнения операции каждая микрокоманда в микропрограмме определяет (содержит) адрес следующей микрокоманды, необходимой для выполнения операции.

МПУУ функционируют с использованием доступа к МП-памяти, поэтому их применение стало оправданным лишь с появлением быстрых модулей памяти.

Основное достоинство МПУУ – возможность модернизации процессора или замены множества выполняемых операций путём перехода к новым модулям МП-памяти.

Т.к. МП-память входит в состав процессора в виде компонента УУ, то данное преимущество даёт возможность автоматизированного и автоматического проектирования компонент УУ и микропроцессора в целом.

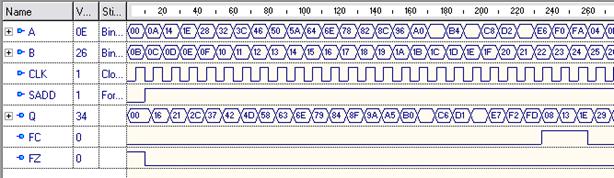

Для выработки управляющих сигналов используются следующие обозначения:

1. каждый управляющий сигнал соответствует некоторой операции, реализуемой операционным блоком. Пусть V1…Vm – совокупность управляющих сигналов, причём Vi инициирует выполнение соответствующей микрооперации.

2. При выработке управляющих сигналов используются U1…Un – значения «осведомительных сигналов» о результатах выполнения предыдущей операции, а также о состоянии компонент операционного устройства.

Похожие работы

... состояний триггеров. Рис.3.5. Карта Карно, описывающая зависимость состояния входа D4 от состояний триггеров. Рис.3.6. Схема последовательностной части цифрового управляющего устройства Рис.3.7. 3.1.4 Синтез комбинационной части цифрового управляющего устройства 3.1.4.1Определение зависимости выходных сигналов цифрового управляющего устройства от входных сигналов и внутренних ...

... входов для каждого триггера: МДНФ счётчика: ; ; ; . · Синтезируем счётчик. Структурную схему: Принципиальную схему: Временные диаграммы счётчика: Синтез дешифратора Мы должны получить неполный ...

... в 60-х годах разрабатывались новые модели машин серии М для управляющих применений в различных отраслях народного хозяйства. В 70-х ИНЭУМ стал головной организацией по созданию серии малых управляющих ЭВМ — СМ ЭВМ. И.С. Брук был человеком выдающимся и весьма своеобразным. По стилю своей деятельности это был, скорее, ученый-одиночка, генератор идей, которые подхватывали и реализовывали его ...

... начинается фаза интерпретации команды. В зависимости от команды эта фаза может представлять собой, например, извлечение из памяти константы, необходимой для выполнения команды или извлечение из памяти номера регистра. В конце этой фазы процессор готов к выполнению команды. На этом начинается фаза выполнения. Фаза извлечения данных из памяти присутствует у команды занесения данных в аккумулятор, в ...

0 комментариев