Содержание

Введение

1. Задание

1.1 Список микроопераций

2. Описание функционирования МФР, как основного узла ОА

3. Разбиение множества МО на подмножества, сегментация соответствующего формата данных

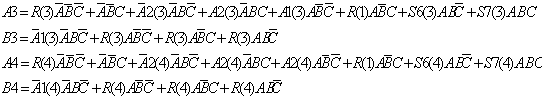

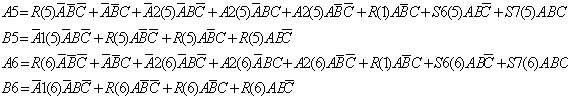

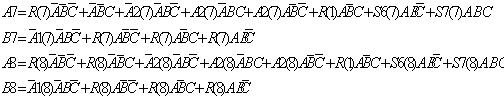

4. Формирование функций возбуждения для T триггера

4.1 Функции возбуждения

4.2 Сегментация

5. Синтез МФР

5.1 Краткое описание элементной базы К555

5.2 Описание структурной схемы МФР

6. Описание принципиальной схемы на элементах малой и средней степени интеграции

7. Описание принципиальной схемы на элементах малой и средней степени интеграции

7.1. Подготовка операндов

Введение

В данной курсовой работе рассчитан многофункциональный регистр (МФР). Задается 9 микроопераций (МО): 7 для входной шины и 2 для выходной шины.

Синтез регистра произведен на элементах малой и средней степени интеграции, а также на большой степени интеграции.

Использована различная элементная база: мультиплексоры, дешифратор, ПЗУ, программируемые логические матрицы, арифметико-логические устройства, элементы 2и 2и-не 3и 2или 2или-не 3или-не, и др.

По схеме с элементами большой степени интеграции рассчитана печатная плата, трассировка, расположение элементов и отверстий.

1. Задание

В данной курсовой работе необходимо спроектировать многофункциональный регистр (МФР), выполняющий заданный набор микроопераций, который и будет являться основным узлом синтезируемого операционного автомата. Вариант курсового проекта образуется путём задания определенного набора микроопераций (выбирается по таблице) и элементной базы.

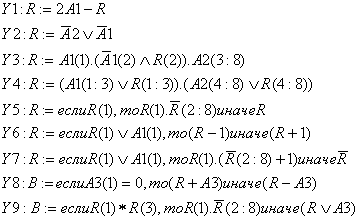

1.1 Список микроопераций

Согласно варианта задан следующий список микроопераций

7,11,15 (n=2), 19 (n=3),3134,36,45,49

Операция выполняемая схемой контроля:

x1: 2R>m; x2: R=1. .1, где m - двоичное представление суммы, последних двух цифр номера зачетки и числа 23.

№ варианта - 23, следовательно m=23+23=46=001011102

Содержание МО:

Тип триггера: T

Серия элементов: K555

2. Описание функционирования МФР, как основного узла ОА

Назначение операционного устройства (ОУ) - обработка текущих операндов, в соответствии с заданной МО и выдача результатов этой обработки. ОА может быть представлен в виде двух взаимодействующих автоматов: УА и ОА. Синтез УА был рассмотрен ранее, в курсовом проекте по ПТЦА. ОА состоит из регистров, сумматоров и других узлов, производящих прием, хранение и обработку информации, а также выдачу результата обработки во внешнюю среду и выдачу в УА и внешнюю среду осведомительных сигналов об особых значениях операндов или их отдельных разрядов (о знаках операндов, о равенстве нулю результата операции, об окончании работы, переполнении и т.п.).

Процесс функционирования во времени ОУ состоит из последовательности тактовых интервалов, в которых ОА производит определенные элементарные операции обработки слов: ОА выполняет некоторый набор элементарных преобразований информации: передачи слова из регистра в регистр, взятие обратного кода, сдвиг кода и т.п. В общем случае ОА может выполнять множество таких МО, но на практике реализуются те микрооперации, которые должен выполнять ОУ, и их количество ограничено. В каждом такте выполняется только одна МО. Границы тактов задаются длительностью синхросигнала.

УА обычно представляется в виде регистровой структуры, то есть совокупности МФР со своими шинами, КС, предназначенными для формирования функций возбуждения триггеров и выходных сигналов ОА.

Под МФР подразумевают регистр, способный выполнить некоторое множество МО Y={y1, y2... ym} над входными словами, а также над словами, которые хранились в регистре до начала выполнения МО. В каждом машинном такте регистр может выполнить либо только одну МО, либо не выполнить ни одной. Кроме стандартного набора МО для обычного регистра, в МФР используются и другие МО, предусматривающие предварительную обработку входных данных (арифметическую или / и логическую).

Таким образом МФР - это автомат с памятью, у которого входными, являются переменные А1, А2,... Ак и множество МО Y, а выходными - В1, В2,... Вs и Х. Для синтеза такого автомата проводят его декомпозицию, крайнем случаем которой является разбиение данного автомата на элементарные одноразрядные автоматы; при этом рассматривается n - автоматов с двумя состояниями.

В большинстве реальных случаев нет необходимости в полной декомпозиции, поскольку МО, это совокупность действий над группами разрядов (сегментами); таким образом декомпозиция сводится к разбиению поля МФР на сегменты, внутри которых действия, выполняемые над разрядами сегмента, идентичны.

3. Разбиение множества МО на подмножества, сегментация соответствующего формата данных

Множество выполняемых регистром МО Y={ y1, y2, y3, y4, y5, y6, y7, y8, y9} условно можно разбить на два подмножества:

Y1={y1, y2, y3, y4, y5, y6, y7} и Y2={ y8, y9}.

Первое множество включает в себя такие МО, в результате выполнения которых происходят изменения содержимого регистра. Эти МО описываются оператором присваивания

Рг: =f (A1, A2,A3, Рг),

где f - некоторая функция от значений слов, поступающих по входным шинам - A1, A2,A3, а также от содержимого регистра Рг, которое существовало в нем до момента выполнения данной МО.

К подмножеству Y2 отнесем такие МО, в результате выполнения которых не происходит изменение содержимого регистра, но осуществляется передача в некоторую совокупность выходных шин кодов, которые зависят, в общем случае, и от содержимого регистра Рг, и от кодов на входных шинах. Эти МО описываются оператором присваивания вида:

В: = Ф (Рг,A3),

где В - выходная шина, Ф - некоторая функция от содержимого регистра Рг и входной шины А3.

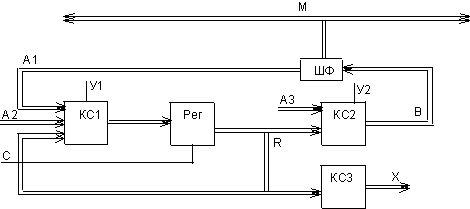

Структура МФР с учётом разбиения множества МО Y на подмножества Y1 и Y2 представлена на рис.1. Здесь первая комбинационная схема (КС1) управляется микрооперациями из подмножества Y1, а вторая (КС2) - из подмножества Y2, собственно регистр может быть синхронным либо асинхронным. Схемой КС3 вырабатываются признаки Х результата обработки регистром входных переменных А и, возможно предыдущего значения регистра. Методика разбиения на сегменты, то есть сегментация, основана на том, что поочередно рассматривается каждая МО, выполняемая МФР или шиной, при этом выявляются разряды регистра (шины), которые выполняют одну и ту же функцию. Затем рассматривается вся совокупность МО (при синтезе КС1-Y1, KC2-Y2) и производится пересечение исходных сегментов: при этом образуются новые сегменты, которые также составляют разрядное поле МФР либо шины.

Рис.1. Структура МФР

4. Формирование функций возбуждения для T триггера

4.1 Функции возбуждения

По заданию: тип триггера - T (синхронный):

| Q (t) | Q (t + 1) | T |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Некоторые МО я выполняю как для Д триггера (для упрощения схемы). Доказательство связи Д и Т триггеров:

| Q (t) | Q (t+1) | T |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| Q (t) | Q (t+1) |

|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Как видно из таблиц: Т триггер одинаков с "исключающим или".

![]()

где Q (t) = R и Q (t+1) = D

![]()

Синтез производился по следующему принципу:

Получаем то значение, в которое необходимо установить регистр.

Мультиплексором производим выборку нужного значения в зависимости от используемой микрооперации.

Значение разряда регистра полученное на выходе мультиплексора необходимо подать на соответствующий разряд триггера. Кстати необходимо отметить и то, что если не действует ни одна из микроопераций, регистр должен сохранять своё значение.

микрооперация Y1:

данные функции возбуждения будут реализованы на сумматоре S1 (i) =A1 (i-1) - R (i)

| S1 | R | R (t+1) | T |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 0 |

R (t+1) (i) =S1 (i), i=1: 7

T (i) = ![]() 1 (i) +S1 (i) = 1, i = 1: 7

1 (i) +S1 (i) = 1, i = 1: 7![]()

R (t+1) (8) = 0

| R | R (t+1) | T |

| 0 | 0 | 0 |

| 1 | 0 | 1 |

T (8) = R (8)

микрооперация Y2:

T (i) = ![]() , i = 1: 8

, i = 1: 8

микрооперация Y3:

T (1) = A1 (1)

T (2) = ![]()

T (i) = A2 (i), i = 3: 8

микрооперация Y4:

T (i) = A1 (i) ![]() R (i), i = 1: 3

R (i), i = 1: 3

T (j) = A2 (j) ![]() R (j), i = 4: 8

R (j), i = 4: 8

микрооперация Y5:

![]()

![]()

![]() , i = 2: 8

, i = 2: 8

микрооперация Y6:

данные функции возбуждения будут реализованы на сумматоре

V = S6 = R (i) +R (1) ![]() A1 (1). R (1)

A1 (1). R (1) ![]() A1 (1). R (1)

A1 (1). R (1) ![]() A1 (1). R (1)

A1 (1). R (1) ![]() A1 (1). R (1)

A1 (1). R (1) ![]() A1 (1). R (1)

A1 (1). R (1) ![]() A1 (1). R (1)

A1 (1). R (1) ![]() A1 (1).1

A1 (1).1

T (i) = S6 (i) ![]() , i = 1: 8

, i = 1: 8

микрооперация Y7:

![]()

T (1) = ![]()

T (i) = S7 (i), i = 2: 8

Каждую МО ![]()

Микрооперации у8 и у9 не изменяют содержимое регистра, а формируют шину В:

микрооперация Y8:

сумматоры: N = S8 = R+A3 и E = S81 = R-A3

B = ![]() , i = 1: 8

, i = 1: 8

микрооперация Y9:

![]()

![]()

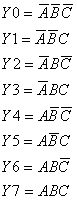

4.2 Сегментация

Так как многие операции для разных разрядов одинаковы, то имеет смысл провести сегментацию.

| Y1 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y2 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y3 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y4 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y5 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y6 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y7 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| R | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y8 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Y9 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| B | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

5. Синтез МФР

5.1 Краткое описание элементной базы К555

Интегральные микросхемы серии К555 изготовляются по ТТЛШ - технологии, которая позволяет получить по сравнению с распространенными сериями микросхем минимальное значение произведения быстродействия на рассеиваемую мощность. Это позволяет при разработке аппаратуры уменьшить плотность токов в шинах питания, уменьшить рассеиваемую мощность, повысить надежность изделий радиоэлектроники. Среди микросхем данной серии имеются микросхемы с тремя устойчивыми состояниями. Помимо состояний высокого и низкого уровней данные микросхемы могут переходить в третье состояние высокого выходного сопротивления. Это свойство данных микросхем позволяет организовать ПРОВОДНОЕ ИЛИ. При работе на магистраль нескольких микросхем с тремя состояниями только одна из них может переходить в проводящее состояние, в то время как остальные должны находиться в состоянии высокого выходного сопротивления.

Для построения будут использованы следующие интегральные микросхемы (ИМС) серии.

Будет использоваться JK-триггер серии К555TB6.

При объединении входов J и K мы получаем Т триггер

Микросхема представляет собой два независимых тактируемых JK-триггера cо сбросом с установкой в 0 и 1. Считывание информации со входов J и K происходит во время положительного перепада на входе С, а на выходы она передается во время отрицательного перепада. Логические уровни на J и K не должны изменяться, пока на С высокий уровень! Если соединить входы J и K триггер будет работать как обычный счетный (делить частоту на 2).

Будет использоваться двоичный сумматор серии К555ИМ6 - Предназначен для выполнения арифметических операций сложения. Операция сложения положительных двоичных чисел определяется правилами двоичной арифметики

Микросхема К555ИМ6 - полный четырехразрядный двоичный сумматор. Ее логика работы: на входы А1 - А8 подается код одного из суммируемых чисел (А1 - младший разряд, А8 - старший),

на входы В1-В8 - код второго числа, на вход С - перенос от предыдущей микросхемы. Код суммы формируется на выходах S1 - S8, перенос - на выходе Р. У микросхемы, суммирующей младшие разряды многоразрядных двоичных чисел, вход С следует соединить с общим проводом.

Будем использовать мультиплексор серии К555КП7 - микросхема содержит двоичный дешифратор для выбора одного из восьми источников данных. Микрасхема представляет собой селектор - мультиплексор из 8 в 1 и в зависимости от установленного на входах А В С кода разрешает прохождение сигнала на выход Y только обного из 8 информационных входов.

Программируемая логическая матрица (ПЛМ) - ПЛМ, имеет параметры n=16, m=48 и k=8, где n - число входов, а k - число выходов. Логические элементы И выполнены на диодах Шоттки, на 48 эмитерных транзисторах. На выбранном типе ПЛМ можно реализовать КС, имеющую 16 входов и 8 выходов.

Использовалась ПЛМ из 556 серии К556РТ2

5.2 Описание структурной схемы МФРСтруктурную схему МФР можно представить в виде соединения пяти основных функциональных блоков:

Блок формирования ФВ для триггеров МФР.

Представляет собой КС, которая реализована с использованием элементов И-НЕ, сумматоров, элементов 2-ИЛИ и 2-И и др.

На входы блока подаются сигналы МО (информация о том, какая МО из множества МО должна выполниться в данном такте) в двоично-кодированной форме, через шифратор, преобразующий номер микрооперации из унитарного кода в двоичный. Также на входы блока подаются значения шин А1 и А2, сигналы, снимаемые с выхода блока (то есть состояние регистра в предыдущий момент времени), также подаются на входы блока формирования ФВ.

Блок формирования сигналов, действующих в шине.

Представляет собой КС, которая реализована на элементах типа 2-ИЛИ, 2-И, 2-ИСКЛ. ИЛИ и др. На входы блока подаются сигналы МО, значения шины А3и состояния регистра. Выходом блока является сигналы, действующие в шине на протяжении данного такта.

Блок памяти.

Представляет собой восьмиразрядный регистр, собранный на 8 J-K триггерах К555ТВ6, с соединенными входами и полученным Т триггером. Регистр осуществляет запоминание кода, сформированного блоком формирования ФВ, которое осуществляется по переднему фронту синхроимпульса. На информационные входы каждого триггера подаются сигналы с выходов соответствующей КС блока формирования ФВ.

Шинный формирователь.

Типа К555АП6. Служит для связи МФР с магистралью. В зависимости от управляющего сигнала данных, либо снимаются с магистрали, либо подаются на нее.

6. Описание принципиальной схемы на элементах малой и средней степени интеграции

Синтез принципиальной схемы выполняется с помощью элементов малой степени интеграции, таких как: простейшие логические элементы - И-НЕ, ИЛИ, Исключающее ИЛИ, а также при помощи элементов средней степени интеграции, к ним можно отнести мультиплексоры (МП), двоичные сумматоры.

Регистр - это электронный узел, состоящий из множества триггеров (в нашем случае их число равно 8), а с другой - это аппарат, для выполнения некоторого набора микроопераций (МО), под влиянием синхроимпульса (СИ) триггер переходит из одного состояния в другое. Кроме того СИ указывает, в какой момент времени выполнить эту операцию.

Управляющие сигналы МО (y1,..., y9) поступают с входов (шина y) и при помощи схемы декодирования преобразуются из унитарного кода в двоичный (A, В, С). В данном случае получаем унитарный код с помощью шифратора К555ИВ1. Управляющий сигнал показывает что конкретно должен выполнить регистр и соответственно его триггер, то есть все Fr должны быть вычислены до момента появления управляющего сигнала. Рассмотрим структуру разряда МФР. Здесь должны быть предусмотрены вычислители и узел, позволяющий выбирать из всех результатов тот который соответствует данному управляющему сигналу.

Входные переменные А1 (1: 8) поступают с выходов шинного формирователя в шину А1. Для вычисления Fr используем различные логические элементы. В качестве коммутатора используется мультиплексор 8а1, который формирует функции возбуждения Т (1), Т (2), … Т (8) для триггера.

Структура КС2 результатом которой является выходная переменная без памяти В (интерпретирующая шину) подобна структуре КС1. Разряд также состоит из вычислителей реализованных на простейших логических элементах. Входными переменными служат переменные A3 (1: 8) поступающих со входа схемы в шину А3 и выходы регистра R (1: 8). Результат их преобразования в КС2 появляется в этом же такте в отличии от КС1 (где результат появляется лишь в следующем такте). Выходные переменные поступают в шину В.

7. Описание принципиальной схемы на элементах малой и средней степени интеграции

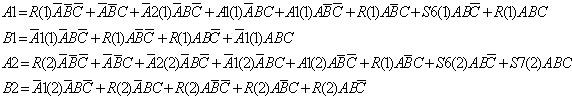

Для синтеза схемы на элементах большой степени интеграции удобно использовать ПЛМ и АЛУ.

Всю выборку микрооперации, подготовку операндов удобно выполнять на ПЛМ, т.к число переменных, используемых в ПЛМ довольно велико (до 48 конъюнкций в одном выражении). А на АЛУ проводить арифметические или логические операции.

С помощью ПЛМ можно исключить из схемы мультиплексоры, все логические элементы. Полученную схему легче реализовать на печатной плате так как уменьшается число входов/выходов т.е. уменьшается число дорожек. В схеме, собранной на элементах большой степени интеграции используется ПЛМ, матрицы программирования которых представлены на рисунках ниже.

7.1. Подготовка операндов

Для наглядности синтеза удобно нарисовать следующую таблицу:

| Y | S3 | S2 | S1 | S0 | M | CR | Операция |

| Y0 | 1 | 1 | 1 | 1 | 1 | 1 | A |

| Y1 | 1 | 1 | 1 | 1 | 1 | 1 | A |

| Y2 | 1 | 1 | 1 | 0 | 1 | 1 | A+B |

| Y3 | 1 | 0 | 1 | 1 | 1 | 1 | A*B |

| Y4 | 1 | 1 | 1 | 0 | 1 | 1 | A+B |

| Y5 | 0 | 1 | 1 | 0 | 1 | 1 |

|

| Y6 | 0 | 1 | 1 | 0 | 1 | 1 |

|

| Y7 | 1 | 1 | 1 | 0 | 1 | 1 | A+B |

| Y81 | 0 | 0 | 0 | 1 | 0 | 0 | S A+B |

| Y82 | 0 | 1 | 1 | 0 | 0 | 0 | S A-B |

| Y91 | 1 | 1 | 1 | 1 | 1 | 1 | A |

| Y92 | 1 | 1 | 1 | 0 | 1 | 1 | A+B |

Для входной шины:

![]()

![]()

S1 = 1

![]()

M = 1

CR = 1

Для выходной шины:

S3 = M = CR = Y9

S2 = S1 = A3 (1) *Y8 + Y9

S0 = ![]() 3 (1) *Y8 + R (1) *R (3) *Y9

3 (1) *Y8 + R (1) *R (3) *Y9

Так как для кодировки сигналов операций будет использован двоичный шифратор 8®3, то введём следующее соответствие:

Для получения функций, которые нужно сформировать на ПЛМ удобно построить следующую таблицу в которой прописаны операнды для АЛУ в каждый момент времени. Причём y0 - случай, когда нет сигнала на выполнение операций:

| A1 | B1 | A2 | B2 | A3 | B3 | A4 | B4 | A5 | B5 | A6 | B6 | A7 | B7 | A8 | B8 | |

| Y0 | R (1) | X | R (2) | X | R (3) | X | R (4) | X | R (5) | X | R (6) | X | R (7) | X | R (8) | X |

| Y1 | 1 | X | 1 | X | 1 | X | 1 | X | 1 | X | 1 | X | 1 | X | R (8) | X |

| Y2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Y3 | A1 (1) | X |

| R (2) | A2 (3) | X | A2 (4) | X | A2 (5) | X | A2 (6) | X | A2 (7) | X | A2 (8) | X |

| Y4 | A1 (1) | R (1) | A1 (2) | R (2) | A1 (3) | R (3) | A2 (4) | R (4) | A2 (5) | R (5) | A2 (6) | R (6) | A2 (7) | R (7) | A2 (8) | R (8) |

| Y5 | R (1) | X | R (1) | R (2) | R (1) | R (3) | R (1) | R (4) | R (1) | R (5) | R (1) | R (6) | R (1) | R (7) | R (1) | R (8) |

| Y6 | S6 (1) | R (1) | S6 (2) | R (2) | S6 (3) | R (3) | S6 (4) | R (4) | S6 (5) | R (5) | S6 (6) | R (6) | S6 (7) | R (7) | S6 (8) | R (8) |

| Y7 | R (1) |

| S7 (2) | X | S7 (3) | X | S7 (4) | X | S7 (5) | X | S7 (6) | X | S7 (7) | X | S7 (8) | X |

На первой ПЛМ будут реализованы следующие функции:

![]() ,

, ![]()

![]()

На второй ПЛМ будут реализованы следующие функции:

На третьей ПЛМ будут реализованы следующие функции:

P = R (1) ![]() A1 (1)

A1 (1)

На четвертой ПЛМ будут реализованы следующие функции:

L = Y8 + Y9

H = ![]() 8 *

8 * ![]() 9

9

Реализация шины В.

Для получения функций, которые нужно сформировать на ПЛМ удобно построить следующую таблицу в которой прописаны операнды для АЛУ в каждый момент времени.

| W1 | V1 | W2 | V2 | W3 | V3 | W4 | V4 | W5 | V5 | W6 | V6 | W7 | V7 | W8 | V8 | |

| Y81 | R (1) | A3 (1) | R (2) | A3 (2) | R (3) | A3 (3) | R (4) | A3 (4) | R (5) | A3 (5) | R (6) | A3 (6) | R (7) | A3 (7) | R (8) | A3 (8) |

| Y82 | R (1) | A3 (1) | R (2) | A3 (2) | R (3) | A3 (3) | R (4) | A3 (4) | R (5) | A3 (5) | R (6) | A3 (6) | R (7) | A3 (7) | R (8) | A3 (8) |

| Y91 | R (1) | X |

| X |

| X |

| X |

| X |

| X |

| X |

| X |

| Y92 | R (1) | A3 (1) | R (2) | A3 (2) | R (3) | A3 (3) | R (4) | A3 (4) | R (5) | A3 (5) | R (6) | A3 (6) | R (7) | A3 (7) | R (8) | A3 (8) |

Y81 ![]() A3 (1) = 0

A3 (1) = 0

Y82 ![]() A3 (1) = 1

A3 (1) = 1

Y91 ![]() R (1) *R (3) = 1

R (1) *R (3) = 1

Y92 ![]() R (1) *R (3) = 0

R (1) *R (3) = 0

На пятой ПЛМ, реализующую шину В получим:

W1 = R (1) *Y8 + R (1) *Y9

V1 = A3 (1) *Y8 + (A3 (1) * (![]() )) *Y9

)) *Y9

S3 = M = CR = Y9

S2 = S1 = A3 (1) *Y8 + Y9

S0 = ![]() 3 (1) *Y8 + R (1) *R (3) *Y9

3 (1) *Y8 + R (1) *R (3) *Y9

W2 = R (2) *Y8 + (![]() (2) *R (1) *R (3) +R (2) * (

(2) *R (1) *R (3) +R (2) * (![]() )) *Y9

)) *Y9

V2 = A3 (2) *Y8 + (A3 (2) * (![]() )) *Y9

)) *Y9

W3 = R (3) *Y8 + R (3) *Y9

На шестой ПЛМ, реализующую шину В получим:

V3 = A3 (3) *Y8 + (A3 (3) * (![]() )) *Y9

)) *Y9

W4 = R (4) *Y8 + (![]() (4) *R (1) *R (3) +R (4) * (

(4) *R (1) *R (3) +R (4) * (![]() )) *Y9

)) *Y9

V4 = A3 (4) *Y8 + (A3 (4) * (![]() )) *Y9

)) *Y9

W5 = R (5) *Y8 + (![]() (5) *R (1) *R (3) +R (5) * (

(5) *R (1) *R (3) +R (5) * (![]() )) *Y9

)) *Y9

V5 = A3 (5) *Y8 + (A3 (5) * (![]() )) *Y9

)) *Y9

W6 = R (6) *Y8 + (![]() (6) *R (1) *R (3) +R (6) * (

(6) *R (1) *R (3) +R (6) * (![]() )) *Y9

)) *Y9

V6 = A3 (6) *Y8 + (A3 (6) * (![]() )) *Y9

)) *Y9

На седьмой ПЛМ, реализующую шину В получим:

W7 = R (7) *Y8 + (![]() (7) *R (1) *R (3) +R (7) * (

(7) *R (1) *R (3) +R (7) * (![]() )) *Y9

)) *Y9

V7 = A3 (7) *Y8 + (A3 (7) * (![]() )) *Y9

)) *Y9

W8 = R (8) *Y8 + (![]() (8) *R (1) *R (3) +R (8) * (

(8) *R (1) *R (3) +R (8) * (![]() )) *Y9

)) *Y9

V8 = A3 (8) *Y8 + (A3 (8) * (![]() )) *Y9

)) *Y9

0 комментариев