Микроконтроллеры AVR

Введение

Однокристальные микроконтроллеры находят широкие применение в самых разнообразных сферах: от измерительных приборов, фотоаппаратов и видеокамер, принтеров, сканеров и копировальных аппаратов до изделий электронных развлечений и всевозможной домашней техники.

Со времени появления первых микропроцессоров в 1970-х годах их сложность постоянно возрастала за счет появления новых аппаратных решений и добавления новых команд, предназначенных для решения новых задач. Так постепенно сложилась архитектура, получившая впоследствии название CISC (Complete Instruction Set Computers – компьютеры со сложным набором команд). В дальнейшем обозначилось и нашло активное развитие еще одно направление: архитектура RISC (Reduced Instruction Set Computers – компьютеры с сокращенным набором команд). Именно к этой архитектуре относятся микроконтроллеры AVR от компании Atmel и PIC от компании Microchip, которым посвящена эта книга.

Основное преимущество RISC-процессоров заключается в том, что они просты, выполняют ограниченный набор команд, и, как следствие, очень быстродействующие. Это позволяет снизить стоимость и сложность их программирования.

Обратной стороной RISC-архитектуры стала необходимость создания дополнительных команд на ассемблере, которые у CISC-устройств реализованы в аппаратной части. Например, вместо того, чтобы просто вызвать команду деления, которая характерна для устройств CISC, разработчику, имеющему дело с RISC-процессором, приходится применять несколько последовательных команд вычитания. Однако подобный недостаток с лихвой компенсируется ценой и скоростью работы RISC-устройств. Кроме того, если создавать программы на языке С, то подобные проблемы вообще перестают иметь какое-либо значение для разработчика, поскольку они решаются компилятором, который автоматически генерирует весь недостающий ассемблерный код.

На заре возникновения микропроцессоров разработка программного обеспечения происходила исключительно на том или ином языке ассемблера, ориентированном на конкретное устройство. По сути, такие языки представляли собой символьные мнемоники соответствующих машинных кодов, а перевод мнемоники в машинный код выполнялся транслятором. Однако главный недостаток ассемблерных языков заключается в том, что каждый из них привязан к конкретному типу устройств и логике его работы. Кроме того, ассемблер сложен в освоении, что требует достаточно больших усилий для его изучения, которые, к тому же, оказываются потраченными впустую, если впоследствии потребуется перейти на использование микроконтроллеров других производителей.

Язык С, являясь языком высокого уровня, лишен подобных недостатков и может использоваться для программирования любого микропроцессора, для которого есть компилятор с языка С. В языке С все низкоуровневые операции, выполняемые компьютерами, представлены в виде абстрактных конструкций, позволяющих разработчикам сосредоточиться на программировании одной лишь логики, не заботясь о машинном коде. Изучив язык С, можно легко переходить от одного семейства микроконтроллеров к другому, тратя гораздо меньше времени на разработку.

1. Архитектура микроконтроллеров AVR и PIC

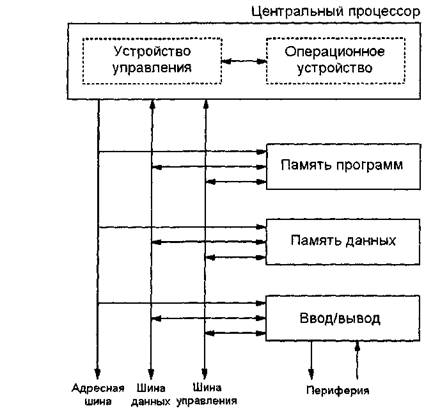

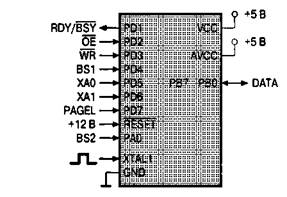

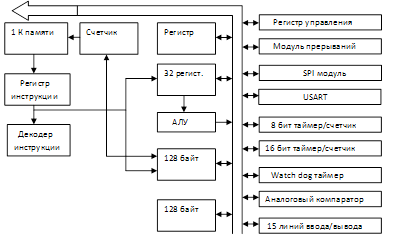

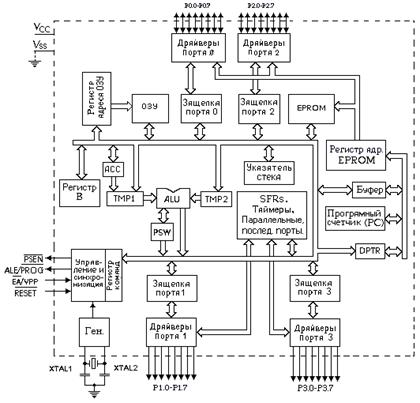

В общем, все микроконтроллеры построены по одной схеме. Система управления, состоящая из счетчика команд и схемы декодирования, выполняет считывание и декодирование команд из памяти программ, а операционное устройство отвечает за выполнение арифметических и логических операций; интерфейс ввода/вывода позволяет обмениваться данными с периферийными устройствами; и, наконец, необходимо иметь запоминающее устройство для хранения программ и данных (рис. 1.1).

Рис. 1.1. Обобщенная структура микроконтроллера

Будем рассматривать микроконтроллеры в общем, не привязываясь к какому-либо конкретному типу микроконтроллеров AVR, поэтому ниже будут рассмотрены только общие для большинства микроконтроллеров особенности архитектуры памяти, вопросы ввода/вывода, обработки прерываний, сброса и др.

Память микроконтроллеров AVRВ микроконтроллерах AVR память реализована по Гарвардской архитектуре, что подразумевает разделение памяти команд и данных. Это означает, что обращение к командам осуществляется независимо от доступа к данным. Преимуществом такой организации является повышение скорости доступа к памяти.

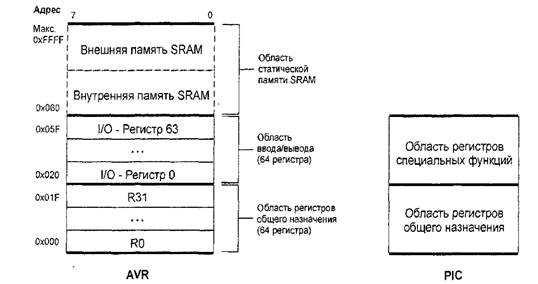

Память данныхПамять данных предназначена для записи/чтения данных, используемых программами. Является энергозависимой, то есть, при отключении питания микроконтроллера все хранимые в ней данные, будут потеряны. В микроконтроллерах AVR память данных имеет более развитую структуру по сравнению с микроконтроллерами PIC, что показано на рис. 2.1.

Здесь и далее шестнадцатеричные числа будут представлены в форме, принятой в языке С: с префиксом 0х.

Рис. 2.1. Структура памяти данных в микроконтроллерах AVR и PIC

Область статической памяти SRAM (Static Random Access Memory) обозначена на рис. 2.1 пунктиром, поскольку используется не всеми микроконтроллерами AVR (это относится как к внутренней, так и к внешней SRAM). Ее начальный адрес – 0x060, а верхний адрес – разный в различных устройствах.

В некоторых микроконтроллерах AVR можно увеличивать пространство памяти SRAM посредством подключения внешних блоков памяти вплоть до 64 Кбайт, однако для этого приходится пожертвовать портами А и С, которые в этом случае применяются для передачи данных и адресов.

Регистры общего назначенияОбласть регистров общего назначения (рабочих регистров) предназначена для временного хранения переменных и указателей, используемых процессором для выполнения программ. В микроконтроллерах AVR она состоит из 32 восьмиразрядных регистров (диапазон адресов 0x000 – 0x01F). В микроконтроллерах PIC регистры общего назначения также восьмиразрядные, однако их количество и диапазон адресов зависят от конкретного типа устройства.

В программах, написанных на языке С, непосредственное обращение к регистрам общего назначения обычно не требуется, если только не используются фрагменты на языке ассемблера.

Регистры специальных функций микроконтроллеров PICРегистры специальных функций используются в микроконтроллерах PIC для управления различными операциями. Как и в случае с регистрами общего назначения, их количество и адресация отличаются от устройства к устройству. В программах, написанных на языке С, непосредственное обращение к регистрам специальных функций обычно не требуется, если только не используются фрагменты на языке ассемблера.

Область ввода/вывода микроконтроллеров AVRОбласть ввода/вывода микроконтроллеров AVR содержит 64 регистра, используемых для управления или хранения данных периферийных устройств. К каждому из этих регистров можно обращаться по адресу ввода/вывода (начиная с 0x000) или по адресу SRAM (в этом случае к адресу ввода/вывода следует прибавить 0x020). В программах на языке С обычно используются условные имена регистров ввода/вывода, а адреса имеют значение только для программ на языке ассемблера.

Имена, адреса ввода/вывода и SRAM, а также краткое описание регистров из области ввода/вывода микроконтроллеров AVR представлены в табл. 2.1. При этом следует отметить, что в различных моделях микроконтроллеров некоторые из перечисленных регистров не используются, а адреса, не указанные в табл. 2.1, зарезервированы компанией Atmel для использования в будущем.

Таблица 2.1. Описание регистров из области ввода/вывода

| Имя регистра | Адрес ввода/ вывода | Адрес SRAM | Описание |

|

| ACSR | 0x08 | 0x28 | Регистр управления и состояния аналогового компаратора |

|

| UBRR | 0x09 | 0x29 | Регистр скорости передачи данных через UART |

|

| UCR | 0х0А | 0х2А | Регистр управления приемопередатчиком UART |

|

| USR | 0x0В | 0x2В | Регистр состояния приемопередатчика UART |

|

| UDR | 0х0С | 0х2С | Регистр данных приемопередатчика UART |

|

| SPCR | 0x0D | 0x2D | Регистр управления интерфейсом SPI |

|

| SPSR | 0х0Е | 0х2Е | Регистр состояния интерфейса SPI |

|

| SPDR | 0x0F | 0x2F | Регистр ввода/вывода данных интерфейса SPI |

|

| PIND | 0x10 | 0x30 | Выводы порта D |

|

| DDRD | 0x11 | 0x31 | Регистр направления передачи данных порта D |

|

| PORTD | 0x12 | 0x32 | Регистр данных порта D |

|

| PINC | 0x13 | 0x33 | Выводы порта С |

|

| DDRC | 0x14 | 0x34 | Регистр направления передачи данных порта С |

|

| PORTC | 0x15 | 0x35 | Регистр данных порта С |

|

| PINB | 0x16 | 0x36 | Выводы порта В |

|

| DDRB | 0x17 | 0x37 | Регистр направления передачи данных порта В |

|

| PORTB | 0x18 | 0x38 | Регистр данных порта В |

|

| PINA | 0x19 | 0x39 | Выводы порта А |

|

| DDRA | 0x1А | 0х3А | Регистр направления передачи данных порта А | |

| PORTA | 0x1В | 0х3В | Регистр данных порта А | |

| EECR | 0x1С | 0х3С | Регистр управления памяти EEPROM | |

| EEDR | 0x1D | 0x3D | Регистр данных памяти EEPROM | |

| EEARL | 0x1Е | 0х3Е | Регистр адреса памяти EEPROM (младший байт) | |

| EEARH | 0x1F | 0x3F | Регистр адреса памяти EEPROM (старший байт) | |

| WDTCR | 0x21 | 0x41 | Регистр управления сторожевым таймером | |

| ICR1L | 0x24 | 0x44 | Регистр захвата таймера/счетчика Т/С1 (младший байт) | |

| ICR1H | 0x25 | 0x45 | Регистр захвата таймера/счетчика Т/С1 (младший байт) | |

| OCR1BL | 0x28 | 0x48 | Регистр сравнения В таймера Т/С1 (младший байт) | |

| OCR1BH | 0x29 | 0x49 | Регистр сравнения В таймера Т/С1 (старший байт) | |

| OCR1AL | 0х2А | 0х4А | Регистр сравнения А таймера Т/С1 (младший байт) | |

| OCR1AH | 0x2В | 0x4В | Регистр сравнения А таймера Т/С1 (старший байт) | |

| TCNT1L | 0х2С | 0х4С | Счетный регистр таймера/счетчика Т/С1 (младший байт) | |

| TCNT1H | 0x2D | 0x4D | Счетный регистр таймера/счетчика Т/С1 (старший байт) | |

| TCCR1B | 0x2Е | 0х4Е | Регистр управления В таймера/счетчика Т/С1 | |

| TCCR1A | 0x2F | 0x4F | Регистр управления А таймера/счетчика Т/С1 | |

| TCNT0 | 0x32 | 0x52 | Счетный регистр таймера/счетчика Т/С0 | |

| TCCR0 | 0x33 | 0x53 | Регистр управления таймера/счетчика Т/С0 | |

| MCUCR | 0x35 | 0x55 | Регистр управления микроконтроллером | |

| TIFR | 0x38 | 0x58 | Регистр флагов прерываний от таймеров/счетчиков | |

| TIMSK | 0x39 | 0x59 | Регистр маскирования прерываний от таймеров | |

| GIFR | 0х3А | 0х5А | Общий регистр флагов прерываний | |

| GIMSK | 0х3В | 0x5В | Общий регистр маскирования прерываний | |

| SPL | 0x3D | 0x5D | Указатель стека (младший байт) | |

| SPH | 0х3Е | 0х5Е | Указатель стека (старший байт) | |

| SREG | 0x3F | 0x5F | Регистр состояния | |

Регистр состояния содержит флаги условий микроконтроллеров AVR и располагается в области ввода/вывода по адресу $3F (адрес SRAM – $5F). После подачи сигнала сброса он инициализируется нулями.

В микроконтроллерах AVR для обозначения результата выполнения операций используются восемь различных флагов:

-разряд 0 (С) – флаг переноса (Carry); указывает на переполнение (перенос) после выполнения арифметической или логической операции;

-разряд 1 (Z) – нулевой флаг (Zero); всегда устанавливается, если результат арифметической или логической операции равен нулю; сбрасывается, если результат операции не равен нулю;

-разряд 2 (N) – флаг отрицательного результата (Negative); указывает на отрицательный результат после выполнения арифметической или логической операции;

-разряд 3 (V) – флаг переполнения при вычислениях в дополнительных кодах (Two's complement Overflow); поддерживает арифметику дополнительных кодов (арифметика кодов с дополнением до двух); устанавливается, если при выполнении соответствующей операции происходит переполнение, в противном случае – сбрасывается;

-разряд 4 (S) – флаг знака (Sign); S = NÅV – связь флагов N и V с помощью операции "Исключающее ИЛИ"; флаг знака может применяться для определения фактического результата арифметической операции;

-разряд 5 (Н) – флаг половинного переноса (Half Carry); указывает на переполнение в младшем полубайте (разряды 0...3 байта данных); устанавливается, когда происходит перенос из младшего полубайта в старший, в противном случае – сбрасывается;

-разряд 6 (Т) – флаг копирования (Transfer or Copy); предназначен для свободного применения программистом (например, в качестве буфера);

-разряд 7 (I) – общее разрешение прерываний (Global Interrupt); если прерывания, как таковые, должны быть разрешены, то должен быть установлен разряд 7 регистра состояния (в лог. 1).

Внутренняя и внешняя память SRAM микроконтроллеров AVRПамять SRAM микроконтроллеров AVR предназначена для хранения тех данных, которые не помещаются в рабочих регистрах, а также для организации программного стека. Данные обычно сохраняют в SRAM, начиная с первых адресов, а стеку соответствуют верхние адреса.

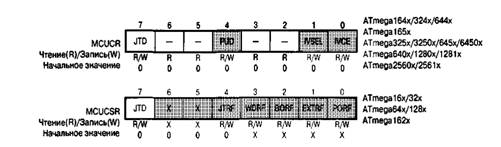

Если объема внутренней памяти SRAM недостаточно, то в некоторых микроконтроллерах AVR его можно увеличить до 64 Кбайт посредством подключения внешних блоков памяти. Для этого в регистре MCUCR (адрес в области ввода/вывода – $35, адрес в SRAM – $55) следует установить в лог. 1 разряд SRE (разряд 7). После установки этого разряда порты А и С будут выступать в качестве шины адреса и шины данных, а выводы 7 и 6 порта D – в качестве управляющих сигналов чтения /RD и, соответственно, записи /WR для внешней памяти SRAM), независимо от того, какие направления передачи данных установлены для этих портов в соответствующих регистрах направления передачи данных.

СтекСтек – это особая область памяти данных, используемая процессором для временного хранения адресов возврата из подпрограмм, промежуточных результатов вычислений и др. В микроконтроллерах PIC и некоторых микроконтроллерах AVR стек реализован аппаратно – для этого выделено отдельное запоминающее устройство фиксированного объема в несколько (или несколько десятков) байт. Для микроконтроллеров AVR компиляторы языка С (например, при обращении к подпрограммам) могут также создавать один или более стеков программно, начиная с верхних адресов области SRAM.

Стек действует по принципу LIFO – "Last In, First Out", что означает "последним вошел, первым вышел". Это означает, что новые данные вначале помещаются на вершину (первый уровень) стека, а затем, с поступлением следующих данных, "проталкиваются" на его нижние уровни. Извлечение из стека происходит в обратном порядке: вначале считываются данные, помещенные последними на вершину, после чего данные, размещенные на нижних уровнях, как бы "выталкиваются" на один уровень вверх. Ячейка памяти, которая является в данный момент вершиной стека, адресуется указателем стека (для AVR – регистровой парой SPL, SPH).

Поскольку область памяти данных, отводимая для программного стека, ограничивается только объемом памяти SRAM, при написании программ следует следить за тем, чтобы стек не становился слишком большим, затирая полезные данные.

Память программПамять программ как в микроконтроллерах AVR, так и в микроконтроллерах PIC реализована по технологии Flash–EPROM, которая подразумевает программирование пользователем и вытирание электрическим способом. Размер этой памяти варьируется в зависимости от микроконтроллера и обычно составляет несколько Кбайт командных слов.

Флэш–память является энергонезависимой, то есть, сохраняет записанную в нее информацию даже после отключения питания микроконтроллера. Несмотря на то, что память этого типа – программируемая, для записи в нее используются только внешние аппаратные средства, поэтому с точки зрения программиста можно сказать, что память программ доступна только для чтения.

Адресация команд в памяти программ реализуется с помощью специального регистра – счетчика команд, разрядность которого определяет допустимый размер этой памяти. Разрядность ячеек памяти программ, в зависимости от типа микроконтроллера, может составлять 14…16 бит.

Кроме того, следует отметить, что в микроконтроллерах PIC в первых ячейках памяти программ (начиная с адреса 0x0000) содержатся векторы (адреса перехода) сброса и прерываний.

Память EEPROM микроконтроллеров AVRМногие микроконтроллеры AVR оборудованы встроенной памятью EEPROM – электрически перезаписываемой энергонезависимой памятью. Хотя эта память и допускает запись, она редко используется для хранения программных переменных, поскольку, во-первых, медленнодействующая, и, во-вторых, имеет ограниченный (хотя и довольно большой) цикл перезаписи.

Учитывая вышесказанное, память EEPROM используют, преимущественно, для хранения данных, которые не должны быть потеряны даже при потере питания. Это очень удобно, к примеру, при калибровке измерительных приборов, работающих под управлением микроконтроллеров, у которых в памяти EEPROM в процессе настройки сохраняются параметры корректировки. Благодаря этому, в большинстве случаев полностью отпадает необходимость в настроечных потенциометрах и триммерах.

В отличие от флэш-памяти, для записи/чтения памяти EEPROM нет необходимости в специальном программаторе – эти операции доступны программно и допускают побайтную передачу данных с помощью регистра управления EECR, регистра данных EEDR и регистровой пары EEARL, EEARH, определяющей адрес ячейки памяти (см. табл. 1.1).

Запись байта данных в память EEPROM осуществляется по следующей схеме:

-удостовериться, что в разряде EEWE (разряд 1) регистра EECR находится лог. 0 (разрешение записи);

-записать адрес ячейки EEPROM в регистр EEAR;

-записать байт данных в регистр EEDR;

-установить в лог. 1 разряд EEMWE (разряд 2) регистра EECR;

-установить в лог. 1 разряд ЕЕWE (разряд 1) регистра EECR, чтобы активизировать процесс записи.

По окончанию цикла программирования разряд EEWE аппаратно автоматически сбрасывается в лог. 0. Программа пользователя должна непрерывно опрашивать этот разряд, ожидая появления лог. 0, прежде чем приступить к программированию следующего байта.

Чтение байта данных из памяти EEPROM осуществляется по такой схеме:

-записать адрес ячейки EEPROM в регистр EEAR;

-установить в лог. 1 разряд EERE (разряд 0) регистра EECR, чтобы активизировать процесс чтения;

-по окончанию считывания разряда EERE аппаратное обеспечение считывает требуемый байт в регистр EEDR, после чего уже нет необходимости вновь опрашивать разряд EERE, поскольку считывание длится только один цикл такта системной синхронизации.

Перед началом операции чтения программа пользователя должна постоянно опрашивать разряд EEWE и ждать появления лог. 0. Если во время программирования памяти EEPROM в соответствующий регистр будет записан новый адрес или данные, то еще продолжающийся процесс программирования будет прерван, и результат будет неопределенным!

Обработка прерыванийПрерывания – это вызовы определенных функций, генерируемые, главным образом, аппаратной частью микроконтроллера. В результате прерывания выполнение программы останавливается, и происходит переход к соответствующей подпрограмме обработки прерывания.

Прерывания бывают внутренними и внешними. Источниками внутреннего прерывания являются встроенные модули микроконтроллера (например, таймер/счетчик или сторожевой таймер). Внешние прерывания вызываются сбросом (сигнал на выводе RESET) или сигналами предустановленного уровня на выводах INT. К примеру, в микроконтроллерах AVR за характер сигналов на выводах INT0/INT1, вызывающих прерывание, определяется с помощью разрядов регистра управления MCUCR: ISC00 (разряд 0), ISC01 (разряд 1) – для входа INT0; ISC 10 (разряд 2), ISC11 (разряд 3) – для входа INT1 (табл. 3.1 и табл. 3.2).

Таблица 3.1. Выбор способа активизации прерывания по входу INT0

| Разряд ISC01 | Разряд 1SC00 | Описание |

| 0 | 0 | Прерывание вызывается по уровню лог. 0 на входе INT0 |

| 1 | 0 | Прерывание вызывается по ниспадающему фронту сигнала INT0 |

| 1 | 1 | Прерывание вызывается по нарастающему фронту сигнала INT0 |

Таблица 3.2. Выбор способа активизации прерывания по входу INT1

| Разряд ISC11 | Разряд ISC10 | Описание |

| 0 | 0 | Прерывание вызывается по уровню лог. 0 на входе INT1 |

| 1 | 0 | Прерывание вызывается по нарастающему фронту сигнала INT1 |

| 1 | 1 | Прерывание вызывается по ниспадающему фронту сигнала INT1 |

В ряде микроконтроллеров PIC выбор фронта для активизации прерывания по входу INT определяется состоянием разряда 6 регистра OPTION: лог. 1 в этом разряде соответствует прерывание по нарастающему, а лог. 0 – по ниспадающему фронту сигнала. Для установки этого разряда в языке С обычно используют специальные функции.

В микроконтроллерах AVR всем прерываниям, включая сброс, поставлен в соответствие собственный вектор прерывания – адрес в начальной области памяти программ, по которому компилятор размещает команду перехода к подпрограмме обработки прерывания. Перечень векторов прерывания в некоторых моделях микроконтроллеров AVR может выглядеть следующим образом (табл. 3.3). В микроконтроллерах AVR все прерывания имеют одинаковый приоритет, и в случае одновременного возникновения двух прерываний первым обрабатывается прерывание с меньшим номером вектора.

Таблица 3.3. Векторы прерываний

| Адрес в памяти программ | Источник прерывания | Описание |

| 0x0000 | RESET | Сигнал сброса |

| 0x0001 | INT0 | Внешний запрос на прерывание по входу INT0 |

| 0x0002 | INT1 | Внешний запрос на прерывание по входу INT1 |

| 0x0003 | Т/С1 | Захват по таймеру/счетчику Т/С1 |

| 0x0004 | Т/С1 | Совпадение с регистром сравнения А таймера Т/С1 |

| 0x0005 | Т/С1 | Совпадение с регистром сравнения В таймера Т/С1 |

| 0x0006 | Т/С1 | Переполнение таймера/счетчика Т/С1 |

| 0x0007 | Т/С0 | Переполнение таймера/счетчика Т/С0 |

| 0x0008 | SPI | Завершение передачи данных по интерфейсу SPI |

| 0x0009 | UART | Прием байта приемопередатчиком UART завершен |

| 0х000А | UART | Регистр данных приемопередатчика UART пуст |

| 0x000В | UART | Передача данных приемопередатчиком UART завершена |

| 0х000С | ANA_COMP | Прерывание от аналогового компаратора |

В микроконтроллерах PIC источники прерывания, кроме RESET, не рассматриваются в отдельности, им обычно соответствует один вектор, а в некоторых моделях – два вектора для прерываний с различной приоритетностью. Определять, какое именно прерывание требует обслуживания, – задача программиста, и многие компиляторы с языка С предоставляют для этой цели готовые функции, освобождающие от необходимости самому "вычислять" источник прерывания.

В момент возникновения прерывания в стек помещается адрес возврата – адрес команды, которая должна быть выполнена первой после выхода из подпрограммы обработки прерывания. В результате выполнения последней ассемблерной команды подпрограммы обработки прерывания (для микроконтроллеров AVR – это команда reti, а для микроконтроллеров PIC – retfie) адрес возврата извлекается из стека в счетчик команд, и выполнение программы продолжается.

Управление прерываниями в микроконтроллерах AVRВ микроконтроллерах AVR за управление прерываниями отвечают, главным образом, четыре регистра:

-GIMSK (General Interrupt Mask Register) – разрешает или запрещает внешние прерывания по входу INT0/INT1;

-GIFR (General Interrupt Flag Register) – регистр флагов внешних прерываний;

-TIMSK (Timer/Counter Interrupt Mask Register) – регистр маскирования прерываний от таймера/счетчика Т/С0 и Т/С1;

-TIFR (Timer/Counter Interrupt Flag Register) – регистр флагов прерываний от таймеров/счетчиков.

О состоянии прерывания сигнализирует соответствующий флаг, который устанавливается или сбрасывается в регистре флагов. Даже если в регистре маски прерываний установлен соответствующий отдельный разряд разрешения прерывания, то прерывания могут активизироваться только тогда, когда в регистре состояния SREG установлен разряд общего разрешения прерываний I (разряд 7). Если это имеет место, и наступает прерывание, то выполнение программы ответвляется по соответствующему адресу (см. табл. 1.4) и разряд общего разрешения прерываний I в регистре SREG сбрасывается в состояние лог. 0, блокируя тем самым последующие прерывания. Если требуется прервать подпрограмму другим прерыванием, то после входа в подпрограмму обработки прерывания программа пользователя должна установить флаг I в лог. 1.

Вместе с входом в подпрограмму обработки прерывания аппаратно сбрасывается также и соответствующий флаг, вызвавший прерывание. Некоторые флаги прерываний могут быть сброшены самим пользователем посредством установки соответствующего флага в лог. 1.

Регистр GIMSK

Регистр GIMSK (рис. 3.1), расположенный в области ввода/вывода по адресу 0x003В (адрес в SRAM – 0x005В), используется для разрешения внешних прерываний.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| INT1 | INT0 | – | – | – | – | – | – |

Рис. 3.1. Структура регистра GIMSK микроконтроллеров AVR

Если разряд INT1/INT0 установлен в лог. 1, то внешнее прерывание по входу INT1/INT0 будет разрешено до тех пор, пока установлен в лог. 1 разряд I в регистре состояния SREG.

Регистр GIFR

Состояние внешнего прерывания определяется по регистру GIFR (рис. 3.2), который расположен в области ввода/вывода по адресу 0х003А (адрес SRAM – 0х005А).+

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| INTF1 | INTF0 | – | – | – | – | – | – |

Рис. 3.2. Структура регистра GIFR микроконтроллеров AVR

Флаг INTF1/INTF0 устанавливается в лог. 1, если возникает внешнее прерывание по сигналу на выводе INT1/INT0. При входе в подпрограмму обработки прерывания этот разряд переводится аппаратно в исходное состояние лог. 0.

Регистры TIMSK и TIFR

Регистр TIMSK (рис. 3.3), расположенный в области ввода/вывода по адресу 0x0039 (адрес в SRAM – 0x0059), используется для разрешения прерываний от таймеров/счетчиков.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TOIE1 | OCIE1A | OCIE1B | – | TICIE1 | – | TOIE0 | – |

Рис. 3.3. Структура регистра TIMSK микроконтроллеров AVR

Состояние прерываний, имеющих отношение к таймерам/счетчикам микроконтроллеров AVR, определяется по регистру TIFR (рис. 3.4), который расположен в области ввода/вывода по адресу 0x0038 (адрес SRAM – 0x0058).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| TOV1 | OCF1A | OCF1B | – | ICF1 | – | TOV0 | – |

Рис. 3.4. Структура регистра TIFR микроконтроллеров AVR

Когда разряд TOIE1 и разряд I в регистре состояния SREG установлены в лог. 1, то разрешено прерывание при переполнении Т/С1. В случае переполнения в регистре TIFR устанавливается флаг TOV1.

Если разряд OCIE1A и разряд I в регистре состояния SREG установлены в лог. 1, то разрешено прерывание при совпадении содержимого регистра сравнения А с текущим состоянием Т/С1. В случае совпадения, в регистре TIFR устанавливается флаг OCF1 А.

Если разряд OCIE1B и разряд I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание при совпадении содержимого регистра сравнения В с текущим состоянием Т/С1. В случае совпадения, в регистре TIFR устанавливается флаг OCF1B.

Если разряд TICIE1 и разряд I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание при выполнении условия захвата. Когда возникает срабатывание по захвату, в регистре TIFR устанавливается флаг ICF1.

Если разряд TOIE0 и разряд I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание при переполнении таймера/счетчика Т/СО. В таком случае, в регистре TIFR устанавливается флаг TOV0.

Установка в лог. 1 одного из флагов в регистре TIFR приводит к переходу по соответствующему вектору прерывания. При входе в подпрограмму обработки прерывания, флаг в регистре TIFR аппаратно сбрасывается в лог. 0.

Управление прерываниями в микроконтроллерах PIC

В микроконтроллерах PIC управление прерываниями реализовано с помощью регистров специальных функций, и отличается от устройства к устройству. К примеру, в микроконтроллерах PIC12C6x, PIC14000, Р1С16х для этой цели используются регистры INTCON (рис. 3.5), PIE и PIR, а программы обработки прерываний всегда начинают исполняться с адреса 0x004.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| GIE | PEIE | TOIE | INTE | RBIE | TOIF | INTF | RBIF |

Рис. 3.5. Регистр INTCON микроконтроллеров PtC12C6x, PIC14000, Р1С16х

Разряд GIE – это флаг общего разрешения прерываний. Если он установлен в лог. 1, то все немаскированные прерывания разрешены, если же он сброшен в лог. 0, то все прерывания запрещены.

Разряд PEIE регистра INTCON может использоваться в качестве флага разрешения всех прерываний от периферии, определяемых с помощью регистров PIE и PIR.

Флаг TOIE разрешает (лог. 1) или запрещает (лог. 0) прерывания при переполнении таймера TMR0), а флаг TOIF определяет запрос на соответствующее прерывание.

Разряд INTE – флаг разрешения внешнего прерывания по входу INT, а разряд INTF – флаг запроса на прерывания по этому входу. Аналогичное значение, но для порта В имеют разряды RBIE и RBIF.

Регистр PIE содержит флаги разрешения прерываний от периферийных устройств, а регистр PIR – соответствующие флаги запросов на прерывание. Позиции разрядов в этих регистрах для различных микроконтроллеров отличаются.

СбросСброс – это, по сути, одна из форм прерываний, вызывающая перезапуск микроконтроллера (аппаратная инициализация всех регистров управления и периферийных устройств и выполнение программы, начиная с адреса 0x0000). Вектор сброса всегда расположен самым первым.

Возможны следующие варианты сброса:

-сброс при включении питания;

-внешний сброс – сигнал сброса подается на соответствующий вывод микроконтроллера;

-сброс от сторожевого таймера – микроконтроллер сбрасывается по истечению времени, заданного сторожевым таймером, если этот таймер был разрешен.

"Спящие" режимы процессораМикроконтроллеры AVR и PIC допускают переход в "спящий" режим, когда происходит временное отключение генератора тактовых импульсов. В таком режиме потребление энергии сведено к минимуму, а выход из него осуществляется при получении запроса на прерывание.

Переход в "спящий" режим реализуется по ассемблерной команде sleep. В случае микроконтроллеров AVR, при этом должен быть предварительно установлен в лог. 1 разряд SE (разряд 5) регистра управления MCUCR.

Когда во время режима пониженного энергопотребления происходит прерывание, центральный процессор выходит из "спящего" режима, выполняет подпрограмму обработки прерывания и продолжает выполнение программы с команды, следующей после команды sleep. Если во время режима пониженного энергопотребления поступает сигнал сброса, то центральный процессор выходит из "спящего" режима и продолжает выполнение программы с команды, расположенной по адресу $000 в области команд.

Для микроконтроллеров AVR может быть выбран один из двух "спящих" режимов:

-В ждущем режиме (Idle Mode) работа процессора приостанавливается, но таймер/счетчик, сторожевой таймер, система прерываний и тактирования остаются активными. Благодаря этому, центральный процессор может быть возвращен в обычный режим работы с помощью сторожевого таймера, таймера/счетчика или внешнего прерывания.

-В режиме пониженного энергопотребления (Power Down Mode) системный осциллятор (а значит и весь микроконтроллер) находится в отключенном состоянии. В таком режиме с помощью внутреннего RC-генератора колебаний может включаться лишь сторожевой таймер со своим собственным обеспечением тактовой частотой. Активный сторожевой таймер по истечении времени задержки опять переводит микроконтроллер в нормальное состояние. Если сторожевой таймер также отключен, то в нормальное состояние его может перевести только внешний сигнал сброса или внешнее прерывание.

Выбор одного из "спящих" режимов в микроконтроллерах AVR осуществляется с помощью разряда SM (разряд 4) регистра управления MCUCR. Если разряд SM установлен в лог. 1, то микроконтроллер переводится в режим пониженного энергопотребления последующей командой sleep, если же разряд SM сброшен в лог. 0, то последующей микроконтроллер переводится в ждущий режим в том случае, если ранее в регистре MCUCR был установлен разряд SE.

Таймеры/счетчики

Таймеры/счетчики – это, наиболее часто используемые модули микроконтроллеров. С их помощью можно измерять промежутки времени и частоту, определять ширину импульсов, вычислять скорость и т.д. Хотя они и используются для измерения времени, на самом деле речь идет об обычных двоичных счетчиках.

В микроконтроллерах AVR и PIC используются как 8-ми, так и 16-ти разрядные таймеры/счетчики. Разрядность определяет момент переполнения счетчика (возврат в нулевое состояние). Так, для 8-разрядного счетчика переполнение наступает, когда счет достигает 255, а для 16-разрядного – 65535.

Количество таймеров/счетчиков и их разрядность в микроконтроллерах отличается в зависимости от модели, и потому в данном разделе будут рассмотрены только общие вопросы, имеющие отношение к использованию таймеров/счетчиков.

Если таймер/счетчик функционирует в качестве счетчика, то он подсчитывает число импульсов, поступающих на определенный вход микроконтроллера. В этом случае соответствующий вывод должен быть сконфигурирован в инициализационной части программы как вход.

В случае использования в качестве таймера, частота тактирования таймера/счетчика является производной величиной от такта системной синхронизации внутреннего кварцевого осциллятора. При этом таймеры/счетчики используют в качестве тактового сигнала разделенный такт системной синхронизации. Коэффициент деления предварительного делителя частоты может настраиваться индивидуально для каждого из таймеров с помощью мультиплексора, управляемого разрядами из регистра управления таймера/счетчика.

Таймеры/счетчики микроконтроллеров AVRВ микроконтроллерах AVR могут использоваться следующие таймеры/счетчики:

-8-ти или 16-ти разрядный Т/С0;

-16-разрядный Т/С1;

-8-ми или 16-ти разрядный Т/С2.

Регистры управления в этом случае называются TCCR0, TCCR1 и TCCR2 (расположены в области ввода/вывода), а режим работы и коэффициент деления частоты осциллятора определяется с помощью разрядов CSx2, CSxl и CSx0 этих регистров. К примеру, для таймеров/счетчиков Т/С0 и Т/С1 выбор режима и входного такта можно определить с помощью комбинаций разрядов, представленных в табл. 4.1.

Таблица 4.1. Выбор режима и входного такта для Т/С0 и Т/С1

| CSx2 | CSx1 | CSxO | Описание |

| 0 | 0 | 0 | Останов |

| 0 | 0 | 1 | Режим "Таймер", такт = такт системной синхронизации |

| 0 | 1 | 0 | Режим "Таймер", такт = такт системной синхронизации / 8 |

| 0 | 1 | 1 | Режим "Таймер", такт = такт системной синхронизации / 64 |

| 1 | 0 | 0 | Режим "Таймер", такт = такт системной синхронизации / 256 |

| 1 | 0 | 1 | Режим "Таймер", такт = такт системной синхронизации /1024 |

| 1 | 1 | 0 | Режим "Счетчик", такт – внешний на входе Т0 (Т1), активный фронт сигнала – ниспадающий |

| 1 | 1 | 1 | Режим "Счетчик", такт – внешний на входе Т0 (Т1), активный фронт сигнала – нарастающий |

Для Т/С2 комбинации разрядов CS22, CS21 и CS20 могут иметь разное значение для различных моделей микроконтроллеров.

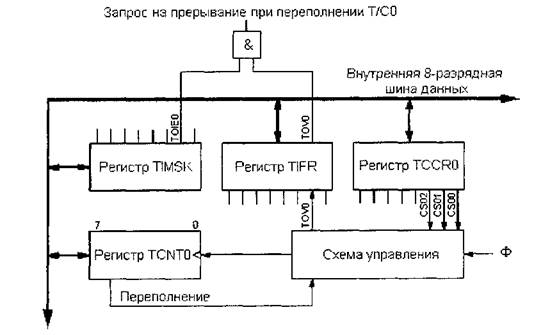

Т/С0

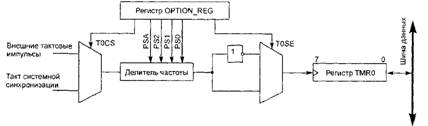

Схема работы таймера/счетчика Т/С0, представлена на рис. 4.1.

Как только с помощью разрядов CS00, CS01 и CS02 регистра TCCR0 (адрес 0x33 в области ввода/вывода, адрес 0x53 в SRAM) для делителя частоты будет установлена комбинация, отличная от 000, таймер/счетчик Т/С0 по каждому импульсу, поступающему на тактовый вход, начинает увеличивать на единицу содержимое регистра TCNT0 (адрес 0x32 в области ввода/вывода, адрес 0x52 в SRAM). Когда состояние счетчика в регистре TCNT0 изменяется с 0xFF на 0x00, в регистре TIFR (адрес 0x38 в области ввода/вывода) устанавливается флаг переполнения TOV0.

Рис. 4.1. Схема таймера/счетчика Т/С0

Кроме разрядов CS00, CS01 и CS02 регистра TCCR0 (разряды 0-2), никакие другие разряды этого регистра не используются.

Таймер/счетчик Т/С0 хорошо подходит для оценки временных интервалов. Для этого в ходе выполнения программы в регистр TCNT0 записывается исходное значение. Затем может быть запущен Т/С0 с требуемым входным тактом. Программа ожидает появления в регистре TIFR флага переполнения TOV0, указывающего на то, что требуемое время истекло.

Предположим частота системной синхронизации составляет 4 МГц, а некоторое действие должно выполняться программой каждые 0,5 с. В этом случае можно воспользоваться делением частоты на 8, что соответствует частоте тактирования 500 кГц или 2 мкс. Таким образом, на подсчет 256 тактовых импульсов счетчику потребуется 512 мкс. Это значение должно быть кратно 500 мкс, чтобы с помощью множителя 1000 в программе можно было реализовать требуемое действие в точности с периодом 500 мс. Для этого в счетчик перед началом каждого счета должно быть загружено значение 6, чтобы до переполнения выполнялся подсчет не 256, а только 250 тактовых импульсов.

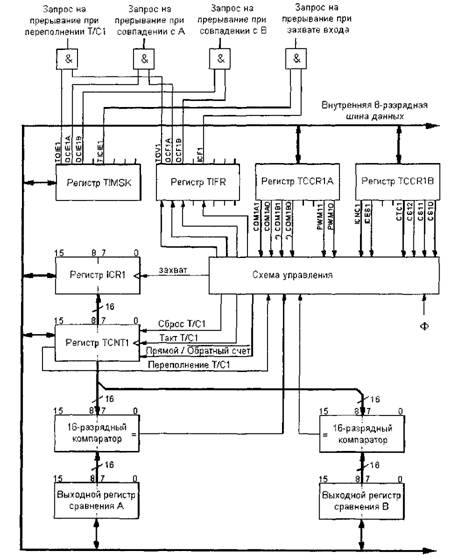

Т/С1

16-разрядный таймер/счетчик Т/С1 гораздо сложнее Т/С1 (рис. 4.2).

Рис. 4.2. Схема таймера/счетчика T/C1

В дополнение к счетному регистру и регистру управления, он содержит регистр захвата по входу (ICR1) и два 16-ти разрядных регистра сравнения на выходе (в некоторых моделях микроконтроллеров регистр сравнения В отсутствует).

Рассмотрим назначение отдельных регистров:

-TCNT1 – счетный регистр (содержимое счетчика);

-TCCR1А – регистр управления для определения реакции выводов

-ОС1А/ОС1В в случае совпадения состояния счетчика в регистре TCNT1 с регистрами сравнения OCR1A/OCR1B, а также для выбора режима широтно-импульсной модуляции;

-TCCR1B – регистр управления для настройки делителя частоты, для разрешения подачи сигнала сброса для регистра TCNT1 и для управления захватом;

-ICR1 – регистр захвата по входу (при появлении на выводе ICP фронта входного сигнала, определенного как активный, текущее состояние счетчика будет перенесено в этот регистр);

-OCR1A, OCR1B – регистры сравнения; их содержимое постоянно сравнивается с состоянием счетчика. В случае совпадения выполняются действия, определенные регистром TCCR1A.

Регистр управления TCCR1A (рис. 4.3) находится в области ввода/вывода по адресу 0x2F (адрес 0x4F в SRAM).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| COM1A1 | COM1A0 | COM1B1 | COM1B0 | – | – | PWM11 | PWM10 |

Рис. 4.3. Регистр TCCR1A таймера/счетчика T/C1

Разряды СОМ1А1/СОМ1А0 и СОМ1В1/СОМ1В0 определяют состояние вывода ОС1 А/ОС 1В при совпадении содержимого регистра сравнения А/В с содержимым счетчика. Возможные настройки для режима сравнения показаны в табл. 4.2.

Таблица 4.2. Возможные варианты для работы в режиме сравнения

| СОМ1х1 | СОМ1Х0 | Действия в случае совпадения |

| 0 | 0 | Выходное значение отсутствует |

| 0 | 1 | При совпадении ОС1х переключается в другое состояние |

| 1 | 0 | При совпадении на выходе ОС1х устанавливает лог. 0 |

| 1 | 1 | При совпадении на выходе ОС1х устанавливает лог. 1 |

В случае активизации режима ШИМ, разряды 4…7 в регистре TCCR1А имеют значения, отличные от указанных в табл. 1.6. Когда регистр управления TCCR1A определяет работу в конфигурации широтно-импульсного модулятора, то Т/С1 работает как суммирующий и вычитающий счетчик, осуществляя циклические переходы от 0x0000 к максимальному значению ТОР, и затем снова возвращаясь к 0x0000. При запрограммированной разрешающей способности ШИМ в N разрядов значение ТОР рассчитывается как:

![]()

Частота fШИМ, с которой повторяются циклы ШИМ, вычисляется по формуле:

![]()

причем частота таймера/счетчика fT/ci выбирается с помощью разрядов CSIO–CS 12 регистра TCCR1B, а разрешающая способность N – с помощью разрядов PWM10 и PWM11 регистра TCCR1A. Соответствующие взаимосвязи показаны в табл. 4.3.

Таблица 4.3. Выбор режима ШИМ (PWM11 и PWM10)

| PWM11 | PWWI10 | Разрешающая способность | Значение ТОР | Частота ШИМ |

| 0 | 0 | Режим ШИМ не активен | ||

| 0 | 1 | 8 разрядов | 0x00FF (255) | fT/С1 /510 |

| 1 | 0 | 9 разрядов | 0x01FF (511) | fT/С1 /1022 |

| 1 | 1 | 10 разрядов | 0x03FF(1023) | fT/С1 /2046 |

Когда состояние счетчика в регистре TCNT1 совпадает со значением 10 младших разрядов регистра OCR1A/OCR1B, то, в зависимости от состояния разрядов СОМ1А1/СОМ1А0 или СОМ1В1/СОМ1В0 регистра TCCR1A, вывод ОС1А/ОС1В последующим тактовым импульсом устанавливается или сбрасывается. Соответствующие взаимосвязи показаны в табл. 4.4.

Таблица 4.4. Возможности выбора для режима сравнения

| СОМ1х1 | СОМ1х0 | Действие в случае совпадения |

| 0 | 0 | На выводе ОС1х нет никакого сигнала |

| 0 | 1 | На выводе ОС1х нет никакого сигнала |

| 1 | 0 | Неинвертирующий широтно-импульсный модулятор. В случае соответствия, при суммирующем подсчете на выводе ОС1х устанавливается лог. 0, а при подсчете с вычитанием – лог. 1 |

| 1 | 1 | Инвертирующий широтно-импульсный модулятор. В случае соответствия, при суммирующем подсчете на выводе ОС1х устанавливается лог. 1, а при подсчете с вычитанием –лог. 0 |

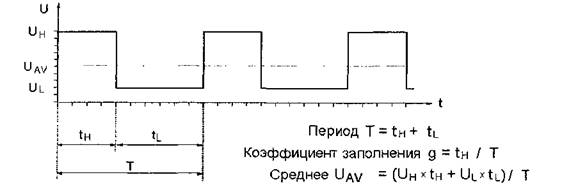

В случае неинвертирующего широтно-импульсного модулятора, коэффициент заполнения g прямоугольного сигнала на выводе с ШИМ соответствует значению n / (2N - 1), где n – значение в соответствующем регистре OCR, a N – разрешающая способность ШИМ в разрядах (рис. 4.4).

Рис. 4.4. Определение периода Т, коэффициента заполнения g и среднего арифметического UAV прямоугольных импульсов напряжения U

Если регистр сравнения OCR1A/OCR1B содержит значение ТОР или 0, то на соответствующем выводе, в соответствии с правилами, представленными в табл. 4.5, постоянно поддерживаются уровень лог. 0 или лог. 1.

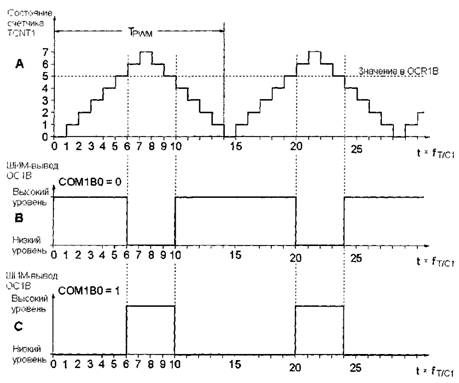

На рис. 4.5. на примере фиктивной трехразрядной ШИМ показано формирование неинвертированного и инвертированного выходного ШИМ – сигнала на выходе ОС1В. На диаграмме А показан примерный вид ступенчатого сигнала, соответствующий состоянию счетчика TCNT1, на диаграмме В – неинвертированный, а на диаграмме С – инвертированный выходной сигнал. Продолжительность периода TPWM в этом случае вычисляется в соответствии с рассмотренным выше уравнением TPWM = TT/C1 * (2N+1 - 2). Таким образом, при N=3 период ШИМ-сигнала состоит из 14 периодов тактового сигнала fT/C1 на входе TCNT1.

Таблица 4.5. Вывод ШИМ для особых случаев

| СОМ1х1 | СОМ1хО | OCR1X | Вывод ОС1х |

| 1 | 0 | 0 | 0 |

| 1 | 0 | ТОР | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | ТОР | 0 |

Рис. 4.5. Способ формирования неинвертированных и инвертированных выходных ШИМ-сигналов

В данном примере регистр сравнения OCR1B содержит значение 5. В регистре TCNT1, учитывая тот факт, что его исходное значение равно 0, значение 5 появляется после пяти тактовых импульсов. На следующем тактовом импульсе, после распознания совпадения на выводе ОС 1В устанавливается уровень лог. 0 (рис. 1.12, В).

Регистр TCNT1 инкрементируется далее до тех пор, пока не будет достигнуто значение ТОР, которое при трехразрядной ШИМ составляет 7. Как только достигнуто значение ТОР, направление счета меняется на обратное, и регистр выполняет вычитание. После девятого тактового импульса, начиная от стартового значения 0, содержимое регистра TCNT1 опять совпадает с содержимым регистра OCR1B. На следующем тактовом импульсе на выходе ОС1В устанавливается уровень лог. 1.

Регистр TCNT1 декрементируется далее до тех пор, пока опять не будет достигнуто значение 0. Это происходит после в общей сложности четырнадцати тактовых импульсов, считая от начального значения 0. Таким образом завершается период ШИМ-сигнала, направление счета вновь меняется на обратное и регистр TCNT1 опять выполняет сложение. Как видно на рис. 1.12 (В), "высокая" составляющая выходного сигнала составляет 6 тактовых периодов, а "низкая" – 4. Таким образом, коэффициент заполнения g = 6/10 или g = 3/5. Аналогично, диаграмма С на рис. 1.12 показывает соотношения для инвертированного выходного ШИМ-сигнала.

В режиме ШИМ устанавливается флаг переполнения TOV1, если счетчик при достижении состояния 0 меняет направление счета на обратное. Это прерывание по Т/С1 при переполнении, как и при нормальной работе в режиме счетчика, вызывается в том случае, если установлен флаг общего разрешения прерываний I в регистре состояния SREG, а также флаг TOIE1 в регистре TIMSK. В соответствии с этим, прерывания при совпадении регистров TCNT1 и OCR1A/OCR1B вызываются тогда, когда в регистре TIMSK установлен флаг общего разрешения прерываний и флаг OCIE1A/OCIE1B.

В отношении таймера/счетчика Т/С1 осталось рассмотреть еще регистр управления TCCR1B (адресу 0х2Е в области ввода/вывода, адрес 0х4Е в SRAM). Структура регистра TCCR1B показана на рис. 4.6.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| ICNC1 | ICES1 | – | – | CTC1 | CS12 | CS11 | CS10 |

Рис. 4.6. Регистр TCCR1В таймера/счетчика Т/С1

Разряды 0 – 2 используются для выбора частоты тактирования Т/С1 (табл. 1.5). Если разряд СТС1 установлен в лог. 1, то Т/С1 возвращается в состояние 0x0000 по импульсу такта системной синхронизации, следующего после совпадения содержимого счетчика и регистра сравнения А. При работе в режиме ШИМ этот разряд на процесс работы никак не влияет.

Разряд ICES1 определяет, каким образом должна осуществляться передача состояния счетчика в регистр захвата ICR1: по нарастающему (ICES 1 = 1) или по ниспадающему фронту (ICES 1=0).

Разряд ICNC1 определяет, должно ли быть активизировано подавление помех (если ICNC1 = 0, то подавление помех отключено), Для подавления кратковременных импульсов помех, которые могут привести к ошибочному запуску, входной сигнал зондируется на протяжении четырех периодов такта системной синхронизации. Только после того как будут распознаны четыре последовательных низких или высоких уровня входного сигнала, что определяется разрядом ICES1, при активном подавлении помех будет выполнена запись текущего состояния счетчика в регистр ICR1.

Т/С2

Таймер/счетчик Т/С2 обычно имеет разрядность 8 бит и реализует функции сравнения на выходе и ШИМ, аналогичные Т/С1. Основная особенность Т/С2 заключается в том, что в качестве источника тактовых импульсов он может использовать генератор, независимый от системного. Для управления Т/С2 используются два регистра: ASSR (рис. 4.7) и TCCR2 (рис. 4.8).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| – | – | – | – | AS2 | TCN2UB | OCR2UB | TCR2UB |

Рис. 4.7. Регистр ASSR таймера/счетчика Т/С2

Если установить в лог. 1 разряд AS2, то в качестве источника тактовых импульсов можно использовать внешний осциллятор. Оставшиеся три разряда (0-2) используются в программах для проверки того, что данные не записываются в регистры Т/С2 в тот момент, когда они обновляются аппаратно. Такая проверка необходима по той причине, что осциллятор Т/С2 работает асинхронно по отношению к системному осциллятору.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| – | PWM2 | COM21 | COM20 | CTC2 | CS22 | CS21 | CS20 |

Рис. 4.8. Регистр TCCR2 таймера/счетчика Т/С2

Установка в лог. 1 разряда PWM2 переводит Т/С2 в режим ШИМ. Назначение разрядов COM21 и СОМ20 идентично назначению разрядов COM lxl и СОМ 1x0 таймера/счетчика Т/С1 – выбор режима сравнения на выходе.

Разряд СТС2 определяет, должен ли счетчик сбрасываться в нуль при совпадении его содержимого с регистром сравнения. Разряды 0 – 2 определяют частоту тактового сигнала, полученного с помощью предварительного делителя частоты такта системной синхронизации.

Таймеры/счетчики микроконтроллеров PICОписанное выше применение таймеров/счетчиков микроконтроллеров AVR справедливо также и для таймеров микроконтроллеров PIC. Здесь используются аналогичные принципы измерения ширины и частоты импульсов, а также широтно-импульсной модуляции, режимов сравнения и захвата.

В микроконтроллерах PIC могут использоваться три таймера: TMR0, TMR1 и TMR2.

TMR0

TMR0 (рис. 4.9) – это 8-разрядный таймер/счетчик. Таким образом, счет для него ограничен диапазоном 0-255. Его тактирование реализуется от внешнего источника или на основании такта системной синхронизации.

Рис. 4.9. Схема таймера/счетчика TMR0

Для управления работой таймера TMR0 используются следующие разряды регистра OPTION_REG:

-разряд 5 – T0CS – определяет выбор источника синхроимпульсов (0 – внутренний; 1 – внешний на входе TOCKI);

-разряд 4 – T0SE – определяет выбор фронта, по которому происходит увеличение содержимого счетного регистра TMR0 (0 – по нарастающему; 1 – по ниспадающему фронту тактового сигнала);

-разряд 3 – PSA – использование предварительного делителя частоты (0 – делитель используется для управления таймером TMR0; 1 – для управления сторожевым таймером);

-разряды 0-2 – PS0, PS1, PS2 – выбор коэффициента деления частоты входного тактового сигнала (табл. 4.6).

Таблица 4.6. Назначение разрядов PSO - PS2 регистра OPTIONJREG

| PS2 | PS1 | PSO | Коэффициент деления частоты входного тактового сигнала |

| 0 | 0 | 0 | 2 |

| 0 | 0 | 1 | 4 |

| 0 | 1 | 0 | 8 |

| 0 | 1 | 1 | 16 |

| 1 | 0 | 0 | 32 |

| 1 | 0 | 1 | 64 |

| 1 | 1 | 0 | 128 |

| 1 | 1 | 1 | 256 |

Для управления прерываниями от таймера TMR0 используются следующие разряды регистра INTCON:

-разряд 2 – TOIF – флаг прерывания при переполнении TMR0;

-разряд 5 – TOIE – флаг разрешения прерывания при переполнении TMR0;

-разряд 7 – GIE – флаг общего разрешения прерываний.

TMR1

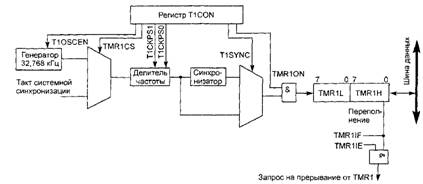

TMR1 (рис. 4.11) – это 16-разрядный таймер/счетчик, который может использоваться для формирования запросов на прерывание, подобно TMR0, или же работать в режимах захвата, сравнения и ШИМ.

Тактирование таймера TMR1 осуществляется от сигнала системной синхронизации или от специального генератора, предназначенного для работы с относительно медленными программными приложениями. Как правило, используется кварцевый резонатор частотой 32,768 кГц.

Для управления таймером TMR1 используется регистр T1CON (рис. 4.12). Назначение отдельных разрядов регистра T1CON:

-TMRION – подключение таймера (0 – отключен, 1 – включен);

-TMR1CS – выбор источника тактирующих сигналов (0 – такт системной синхронизации; 1 – генератор 32,768 кГц);

-Tl SYNC – включение/отключение синхронизация специального генератора с генератором импульсов системной синхронизации (0 – включена; 1 – отключена);

-T10SCEN – разрешение/запрет тактирования таймера TMR1 от специального генератора (0 – генератор отключен; 1 – тактирование разрешено);

T1CKPS0, T1CKPS1 – выбор коэффициента деления частоты (табл. 4.7).

Рис. 4.11. Схема таймера/счетчика TMR1

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| – | – | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | TMR1CS | TMR1ON |

Рис. 4.12. Регистр T1CON микроконтроллеров PIC

Таблица 4.7. Назначение разрядов T1CKPS0 - T1CKPS1 регистра T1CON

| T1CKPS1 | T1CKPS0 | Коэффициент деления частоты тактового сигнала |

| 0 | 0 | 1 |

| 0 | 1 | 2 |

| 1 | 0 | 4 |

| 1 | 1 | 8 |

Счетный регистр таймера TMR1 представляет собой регистровую пару TMR1H, TMR1L, а управление прерываниями осуществляется с помощью разрядов регистров PIR1 и РIЕ1:

Регистр PIR1:

-разряд 0 – TMR1IF – флаг переполнения TMR1;

-разряд 2 – ССР 1 IF – флаг прерывания при возникновении захвата по входу/

Регистр PIE1:

-разряд 0 – TMR1IE – флаг разрешения прерывания при переполнении TMR1;

-разряд 2 – ССР НЕ – флаг разрешения прерывания при возникновении захвата по" входу.

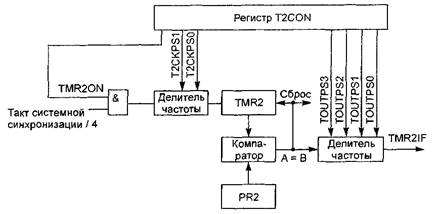

TMR2

Назначение таймера TMR2 (рис. 4.13) – измерение временных интервалов для реализации ШИМ, обеспечения определенной скорости обмена по последовательному порту и т.п. В этом смысле он подобен таймеру TMR0.

Таймер TMR2 тактируется импульсами, следующими с частотой такта системной синхронизации, деленной на четыре. Каждый раз, когда содержимое счетного регистра TMR2 совпадает с содержимым регистра PR2, таймер автоматически сбрасывается в исходное (нулевое) состояние.

Рис. 4.13. Схема таймера/счетчика TMR2

При каждом совпадении TMR2 и PR2 генерируется запрос на прерывание, частоту возникновения которого можно также масштабировать с помощью выходного делителя частоты.

Для управления таймером TMR2 используется регистр T2CON (рис. 4.14).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| – | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

Рис. 4.14. Регистр T2CON микроконтроллеров PIC

Назначение отдельных разрядов регистра T2CON:

-T2CKPS0-T2CKPS1 –управление предварительным делителем частоты (табл. 4.8);

-TMR20N – подключение таймера (0 – отключен, 1 – включен);

-TOUTPS0-TOUTPS3 – выбор коэффициента деления частоты запросов на прерывание при TMR2::=:PR2 (табл. 4.9).

Таблица 4.8. Назначение разрядов T2CKPS0 - T2CKPS1 регистра T2CON

| T1CKPS1 | T1CKPS0 | Коэффициент деления частоты тактового сигнала |

| 0 | 0 | 1 |

| 0 | 1 | 4 |

| 1 | X | 16 |

Таблица 4.9. Назначение разрядов TOUTPS0 - TOUTPS3 регистра T2CON

| TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | Коэффициент деления частоты запросов |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 2 |

| 0 | 0 | 1 | 0 | 3 |

| 0 | 0 | 1 | 1 | 4 |

| 0 | 1 | 0 | 0 | 5 |

| о | 1 | 0 | 1 | 6 |

| 0 | 1 | 1 | 0 | 7 |

| 0 | 1 | 1 | 1 | 8 |

| 0 | 0 | 0 | 9 | |

| 0 | 0 | 1 | 10 | |

| 0 | 1 | 0 | 11 | |

| 0 | 1 | 1 | 12 | |

| 1 | 0 | 0 | 13 | |

| 1 | 0 | 1 | 14 | |

| 1 | 1 | 0 | 15 | |

| 1 | 1 | 1 | 16 |

Для организации прерываний используются разряды TMR2JE (флаг разрешения) и TMR2IF (флаг прерывания) регистров PIE1 и PIR1 соответственно.

Для того чтобы эффективно использовать таймер TMR2, используются следующие формулы:

где Т – требуемая временная задержка, К1 – коэффициент деления предварительного делителя частоты; К2 – коэффициент деления делителя частоты запросов на прерывание; PR2 – содержимое регистра PR2; F – частота системной синхронизации.

Модуль ССРТаймеры TMR1 и TMR2 микроконтроллеров PIC применяются в составе модуля сравнения/захвата/ШИМ – ССР (Compare-Capture-PWM). Таких модулей может быть два: ССР1 и ССР2, – управление которыми реализовано с помощью регистров CCPxCON (рис. 4.15),

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| – | – | DC1BX1 | DC1BX0 | CCP1M3 | CCP1M2 | CCP1M1 | CCP1M0 |

Рис. 4.15. Регистр CCPxCON микроконтроллеров PIC

Назначение отдельных разрядов регистра CCPxCON:

ССР1М0 – ССР1МЗ – выбор режима захвата/сравнения (табл. 4.9) DC1ВХ0 – DC1ВХ1 – два младших разряда 10-разрядной ШИМ.

Таблица 4.9. Назначение разрядов ССР1М1 -ССР1МЗ регистра CCPxCON

| ССР1МЗ | ССР1М2 | ССР1М1 | ССР1М0 | Значение |

| 0 | 0 | X | X | Модуль ССР отключен |

| 0 | 1 | 0 | 0 | Захват по каждому ниспадающему фронту |

| 0 | 1 | 0 | 1 | Захват по каждому нарастающему фронту |

| 0 | 1 | 1 | 0 | Захват по каждому 4-му нарастающему фронту |

| 0 | 1 | 1 | 1 | Захват по каждому 16-му нарастающему фронту |

| 1 | 0 | 0 | 0 | В случае совпадения на выходе – высокий уровень |

| 1 | 0 | 0 | 1 | В случае совпадения на выходе – низкий уровень |

| 1 | 0 | 1 | 0 | В случае совпадения – запрос на прерывание |

| 1 | 0 | 1 | 1 | Особый случай режима сравнения |

| 1 | 1 | X | X | Режим ШИМ |

В режиме захвата (то есть, фиксации значения таймера в момент появления определенного условия) используются регистры CCPR1H, CCPR1L (в случае TMR1) или CCPR2H, CCPRL (в случае TMR2). В таком режиме таймер выполняет функции счетчика тактовых импульсов, и при наступлении условия захвата его содержимое переписывается в регистровую пару CCPRx.

В режиме сравнения модуль ССР формирует сигнал на выходе ССРх в том случае, когда содержимое счетного регистра становится равным значению, записанному в регистровой паре CCPRxL, CCPRxH. Этот режим обычно используется для выдачи сигналов на внешние устройства по истечении некоторого временного интервала.

В режиме ШИМ таймер работает как делитель частоты, формирующий период ШИМ-сигнала. Его значение постоянно сравнивается с содержимым регистра PR2, и при совпадении компаратор сбрасывает таймер в исходное состояние, после чего цикл повторяется. Параллельно организован контур сравнения, включающий в себя таймер, второй компаратор и регистр CCPRxH. Выходы обоих компараторов управляют RS-триггером, выход которого соединен с выводом ССРх.

Вначале триггер устанавливается в "1" по сигналу сброса таймера, а по сигналу компаратора контура сравнения – сбрасывается в "О". Таким образом, на выходе RS-триггера формируется сигнал с периодом, определяемым содержимым регистров PR2 и CCPRxH.

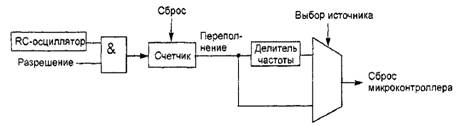

Сторожевой таймер

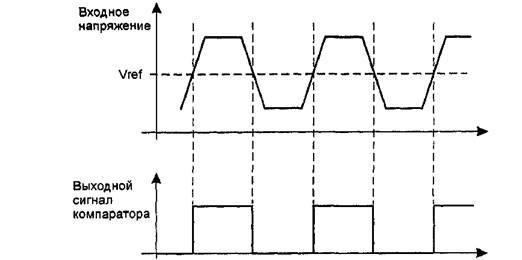

Сторожевой таймер (watchdog timer) – встроенный таймер, тактируемый внутренним RC-осциллятором, который автоматически сбрасывает микроконтроллер при переполнении своего счетного регистра. В частности, он используется для предотвращения перехода микроконтроллера в режим бесконечного цикла, когда на него невозможно повлиять извне. Обобщенная структурная схема сторожевого таймера показана на рис. 5.1.

В микроконтроллерах AVR и PIC управление сторожевым таймером несколько отличается. Так, в микроконтроллерах AVR для этого используется регистр управления WDTCR (адрес в области ввода/вывода – 0x21, адрес SRAM – 0x41) (рис. 5.2).

Рис. 5.1. Структурная схема сторожевого таймера

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| – | – | – | WDTOE | WDE | WDP2 | WDP1 | WDP0 |

Рис. 5.2. Регистр WDTCR микроконтроллеров AVR

Назначение отдельных разрядов регистра WDTCR:

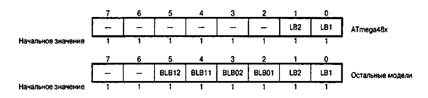

-WDP0-WDP2 – выбор коэффициента деления частоты следования сигналов сброса (при этом период до наступления сброса зависит от рабочего напряжения процессора – табл. 5.1);

-WDE – включение/отключение сторожевого таймера (1 – включен);

-WDTOE – если сторожевой таймер должен быть отключен, следует установить этот разряд в лог. 1. После установки этого разряда он в течение четырех периодов такта системной синхронизации остается в состоянии лог. 1, а затем аппаратно сбрасывается в лог. 0. Программа пользователя имеет возможность отключить сторожевой таймер посредством записи лог. 0 в разряд WDE только во время этих четырех тактов системной синхронизации.

Таблица 5.1 Назначение разрядов WDP0 - WDP2 регистра WDTCR

| WDP2 | WDP1 | WDPP | Коэффициент деления | Период до сброса (при Vcc в 5 В) | Период до сброса (при Vcc = 3 В) |

| 0 | 0 | 0 | 1 | 16 мс | 47 мс |

| 0 | 0 | 1 | 2 | 32 мс | 94 мс |

| 0 | 1 | 0 | 4 | 64 мс | 190 мс |

| 0 | 1 | 1 | 8 | 128 мс | 380 мс |

| 1 | 0 | 0 | 16 | 256 мс | 750 мс |

| 1 | 0 | 1 | 32 | 512 мс | 1,5с |

| 1 | 1 | 0 | 64 | 1 с | Зс |

| 1 | 1 | 1 | 128 | 2,1 с | 6с |

В системе команд AVR сторожевой таймер сбрасывается в исходное состояние по команде wdr. В микроконтроллерах PIC для управления сторожевым таймером предназначен рассмотренный выше регистр OPTION. Для этого разряд PSA должен быть установлен в лог. 1, чтобы предварительный делитель частоты был переключен на использование совместно со сторожевым таймером, а не с TMR0. Коэффициент деления выбирается с помощью разрядов PS2-PS0 (табл. 5.2). В отличие от микроконтроллеров AVR, в микроконтроллерах PIC отсутствует возможность включать/отключать сторожевой таймер с помощью регистра управления. Единственный способ предотвратить сброс от сторожевого таймера – периодически выполнять ассемблерную команду clrwdt.

Таблица 5.2. Выбор коэффициента деления частоты следования сигналов сброса от сторожевого таймера в микроконтроллерах PIC

| PS2 | PS1 | PS0 | Коэффициент деления | Период до сброса |

| 0 | 0 | 0 | 1 | 18 мс |

| 0 | 0 | 1 | 2 | 36 мс |

| 0 | 1 | 0 | 4 | 72 мс |

| 0 | 1 | 1 | 8 | 144 мс |

| 1 | 0 | 0 | 16 | 288 мс |

| 1 | 0 | 1 | 32 | 576 мс |

| 1 | 1 | 0 | 64 | 1,2 с |

| 1 | 1 | 1 | 128 | 2,3 с |

Параллельные порты – это особые устройства ввода/вывода, позволяющие передавать во внешний мир или принимать одновременно восемь разрядов данных. Для обозначения портов используются латинские буквы А, В, С и т.д. Количество портов ввода/вывода варьируется в зависимости от модели микроконтроллера.

В микроконтроллерах AVR каждому параллельному порту ввода/вывода поставлены в соответствие три регистра (букве х соответствует имя порта А, В и т.д.):

-DDRx – регистр направления передачи данных – определяет, является тот или иной вывод порта входом или выходом; если некоторый разряд регистра DDRx содержит лог. 0, то соответствующий вывод порта сконфигурирован как вход, в противном случае – как выход;

-PORTx – регистр порта – если вывод выполняет роль выхода, то в соответствующий разряд записывается значение, предназначенное для вывода; если вывод выполняет роль входа, то лог. 0 в некотором разряде регистра PORTx соответствует высокоомный вход, а лог. 1 – вход, нагруженный подтягивающим сопротивлением;

-PINx – регистр выводов порта – в отличие от регистров DDRx и PORTx доступен только для чтения и позволяет считать входные данные порта на внутреннюю шину микроконтроллера.

Выводы портов зачастую выполняют различные альтернативные функции при работе с внутренними и периферийными модулями микроконтроллеров AVR. Так, к примеру, в некоторых моделях в качестве внешних тактовых входов таймеров/счетчиков Т/С0 и Т/С1 используются разряды 0 и 1 порта В или 4 и 5 порта D. Точное назначение выводов портов следует сверять по спецификации микроконтроллера.

В микроконтроллерах PIC каждому параллельному порту ввода/вывода поставлены в соответствие два регистра:

-PORTx – регистр данных порта;

-TRISx – регистр направления передачи данных через выводы порта (лог. 1 в некотором разряде этого регистра соответствует режим ввода, а лог. 0 – режим вывода).

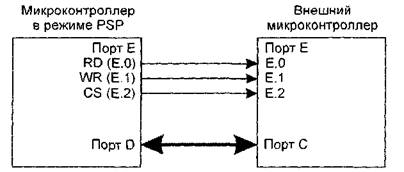

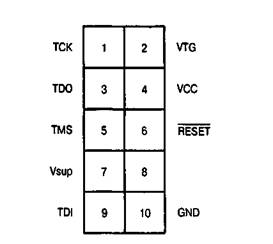

В микроконтроллерах PIC серии 18Сх порт D может работать в режиме управляемого параллельного порта PSP (Parallel Slave Port). Это означает, что он действует как регистр, который может быть подключен к шине другого микроконтроллера, обмениваясь с ним данными. В режиме PSP, как и в случае обмена данными с любым периферийным устройством, используются сигналы RD (чтение), WR (запись) и CS (выбор кристалла) – разряды 0-2 порта Е (пример – рис. 6.1).

Рис. 6.1. Пример подключения внешнего микроконтроллера PIC в режиме PSP

Для управления режимом PSP используется регистр TRISE (рис. 6.2).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| IBF | OBF | IBOV | PSPMODE | – | TRISE2 | TRISE1 | TRISE0 |

Рис. 6.2. Регистр TRISE микроконтроллеров PIC

Режим PSP активизируется путем установки в лог. 1 разряда PSPMODE. Прерывания разрешаются установкой в лог. 1 разряда PSPIE (разряд 7) регистра PIE1, а запросы формируются в разряде PSPIF (разряд 7) регистра PIR1. С помощью разрядов 0-2 регистра TRISE осуществляется выбор режима для соответствующих разрядов порта Е.

Когда на линиях CS и RD (выводы RE2 и RE0) одновременно появляется низкий уровень сигнала, содержимое регистра OUTREG выводится через порт D. При записи в регистр OUTREG устанавливается в лог, 1 разряд OBF регистра TRISE – это означает, что выходной буфер заполнен данными. После передачи данных разряд OBF автоматически сбрасывается в лог. 0.

Когда на линиях CS и WR (выводы RE2 и RE1) одновременно появляется низкий уровень сигнала, осуществляется прием данных через порт D. Принятая величина сохраняется в регистре INREG, при этом автоматически устанавливается в лог. 1 разряд IBF регистра TRISE. После программного считывания содержимого регистра INREG этот разряд автоматически сбрасывается в лог. 0.

Если ранее принятый байт не считывается до поступления следующего байта в регистр INREG, устанавливается в лог. 1 разряд IBOV регистра TRISE, указывающий на переполнение входного буфера.

Последовательный ввод/вывод

В отличие от параллельного обмена данными, в случае последовательного ввода/вывода используется только одна информационная линия. При этом передача данных бывает асинхронной и синхронной.

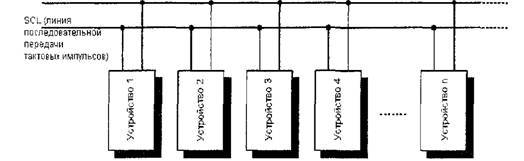

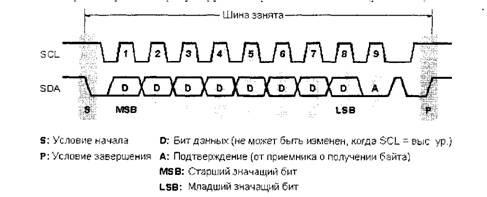

При синхронном последовательном вводе/выводе синхронизируется передача отдельных битов данных с помощью одновременно передаваемого тактового сигнала. Синхронная последовательная передача данных применяется, на уровне печатных плат, в том числе – для обмена данными между различными интегрированными блоками в составе схемы микроконтроллера и различными периферийными схемами (например, для обработки видеосигнала).

В противоположность этому, при асинхронной передаче данных передается не тактовый сигнал, а старт-бит и стоп-бит, определяющие начало и завершение передачи слова данных (рис. 7.1).

Рис. 7.1. Типичный формат асинхронной передачи данных (в данном примере – байта 10000010)

Главной областью применения асинхронной передачи данных, является не обмен данными в составе схемы, а коммуникация между блоками, разделенными пространственно и обладающими признаками собственного интеллекта. В качестве примера можно назвать связь между персональным компьютером и принтером, модемом, программирующим устройством или регистратором данных.

В микроконтроллерах AVR асинхронная передача данных осуществляется с помощью приемопередатчика UART, а в микроконтроллерах PIC – приемопередатчика USART или по шине CAN. Для синхронного ввода/вывода используется особый режим приемопередатчика USART, а также интерфейсы SPI и I2С (в микроконтроллерах PIC – с помощью порта MSSP).

Приемопередатчик UART микроконтроллеров AVRДля работы UART выделены в общей сложности четыре регистра:

-регистр управления UCR (адрес в области ввода/вывода – 0х0А, адрес SRAM – 0х2А) – предназначен для управления функциями приемопередатчика и для разрешения/запрета прерываний от UART (рис. 7.2);

-регистр состояния USR (адрес в области ввода/вывода – 0x0В, адрес SRAM –0x2В) (рис. 7.3);

-регистр данных UDR (адрес в области ввода/вывода – 0х0С, адрес SRAM – 0x2С) – физически состоит из двух регистров, обращение к которым осуществляется по одному и тому же адресу; один из них используется для передачи, а другой – для приема данных;

-регистр UBRR (адрес в области ввода/вывода – 0x09, адрес SRAM – 0x29) – применяется для настройки требуемой скорости передачи данных с помощью встроенного контроллера, позволяющего устанавливать наиболее распространенные скорости передачи по стандарту RS232C.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RXCIE | TXCIE | UDRIE | RXEN | TXEN | CHR9 | RXB8 | TXB8 |

Рис. 7.2. Регистр управления UCR микроконтроллеров AVR

Если разряд RXCIE и разряд общего разрешения прерываний I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание по завершению приема через UART.

Если разряд TXCIE и разряд общего разрешения прерываний I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание по завершению передачи через UART.

Если разряд UDRIE и разряд общего разрешения прерываний I в регистре состояния SREG установлены в лог. 1, то разрешается прерывание по опустошению регистра данных UART.

Если разряд RXEN установлен в лог. 1, то происходит разблокирование приемника, и вывод 0 порта D становится входом UART. Если разряд RXEN содержит лог. 0, то принимающий элемент приемопередатчика UART блокируется, и вывод 0 порта D может использоваться в качестве обычного входа/выхода. Если разряд RXEN содержит лог. 0, то флаги OR и FE регистра состояния USR не могут быть установлены. Если эти флаги все же установлены, то они с помощью RXEN не сбрасываются.

Если разряд TXEN установлен в лог. 1, то происходит разблокирование передатчика, а вывод 1 порта D становится выходом UART. Если разряд TXEN содержит лог. 0, то передающий элемент UART блокируется, и вывод 1 порта D может использоваться в качестве обычного входа/выхода. Если разряд TXEN во время процесса передачи устанавливается в лог. 0, то передатчик не блокируется до тех пор, пока текущий символ в сдвиговом регистре, а также символ, возможно, ожидающий на передачу в регистре UDR не будут полностью переданы.

Если разряд CHR9 установлен в лог. 1, то слова данных, подлежащие передаче/считыванию имеют длину 11 бит (9 разрядов данных плюс стартовый и стоп-бит). Девятый бит из разряда ТХВ8 при передаче попадает в UCR, а при приеме – в разряд RXB8 регистра UCR. Девятый бит может быть использован для размещения дополнительных информационных данных, например, в качестве бита четности или второго стоп-бита. Если разряд CHR9 установлен в лог. 0, то слова данных, подлежащие передаче/считыванию имеют длину 10 бит (8 разрядов данных плюс стартовый и стоп-бит).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RXC | TXC | UDRE | FE | OR | – | – | – |

Рис. 7.3. Регистр состояния USR микроконтроллеров AVR

Регистр состояния USR информирует программу пользователя о состоянии приемопередатчика UART.

Флаг RXC устанавливается в лог. 1, если принятое слово данных было перенесено из сдвигового регистра в регистр UDR (без учета возможных ошибок кадрирования, которые могли возникнуть во время передачи данных). После чтения регистра UDR флаг RXC автоматически сбрасывается в лог. 0.

Флаг ТХС будет установлен в лог. 1, если символ в сдвиговом регистре был передан полностью (то есть, включая стоп-бит), и из регистра UDR не ожидается новый байт данных. Флаг очень полезен в полудуплексном режиме работы, когда непосредственно после передачи необходимо переключиться в режим приема. При входе в подпрограмму обработки прерывания флаг завершения передачи ТХС аппаратно сбрасывается в лог. 0.

Флаг UDRE устанавливается в лог. 1, если содержимое регистра UDR было перенесено в сдвиговой регистр. С его помощью пользователь получает уведомление о том, что приемопередатчик готов к передаче нового байта.

Соответствующая подпрограмма обработки прерывания выполняется до тех пор, пока установлен флаг UDRE. Флаг UDRE сбрасывается при записи байта данных в регистр UDR. В случае сброса при включении питания флаг UDRE устанавливается в лог. 1, чтобы показать, что приемопередатчик готов к передаче нового байта данных.

Флаг FE устанавливается в лог. 1 при обнаружении ошибки кадрирования. Это происходит, если при трех сканированиях стоп-бита был более одного раза обнаружен лог. 0, и тем самым стоп-бит был распознан как сигнал низкого уровня. Флаг FE сбрасывается, когда стоп-биту соответствует сигнал высокого уровня. Пользовательская программа должна постоянно проверять флаг FE перед чтением регистра UDR, чтобы можно было распознать потенциально некорректный символ в регистре приема.

Флаг OR устанавливается в лог. 1, если один из символов, переданных в регистр UDR из сдвигового регистра, не был прочитан перед следующим поступившим символом. Этот флаг обновляется после считывания действительного символа из регистра UDR, поэтому пользовательская программа должна всегда проверять флаг OR после чтения регистра UDR, чтобы распознать потерю одного поступившего символа. Флаг OR сбрасывается при переносе считанного символа в регистр UDR.

Настройка скорости передачи данных через UARTВ приемопередатчик UART встроен специальный контроллер скорости передачи данных, представляющий собой делитель частоты для определения скорости передачи данных на основании такта системной синхронизации.

Скорость передачи может быть вычислена по следующему уравнению:

![]()

где fBaud – скорость передачи в бодах, Ф – такт системной синхронизации; UBRR – содержимое 8-разрядного регистра UBRR (0...255).

Значения, записываемые в регистр UBRR для наиболее распространенных скоростей передачи данных, представлены в табл. 7.1.

Таблица 7.1. Значения регистра UBRR для наиболее распространенных скоростей передачи данных и частоты работы кварцевого осциллятора

| Скорость передачи данных, бод | 1,8432 МГц | Погрешность (%) | 3,6864 МГц | Погрешность (%) | 4 МГц | Погреш ность (%) |

| 1200 | UBRR = 95 | 0,0 | UBRR = 191 | 0,0 | UBRR = 207 | 0,2 |

| 2400 | UBRR = 47 | 0,0 | UBRR = 95 | 0,0 | UBRR = 103 | 0,2 |

| 4800 | UBRR = 23 | 0,0 | UBRR = 47 | 0,0 | UBRR = 51 | 0,2 |

| 9600 | UBRR = 11 | 0,0 | UBRR = 23 | 0,0 | UBRR = 25 | 0,2 |

| 14400 | UBRR=7 | 0,0 | UBRR=15 | 0,0 | UBRR = 16 | 2,1 |

| 19200 | UBRR=5 | 0,0 | UBRR = 11 | 0,0 | UBRR=12 | 0,2 |

| 2400 | UBRR = 207 | 0,2 | UBRR = 287 | – | UBRR = 312 | – |

| 4800 | UBRR = 103 | 0,2 | UBRR = 143 | 0,0 | UBRR = 155 | 0,2 |

| 9600 | UBRR = 51 | 0,2 | UBRR = 71 | 0,0 | UBRR = 77 | 0,2 |

| 14400 | UBRR = 34 | 0,8 | UBRR = 47 | 0,0 | UBRR = 51 | 0,2 |

| 19200 | UBRR = 25 | 0,2 | UBRR = 35 | 0,0 | UBRR = 38 | 0,2 |

Значения, выделенные курсивом, превышают 255, и потому не могут быть установлены в регистре UBRR, имеющем длину всего 8 разрядов. Если потребуется соответствующая скорость передачи данных, то необходимо переходить на более низкие частоты колебаний кварцевого осциллятора.

Приемопередатчик USART микроконтроллеров PICВ микроконтроллерах PIC скорость обмена данными через приемопередатчик USART задается восьмиразрядным счетчиком во взаимодействии с регистром SPBRG. Когда содержимое счетчика и регистра SPBRG совпадает, счетчик сбрасывается в нуль. На значение скорости передачи через USART также влияет состояние разряда BRGH регистра управления TXSTA (рис. 1.32). Этот разряд определяет, какая требуется скорость для передачи данных: высокая (BRGH = 1) или низкая (BRGH = 0).

Значение для записи в регистр SPBRG вычисляется по следующей формуле:

SPBRG = (FOSC * 4BRGH) / (64 * скорость передачи) - 1.

Например, для того чтобы получить скорость передачи 9600 бод при микроконтроллере с рабочей частотой FOSC = 10 МГц в регистр SPBRG должно быть записано значение (10 * 106 * 4)/(64 * 9600) – 1 = 64,1 (округляем до 64).

Управление приемопередатчиком USART осуществляется с помощью регистров TXSTA, который используется для управления процессом передачи (рис. 7.4), и RCSTA, который используется для управления процессом приема (рис. 7.5).

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| CSRC | TX9 | TXEN | SYNC | – | BRGH | TRMT | TX9D |

Рис. 7.4. Регистр TXSTA микроконтроллеров PIC

В отличие от приемопередатчика UART микроконтроллеров AVR, устройство USART может обмениваться данными не только в асинхронном, но и в синхронном режиме. В этом случае поразрядный сдвиг данных из сдвигового регистра в линию передачи (или наоборот) осуществляется по синхроимпульсам самого приемопередатчика USART или внешнего устройства. Выбор режима работы USART осуществляется с помощью разряда SYNC регистра TXSTA (1 – синхронный режим; 0 – асинхронный режим), а выбор источника тактовых импульсов в синхронном режиме – с помощью разряда CSRC (1 – внутренний источник; 0 – внешний источник).

Назначение остальных разрядов регистра TXSTA:

-TX9D – девятый бит передаваемых данных, если ТХ9 = 1;

-TRMT – флаг, сигнализирующий о завершении передачи байта;

-TXEN – флаг разрешения передачи данных;

-ТХ9 – разрешение (лог. 1) передачи данных в девятиразрядном формате.

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SREN | RX9 | SREN | CREN | ADDEN | FERR | OERR | RX9D |

Рис. 7.5. Регистр RCSTA микроконтроллеров PIC

Назначение разрядов регистра RCSTA:

-RX9D – девятый бит принимаемых данных, если RX9 = 1;

-OERR – флаг, указывающий на переполнение буфера приема;

-FERR – флаг, указывающий на обнаружение ошибки в формате принимаемых данных;

-ADDEN – разрешение обнаружения адреса в асинхронном режиме передачи девяти бит данных– в некоторых микроконтроллерах PIC приемник USART может использоваться для приема сразу двух байтов в формате "данные:адрес", где адрес предназначен для идентификации устройства, связанного с шиной данных (в таком случае подпрограмма обработки прерывания вначале проверит адрес запрошенного устройства и только потом обработает байт данных);

-CREN – разрешение режима непрерывного приема;

-SREN – флаг разрешения однократного приема в синхронном режиме (после приема данных автоматически сбрасывается в лог. 0);

-RX9 – флаг разрешения приема девяти бит данных;

-SREN – флаг активизации USART (для передачи битов данных используется вывод 6 порта С, а для приема – вывод 7 того же порта).

Флаги запросов (TXIF и RCIF) и разрешения (TXIE и RCIE) прерываний от USART находятся в регистрах PIR и PIE.

Синхронная передача данных по интерфейсу SPIИнтерфейс SPI (Serial Peripheral Interface) служит для обмена данными с периферийными устройствами. В качестве таких устройств могут выступать простые сдвиговые регистры или буквенно-цифровые модули индикации, а также сложные микропроцессорные системы или системы регистрации данных. Многие компании-изготовители предлагают большой выбор устройств с интерфейсом SPI.

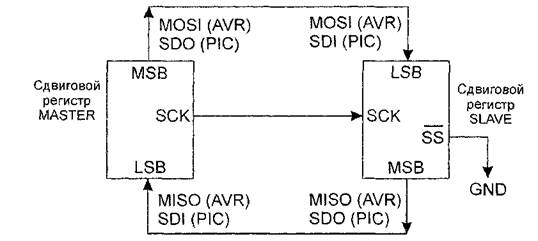

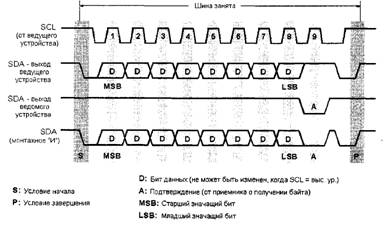

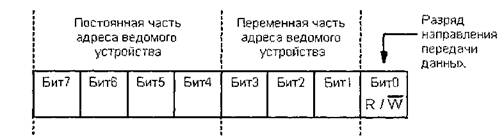

В случае обмена данными по интерфейсу SPI микроконтроллер работает в режиме ведущего устройства (Master), взаимодействуя с одним или несколькими ведомыми блоками (Slave). Схема передачи данных по интерфейсу SPI микроконтроллеров AVR/PIC показана на рис. 7.6 (MSB – старший разряд, a LSB – младший разряд передаваемого байта).

Рис. 7.6. Схема передачи данных по интерфейсу SPI микроконтроллеров AVR/PIC

Ведущее устройство берет на себя активную часть обмена данными, вызывая передачу и управляя процессом. Ведомое устройство не может само быть активным. Оно принимает и передает данные только тогда, когда происходит его активизация со стороны ведущего устройства по линии /SS. Ведущее устройство также генерирует такт для передачи по выходной линии SCK. Для ведомого блока вывод SCK является входом, через который он получает от Master-устройства тактирующие сигналы.

Если ведомое устройство активизируется ведущим по линии /SS, то начинается обмен данными: Master записывает подлежащий передаче байт в свой сдвиговой регистр данных (для микроконтроллеров AVR – регистр SPDR, для микроконтроллеров PIC – регистр SSPBUF). С помощью каждого выработанного тактового импульса Master перемещает один бит данных на выход MOSI/SDO, a Slave одновременно в обратном направлении передает один бит на вход MISO/SDI ведущего блока. Таким образом, в течение цикла SPI, состоящего из восьми тактовых импульсов, Master и Slave обмениваются байтом данных.

По окончании передачи данных в регистре состояния интерфейса SPI устанавливается флаг соответствующего запроса на прерывание. Этот флаг указывает на окончание передачи и вызывает запрос на прерывание после того как в регистре управления SPI будет установлен разряд разрешения на прерывание от интерфейса SPI. В режиме "Master" текущая передача данных может быть преждевременно завершена выдачей в линию /SS сигнала лог. 1.

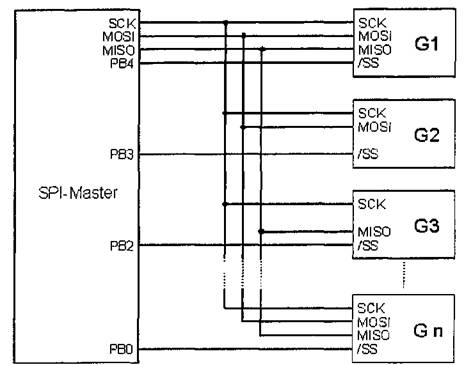

К интерфейсу SPI ведущего устройства можно подключать несколько ведомых устройств (пример для микроконтроллеров AVR – на рис. 7.7), однако активным будет только то из них, на вход /SS которого будет подан уровень лог. 0. Выходы MISO незадействованных ведомых блоков находятся в высокоомном состоянии и не влияют на процесс передачи данных.

В примере на рис. 7.7 устройство G2, с точки зрения ведущего устройства, является только блоком передачи (например, ЦАП с интерфейсом SPI), а устройство G3 – только блоком приема.

Рис. 7.7. Подключение нескольких ведомых устройств к одному ведущему по SPI (для AVR)