|

Раздел |

Содержание: |

Стр. |

|

1 |

Постановка задачи |

3 |

|

2 |

Введение |

3 |

|

3 |

Общий принцип работы однонаправленного буфера типа FIFO |

4 |

|

4 |

Проектирование буфера FIFO |

7 |

|

4.1 |

Схема электрическая структурная |

7 |

|

4.2 |

Построение блока регистровой памяти |

8 |

|

4.2.1 |

Техническое описание микросхемы КР1533ИР32 |

8 |

|

4.2.2 |

Расположение и назначение выводов микросхемы КР1533ИР32 |

9 |

|

4.2.3 |

Функциональная схема микросхемы КР1533ИР32 |

11 |

|

4.2.4 |

Увеличение числа разрядов |

12 |

|

4.2.5 |

Функциональная схема блока регистровой памяти |

14 |

|

4.3 |

Построение компаратора |

15 |

|

4.3.1 |

Проектирование компаратора |

15 |

|

4.3.2 |

Техническое описание микросхемы КР1533ЛП5 |

16 |

|

4.3.3 |

Расположение и назначение выводов микросхемы КР1533ЛП5 |

16 |

|

4.3.4 |

Техническое описание микросхемы КР1533ЛН1 |

17 |

|

4.3.5 |

Расположение и назначение выводов микросхемы КР1533ЛН1 |

17 |

|

4.3.6 |

Техническое описание микросхемы КР1533ЛИ3 |

18 |

|

4.3.7 |

Расположение и назначение выводов микросхемы КР1533ЛИ3 |

19 |

|

4.3.8 |

Построение электрической схемы компаратора |

20 |

|

4.4 |

Построение счетчиков |

20 |

|

4.4.1 |

Проектирование счетчика |

20 |

|

4.4.2 |

Техническое описание микросхемы КР1533ИЕ19 |

21 |

|

4.4.3 |

Функциональная схема микросхемы КР1533ИЕ19 |

22 |

|

4.4.4 |

Расположение и назначение выводов микросхемы КР1533ИЕ19 |

23 |

|

4.5 |

Построение буферного индикатора |

24 |

|

4.5.1 |

Проектирование буферного индикатора |

24 |

|

4.5.2 |

Функциональная схема буферного индикатора |

24 |

|

4.5.3 |

Техническое описание микросхемы КР1533ЛА3 |

25 |

|

4.5.4 |

Расположение и назначение выводов микросхемы КР1533ЛА3 |

25 |

|

4.5.5 |

Построение электрической схемы буферного индикатора |

26 |

|

5 |

Построение устройства |

27 |

|

5.1 |

Создание эквивалентной схемы устройства |

27 |

|

5.2 |

Создание принципиальной схемы устройства |

29 |

|

5.3 |

Перечень элементов |

30 |

|

5.4 |

Схема электрическая |

31 |

|

6 |

Расчет параметров устройства |

31 |

|

6.1 |

Токи и потенциалы |

31 |

|

6.2 |

Согласование входов и выходов микросхем |

31 |

|

6.3 |

Потребляемая мощность |

32 |

|

Литература |

33 |

1. Постановка задачи

Разработать принципиальную схему буфера FIFO4сл.×8р. на элементах серии К1533. Регистровую память разработать на основе микросхемы КР1533ИР32.

2. Введение

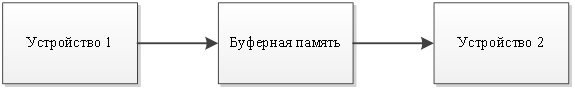

Важнейшим применением микросхем оперативной памяти является организация разнообразных информационных буферов, то есть буферной памяти для промежуточного хранения данных, передаваемых между двумя устройствами или системами. Суть информационного буфера состоит в следующем: передающее устройство записывает передаваемые данные в буфер, а принимающее устройство читает принимаемые данные из буфера (рис. 1).

Рис. 1 Включение буферной памяти

Такое промежуточное хранение позволяет лучше скоординировать работу устройств, участвующих в обмене данными, повысить их независимость друг от друга, согласовать скорости передачи и приёма данных.

Главное отличие буферной памяти от памяти для временного хранения информации состоит в том, что к информационному буферу всегда имеют доступ не одно внешнее устройство, а два (или даже более).

Информационные буферы могут обеспечивать периодический или непрерывный обмен между устройствами. Примером буфера с непрерывным режимом обмена может служить контроллер видеомонитора.

Информационные буферы с периодическим режимом обмена могут быть организованы по типу FIFO или по типу LIFO. В случае FIFO массив данных читается из памяти одним устройством в том же порядке, в каком он был записан в память другим устройством. В случае информационного буфера LIFO массив данных читается из памяти в порядке, противоположном тому, в котором он был записан в память.

3. Общий принцип работы однонаправленного буфера типа FIFO

Для организации обычной очерёдности служит буфер типа очередь, или буфер FIFO (first in — first out — первым вошёл, первым вышел, читается «фифо»). Необходимость в таком буфере возникает, когда источник данных поставляет приёмнику слова, распределённые во времени нерегулярно, причём интервалы времени между некоторыми словами могут быть меньше, чем время, необходимое приёмнику для обработки одного слова. Если потери информации недопустимы, то между источником и приёмником включается буфер FIFO, в котором хранится очередь слов, ожидающих обработки.

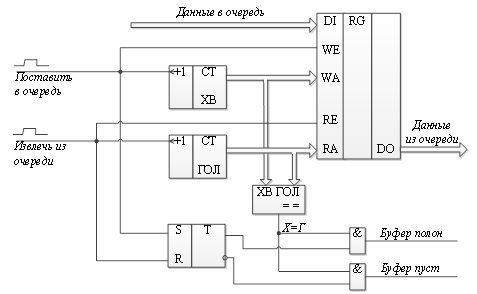

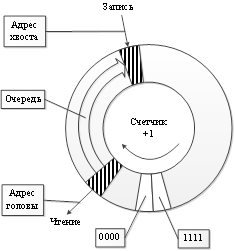

Схема буфера типа «очередь», построенного на основе регистровой памяти, показана на рис. 2,а. На рис. 2,б набор регистров памяти, т. е. адреса памяти показаны в виде кольца. Часть регистров занята очередью, остальные ? свободный резерв на случай её увеличения. Адрес записи при постановке в очередь задаётся счётчиком хвоста очереди СТ ХВ. Сигнал «Поставить в очередь», поступая на вход WE разрешения записи, записывает поступившие по входной шине DI данные в тот регистр памяти, номер которого хранится в СТ ХВ. По срезу сигнала «Поставить в очередь» выходной код счётчика хвоста увеличивается на 1, подготавливая адрес записи для очередного сигнала «Поставить в очередь».

При поступлении сигнала «Извлечь из очереди» на выходной шине DO появляется слово, хранящееся в том регистре памяти, номер которого задан кодом счётчика головы очереди СТ ГОЛ. По срезу сигнала выходной код счётчика увеличится на 1, подготовив для выдачи следующее слово, ставшее теперь первым в очереди. Переполнение счётчика хвоста очереди осложнений не вызовет, поскольку после максимально возможного кода счётчика ВСЕ ЕДИНИЦЫ в нем автоматически появится код ВСЕ НУЛИ. Очередь в своём кольце просто переползёт хвостом через нулевую отметку счётчика. Так же со временем переползёт и голова. В процессе нормальной работы очередь двигается в кольце значений адресов по часовой стрелке, хвостом вперёд, удлиняясь или укорачиваясь в соответствии с флюктуациями активности передатчика. Перед началом работы оба счётчика сбрасываются в нуль.

а)

б)

а — функциональная схема; б — диаграмма использования адресов

Рис. 2. Буфер типа «очередь» (буфер FIFO):

Схема буфера FIFO должна сигнализировать о двух особых ситуациях. Первая — буфер полон, тогда в него нельзя больше записывать, и нужно приостановить передатчик. Вторая — буфер пуст, тогда из него нельзя брать данные, и нужно приостановить приёмник.

Обе ситуации имеют общий признак: равенство показаний обоих счётчиков после исчезновения входного сигнала. Этот признак выявляет компаратор. Если счётчики стали равны после очередного извлечения из очереди, то это значит, что очередь иссякла, буфер пуст. Если они стали равны после очередной постановки в очередь, то буфер полон. Характер последнего обращения к буферу запоминается в RS-триггере. Сигналы, информирующие устройство управления об особых состояниях буфера, получаются как конъюнкции того или иного состояния триггера и признака равенства показаний счётчиков головы и хвоста.

4. Проектирование буфера FIFO

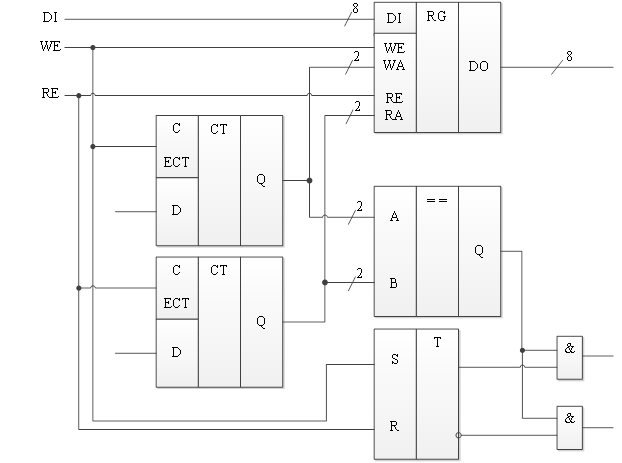

4.1 Схема электрическая структурная

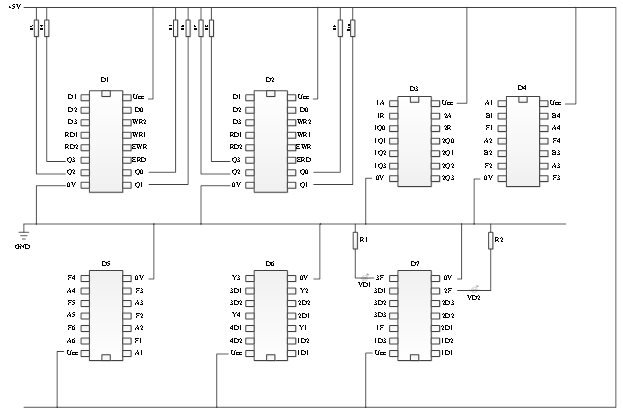

Рис. 3. Буфер FIFO.Схема электрическая структурная.

Для того чтобы разработать принципиальную схему буфера FIFOс регистровой памятью 4сл.×8р. на основе микросхемы КР1533ИР32 (4сл.×4р.), необходимо нарастить число разрядов.

4.2 Построение блока регистровой памяти.

4.2.1. Техническое описание микросхемы КР1533ИР32

Микросхема КР1533ИР32 представляет собой регистровый файл на четыре четырехразрядных слова. Обеспечивается раздельное декодирование и адресация четырех слов как для записи, так и для считывания информации, что позволяет записывать данные по одному адресу и считывать по другому.

Микросхема имеет четыре информационных входа D0-D3, используемые для записи четырехразрядных слов. Адрес разряда регистрового файла определяется адресными входами WR1, WR2 совместно с низким уровнем напряжения на входе EWR. Чтение информации, хранящейся в регистрах, происходит при наличии низкого уровня напряжения на входе ERD, адрес чтения задается входами RD1, RD2. При высоком уровне напряжения на входе EWRв регистровом файле сохраняется предыдущая информация, а при высоком уровне напряжения на входе ERD выходы микросхемы переводятся в состояние высокого уровня напряжения.

Выходы микросхемы КР1533ИР32 выполнены в виде открытого коллектора, что позволяет использовать её при работе на магистраль, а также объединять несколько выходов для получения функции «Монтажное И». Время переключения выхода микросхемы из низкого уровня напряжения в высокий определяется в основном внешним резистором и ёмкостью нагрузки.

|

WR1 |

WR2 |

EWR |

Номер слова |

|||

|

W0 |

W1 |

W2 |

W3 |

|||

|

L |

L |

L |

Q=D |

Qn |

Qn |

Qn |

|

L |

H |

L |

Qn |

Q=D |

Qn |

Qn |

|

H |

L |

L |

Qn |

Qn |

Q=D |

Qn |

|

H |

H |

L |

Qn |

Qn |

Qn |

Q=D |

|

X |

X |

H |

Qn |

Qn |

Qn |

Qn |

Таблица 1. Таблица истинности в режиме записи.

|

RD1 |

RD2 |

ERD |

Номер слова |

|||

|

Q0 |

Q1 |

Q2 |

Q3 |

|||

|

L |

L |

L |

W0B1 |

W0B2 |

W0B3 |

W0B4 |

|

L |

H |

L |

W1B1 |

W1B2 |

W1B3 |

W1B4 |

|

H |

L |

L |

W2B1 |

W2B2 |

W2B3 |

W2B4 |

|

H |

H |

L |

W3B1 |

W3B2 |

W3B3 |

W3B4 |

|

X |

X |

H |

H |

H |

H |

H |

Таблица 2. Таблица истинности в режиме считывания.

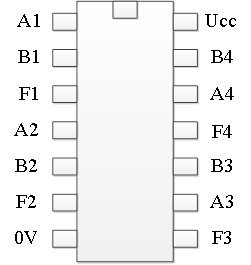

4.2.2. Расположение и назначение выводов микросхемы КР1533ИР32

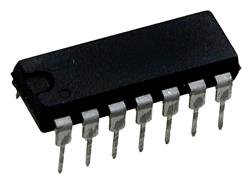

Микросхема КР1533ИР32 выполнена в стандартном корпусе 238.16-1 (DIP16). На Рис. 4. Представлен внешний вид микросхемы.

Рис. 4. Внешний вид микросхемы КР1533ИР32.

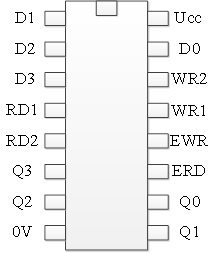

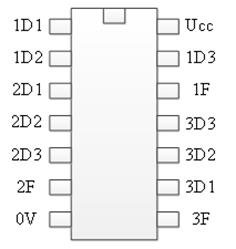

Микросхема имеет 16 выводов, которые нумеруются против часовой стрелки относительно метки. Расположение выводов и их назначение представлены на Рис. 5. и Таблице 3. соответственно.

Рис. 5. Расположение выводов микросхемы КР1533ИР32.

|

01 |

D1 |

Вход информационный |

|

02 |

D2 |

Вход информационный |

|

03 |

D3 |

Вход информационный |

|

04 |

RD1 |

Вход выбора адреса считывания |

|

05 |

RD2 |

Вход выбора адреса считывания |

|

06 |

Q3 |

Выход информационный |

|

07 |

Q2 |

Выход информационный |

|

08 |

0V |

Общий вывод |

|

09 |

Q1 |

Выход информационный |

|

10 |

Q0 |

Выход информационный |

|

11 |

ERD |

Вход разрешения считывания |

|

12 |

EWR |

Вход разрешения записи |

|

13 |

WR1 |

Вход выбора адреса записи |

|

14 |

WR2 |

Вход выбора адреса записи |

|

15 |

D0 |

Вход информационный |

|

16 |

Ucc |

Напряжение питания |

Таблица 3. Таблица назначения выводов.

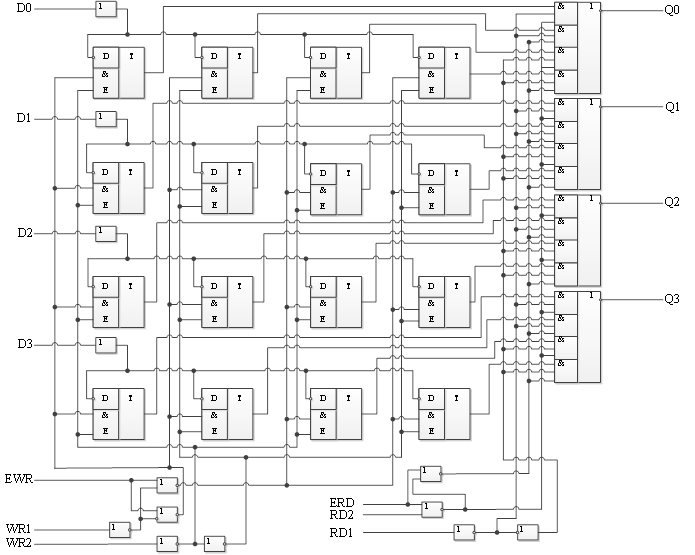

4.2.3. Функциональная схема микросхемы КР1533ИР32

На Рис. 6. показана функциональная схема микросхемы КР1533ИР32.

Рис. 6. Функциональная схема микросхемы КР1533ИР32.

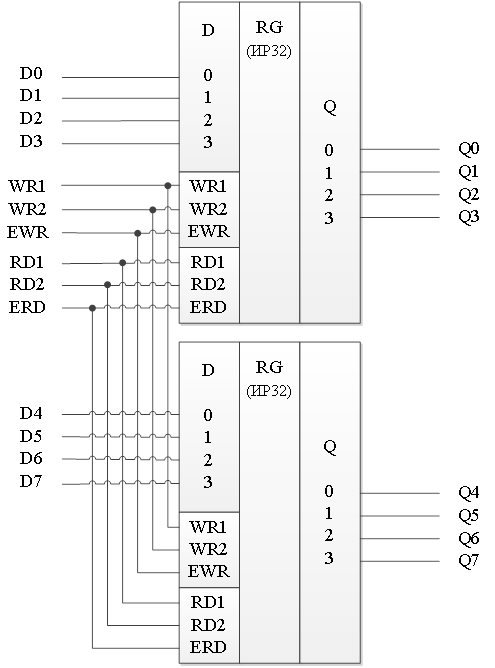

4.2.4. Увеличение числа разрядов

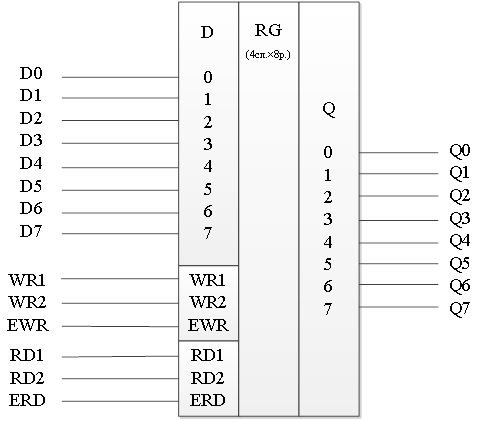

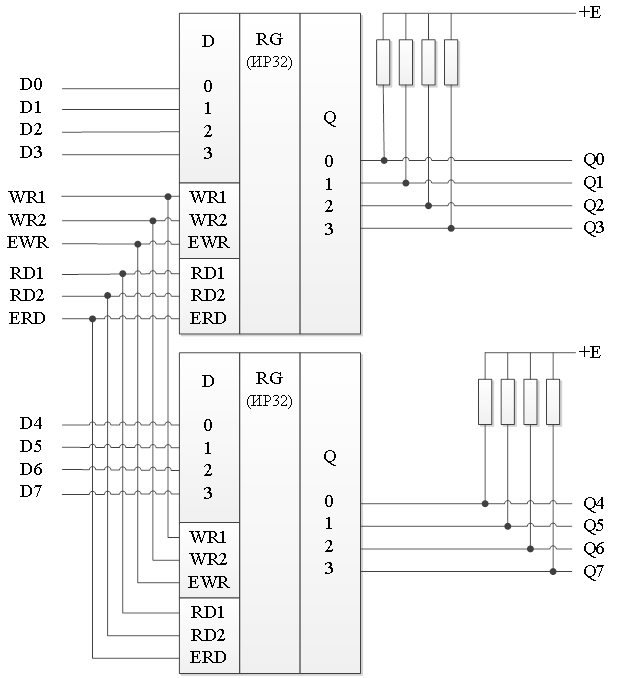

Задача увеличения числа разрядов заключается в следующем: из данного регистрового файла 4сл.×4р построить регистровую память 4сл.×8р. На рис.7 показан принцип увеличения числа разрядов для рассматриваемой микросхемы КР1533ИР32.

Рис. 7. Увеличение числа разрядов регистровой памяти с 4сл.×4р. до 4сл.×8р.

На рис.8 показана эквивалентная схема регистровой памяти 4сл.×8р.

Рис. 8. Эквивалентная схема регистрового файла 4сл.×8р.

4.2.5 Функциональная схема блока регистровой памяти

Рис. 9. Функциональная схема блока регистровой памяти.

Перечень используемых микросхем в блоке регистровой памяти:

Микросхема КР1533ИР32 – 2 шт.,

Резистор С2-23-0.125 4,7 кОм – 8 шт.;

4.3. Построение компаратора

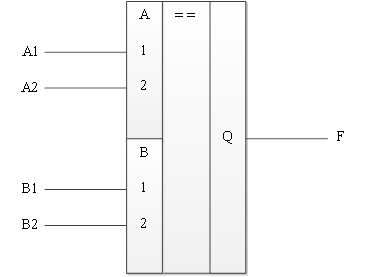

4.3.1. Проектирование компаратора

Компаратор, или устройство сравнения, определяет отношения между двумя двоичными словами. Для проектируемого FIFO в компараторе основным отношением является «равно». Поэтому определим эту функцию и построим нужный компаратор, так как в серии 1533 нет специализированной микросхемы, реализующей функцию сравнения.

Таблица функции «равно» для сравнения слов длиной 3 представлена ниже (Таблица 4). В таблице выпишем только те наборы переменных, где функция принимает значение 1.

|

А1 |

А2 |

В1 |

В2 |

F |

|

0 |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

1 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

Таблица 4. Таблица функции «равно».

Выписав СДНФ функции F и сгруппировав слагаемые, получим:

![]()

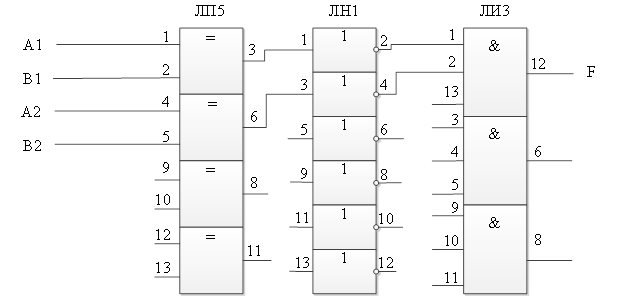

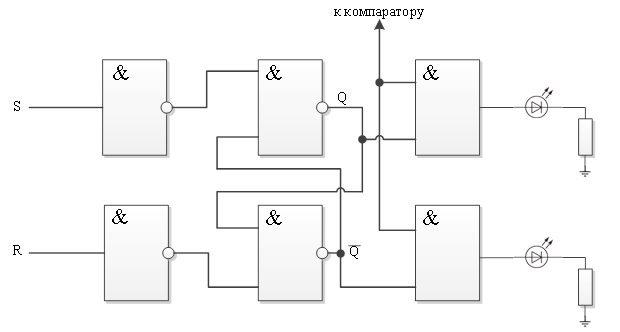

На рис.10 представлена эквивалентная схема компаратора.

Рис. 10. Эквивалентная схема компаратора

4.3.2. Техническое описание микросхемы КР1533ЛП5

Микросхема КР1533ЛП5 представляет собой четыре двухвходовых логических элементов «Исключающее ИЛИ». На Таблице 5 показана таблица истинности.

|

Вход |

Выход |

|

|

A |

B |

F |

|

L |

L |

L |

|

L |

H |

H |

|

H |

L |

H |

|

H |

H |

L |

Таблица 5. Таблица истинности микросхемы КР1533ЛП5.

4.3.3. Расположение и назначение выводов микросхемы КР1533ЛП5

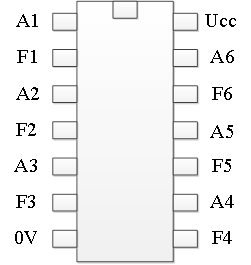

Микросхема КР1533ЛП5 выполнена в стандартном корпусе 2102Ю (DIP14). На Рис. 11. Представлен внешний вид микросхемы.

Рис. 11. Внешний вид микросхемы КР1533ЛП5.

Микросхема имеет 14 выводов, которые нумеруются против часовой стрелки относительно метки. Расположение выводов представлено на Рис. 12.

Рис. 12. Расположение выводов микросхемы КР1533ЛП5.

4.3.4. Техническое описание микросхемы КР1533ЛН1

Микросхема КР1533ЛН1 представляет собой шесть логических элементов «НЕ». На Таблице 6 показана таблица истинности.

|

Вход |

Выход |

|

A |

F |

|

L |

H |

|

H |

L |

Таблица 6. Таблица истинности микросхемы КР1533ЛН1.

4.3.5. Расположение и назначение выводов микросхемы КР1533ЛН1

Микросхема КР1533ЛН1 выполнена в стандартном корпусе 2102Ю (DIP14). На Рис. 13. Представлен внешний вид микросхемы.

Рис. 13. Внешний вид микросхемы КР1533ЛН1.

Микросхема имеет 14 выводов, которые нумеруются против часовой стрелки относительно метки. Расположение выводов представлено на Рис. 14.

Рис. 14. Расположение выводов микросхемы КР1533ЛН1.

4.3.6. Техническое описание микросхемы КР1533ЛИ3

Микросхема КР1533ЛИ3 содержит три идентичных логических элемента со стандартными активными выходами, выполняющих Булевы функции F=D1·D2·D3. На Таблице 7 показана таблица истинности.

|

D1 |

D2 |

D3 |

F |

|

H |

H |

H |

H |

|

L |

H |

H |

L |

|

H |

L |

H |

L |

|

L |

L |

H |

L |

|

H |

H |

L |

L |

|

L |

H |

L |

L |

|

H |

L |

L |

L |

|

L |

L |

L |

L |

Таблица 7. Таблица истинности микросхемы КР1533ЛИ3.

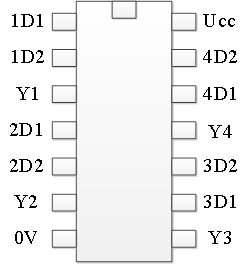

4.3.7. Расположение и назначение выводов микросхемы КР1533ЛИ3

Микросхема КР1533ЛИ3 выполнена в стандартном корпусе 2102Ю (DIP14). На Рис. 15. Представлен внешний вид микросхемы.

|

|

|

|

Рис. 15. Внешний вид микросхемы КР1533ЛИ3. |

Рис. 16. Расположение выводов микросхемы КР1533ЛИ3. |

Микросхема имеет 14 выводов, которые нумеруются против часовой стрелки относительно метки. Расположение выводов представлено на Рис. 16.

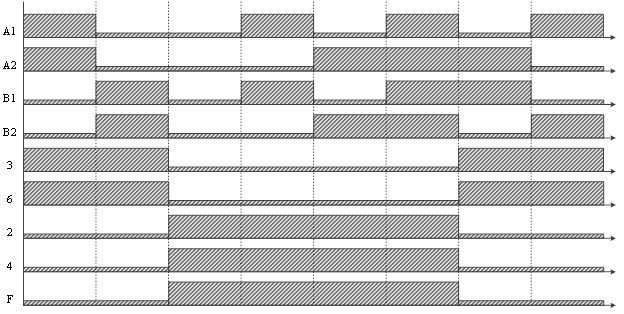

Рис. 17. Временная диаграмма работы компаратора.

4.3.8. Построение электрической схемы компаратора

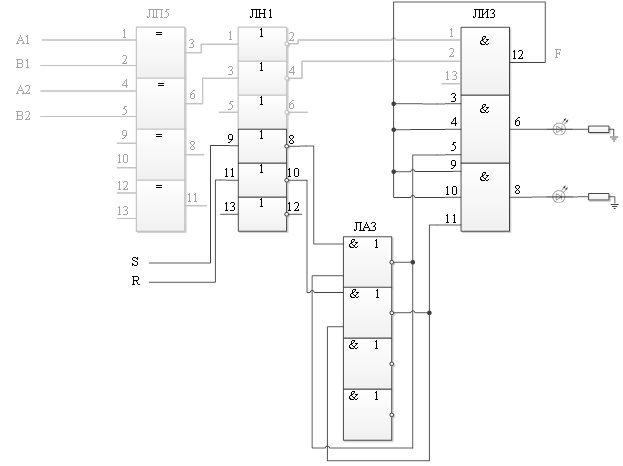

Рис. 18. Компаратор. Схема электрическая функциональная.

Перечень используемых микросхем в блоке компаратора:

Микросхема КР1533ЛП5 – 1 шт.,

Микросхема КР1533ЛН1 – 1 шт.,

Микросхема КР1533ЛИ3 – 1 шт.;

4.4. Построение счетчиков

4.4.1. Проектирование счетчика

Для создания адресного пространства, требуется создать счетчики, которые будут определять адрес входящих и выходящих слов. Для создания счетчиков будем использовать микросхему КР1533ИЕ19.

Рис. 19. Эквивалентная схема счетчика

4.4.2. Техническое описание микросхемы КР1533ИЕ19

Микросхема КР1533ИЕ19 представляет собой два идентичных двоичных четырехразрядных счетчика с индивидуальными входами тактирования и сброса. Сброс счетчика в исходное состояние (0000) происходит при подаче высокого уровня напряжения на вход R. При низком уровне напряжения на входе Rпереключение выходов счетчика происходит по отрицательному фронту тактового импульса на входе A.

На Таблице 8 показана таблица истинности микросхемы КР1533ИЕ19.

|

Счет |

Выход |

|||

|

Q3 |

Q2 |

Q1 |

Q0 |

|

|

0 |

L |

L |

L |

L |

|

1 |

L |

L |

L |

H |

|

2 |

L |

L |

H |

L |

|

3 |

L |

L |

H |

H |

|

4 |

L |

H |

L |

L |

|

5 |

L |

H |

L |

H |

|

6 |

L |

H |

H |

L |

|

7 |

L |

H |

H |

H |

|

8 |

H |

L |

L |

L |

|

9 |

H |

L |

L |

H |

|

10 |

H |

L |

H |

L |

|

11 |

H |

L |

H |

H |

|

12 |

H |

H |

L |

L |

|

13 |

H |

H |

L |

H |

|

14 |

H |

H |

H |

L |

|

15 |

H |

H |

H |

H |

Таблица 8. Таблица истинности микросхемы КР1533ИЕ19.

4.4.3. Функциональная схема микросхемы КР1533ИЕ19

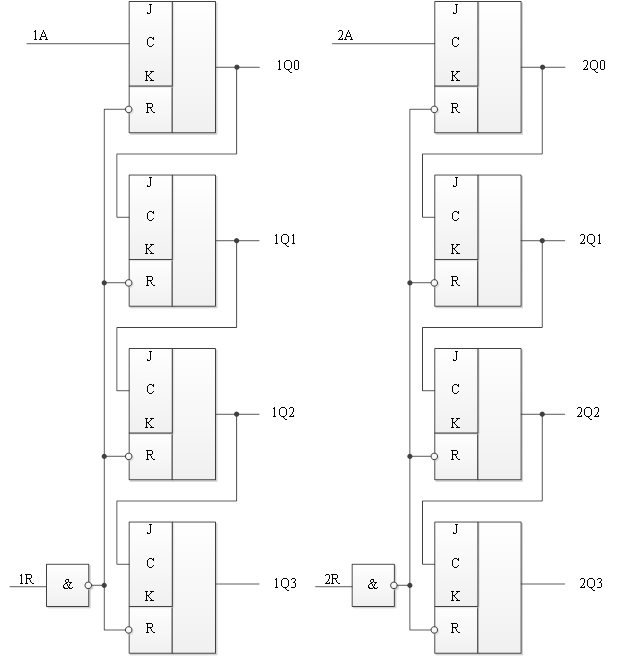

На Рис. 20. показана функциональная схема микросхемы КР1533ИЕ19

Рис. 20.Функциональная схема микросхемы КР1533ИЕ19.

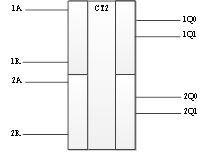

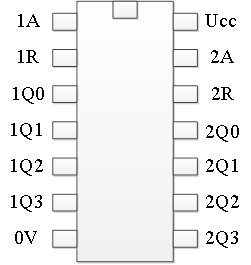

4.4.4. Расположение и назначение выводов микросхемы КР1533ИЕ19

Микросхема КР1533ИЕ19 выполнена в стандартном корпусе 2102Ю (DIP14). На Рис. 21. Представлен внешний вид микросхемы.

Рис. 21. Внешний вид микросхемы КР1533ИЕ19

Микросхема имеет 14 выводов, которые нумеруются против часовой стрелки относительно метки. Расположение выводов представлено на Рис. 22.

Рис. 22. Расположение выводов микросхемы КР1533ИЕ19.

Перечень используемых микросхем в блоке счетчика:

Микросхема КР1533ИЕ19 – 1 шт.;

4.5. Построение буферного индикатора

4.5.1. Проектирование буферного индикатора

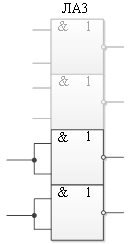

Для построения буферного индикатора, нам необходимо два логических элемента «И» и RS-триггер. Также, для визуального отображения заполнения или освобождения буфера, будем использовать светодиоды.

Учитывая тот факт, что после построения компаратора, некоторые логические элементы были не задействованы, то используем их для построения буферного индикатора.

4.5.2. Функциональная схема буферного индикатора

Рис. 23. Функциональная схема буферного индикатора.

4.5.3. Техническое описание микросхемы КР1533ЛА3

Микросхема содержит четыре идентичных логических элемента со стандартными активными выходами, выполняющих функции «И-НЕ». На Таблице 9 показана таблица истинности микросхемы.

|

D1 |

D2 |

F |

|

H |

H |

L |

|

H |

L |

H |

|

L |

H |

H |

|

L |

L |

H |

Таблица 9. Таблица истинности микросхемы.

4.5.4. Расположение и назначение выводов микросхемы КР1533ЛА3

Микросхема КР1533ЛА3 выполнена в стандартном корпусе 2102Ю (DIP14). На Рис. 24. Представлен внешний вид микросхемы.

Рис. 24. Внешний вид микросхемы КР1533ЛА3.

Микросхема имеет 14 выводов, которые нумеруются против часовой стрелки относительно метки. Расположение выводов представлено на Рис. 25.

Рис. 25. Расположение выводов микросхемы КР1533ЛА3.

4.5.5. Построение электрической схемы буферного индикатора

Как указывалось ранее, логические элементы «НЕ» и «И», будем использовать из незадействованных элементов в компараторе.

Рис. 26. Буферный индикатор. Схема электрическая функциональная.

На Рис. 26 показана электрическая схема буферного индикатора. Серым цветом указаны элементы компаратора.

Перечень используемых микросхем в блоке буферного индикатора:

Микросхема КР1533ЛА3 – 1 шт.,

Резистор 180 Ом C1-4-0.25 – 2 шт.,

Светодиод АЛ336В – 2 шт.;

5. Построение устройства

5.1. Создание эквивалентной схемы устройства

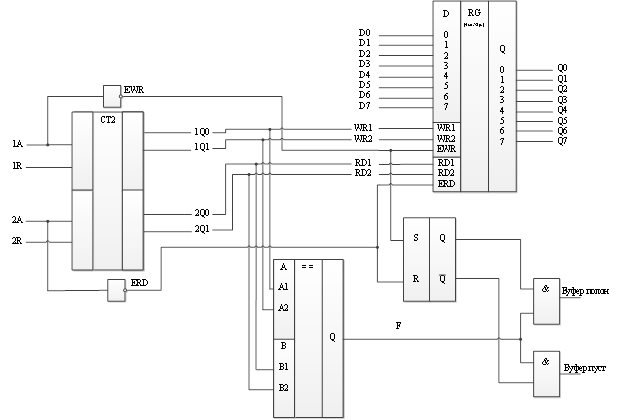

На Рис. 27. показана общая эквивалентная схема устройства.

Рис. 27. Общая эквивалентная схема устройства.

Для согласования сигналов EWR, ERDи входящих сигналов счетчика потребовалось использовать логическое «НЕ» т.к. EWRи ERD срабатывают по «низкому» уровню сигнала, а вход счетчика по «высокому». Т.к. свободный элемент «НЕ» всего один, то воспользуемся элементами «И-НЕ» как показано на Рис. 28.

Серым цветом отмечены части микросхемы, которые уже используются в блоке буферного индикатора.

Рис. 28. Использование элемента «И-НЕ» для создания элемента «НЕ».

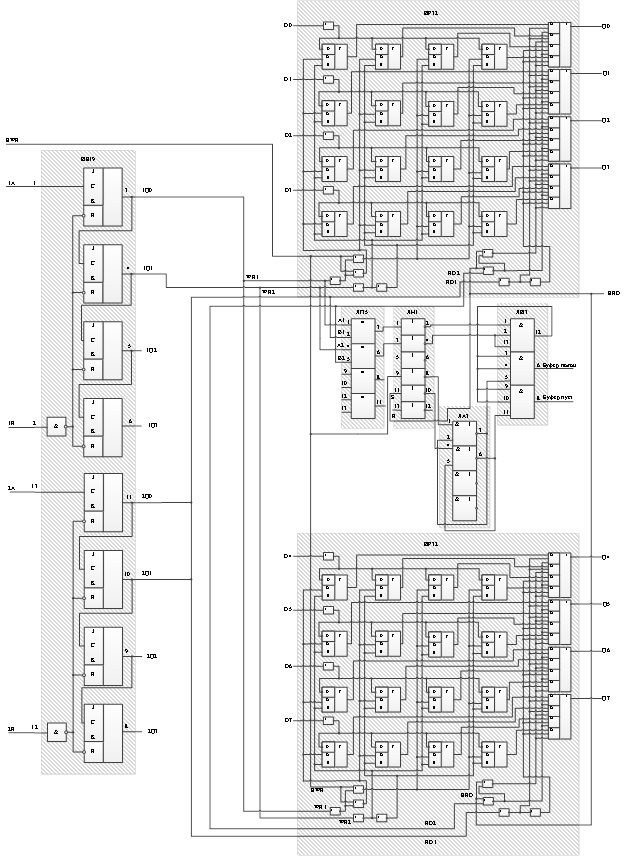

5.2. Создание принципиальной схемы устройства

Рис. 29. Принципиальная схема устройства.

На Рис. 29. представлена принципиальная схема устройства с указанием всех входов и выходов, а так же указанием всех составляющих элементов.

5.3 Перечень элементов

|

№ |

Обозначение |

Наименование |

Количество |

|

1 |

D1, D2 |

Регистровый файл на четыре четырёхразрядных слова КР1533ИР32 |

2 шт. |

|

2 |

D3 |

Два двоичных четырехразрядных счетчика на базе микросхемы КР1533ИЕ19 |

1 шт. |

|

3 |

D4 |

Четыре независимых логических элемента «Исключающее ИЛИ» на базе микросхемы КР1533ЛП5 |

1 шт. |

|

4 |

D5 |

Шесть логических элементов «НЕ» на базе микросхемы КР1533ЛН1 |

1 шт. |

|

5 |

D6 |

Четыре логических элемента «2-И-НЕ» на базе микросхемы КР1533ЛА3 |

1 шт. |

|

6 |

D7 |

Три логических элемента «3-И» на безе микросхемы КР1533ЛИ3 |

1 шт. |

|

7 |

VD1, VD2 |

Светодиод «Зеленый» |

2 шт. |

|

8 |

R1, R2 |

Резистор 180 Ом |

2 шт. |

|

9 |

R3-R10 |

Резистор 4,7 кОм |

8 шт. |

Таблица 10. Таблица перечня элементов.

5.4. Схема электрическая

Рис. 30. Электрическая схема устройства

6. Расчет параметров устройства

6.1 Токи и потенциалы

В спроектированном устройстве регистровой памяти используется серия К1533. Напряжение питания данной серии Uпит.=+5В±10%. Входные и выходные логические уровни сигналов совместимы внутри одной серии, в данном случае 1533.

6.2 Согласование входов и выходов микросхем

Все элементы данного устройства принадлежат одной серии 1533, это значит, что емкостные параметры входов и выходов согласованны.

6.3 Потребляемая мощность

Расчёт потребляемой мощности производится в следующем порядке. Сначала в справочных данных находятся значения потребляемых токов Iпотр. для каждой микросхемы. Далее рассчитывается потребляемая мощность одной микросхемы данного типа. Затем полученное значение помножается на число таких микросхем в устройстве. Полученные значения складываются между собой, образуя суммарную потребляемую мощность.

Pпотр. = Iпотр. х Uпит.

|

Тип |

Потребляемый ток |

Количество |

Мощность |

|

ИР32 |

34 мА |

2 |

340 мВт |

|

ИЕ19 |

24 мА |

1 |

120 мВт |

|

ЛП5 |

5,9 мА |

1 |

29,5 мВт |

|

ЛН1 |

1,1 мА |

1 |

5,5 мВт |

|

ЛА3 |

3 мА |

1 |

15 мВт |

|

ЛИ3 |

3 мА |

1 |

15 мВт |

|

АЛ336В |

20 мА |

2 |

80 мВт |

|

C1-4-0.25 |

50 мА |

2 |

500 мВт |

|

С2-23-0.125 |

25 мА |

8 |

1000 мВт |

Таблица 11. Таблица результатов расчёта

Итого общая мощность схемы получилась = 2105 мВт.

Литература

1. Бойко В.М. Схемотехника электронных систем. Цифровые устройства В.М. Бойко, А.Н. Гуржий, В.Я. Жуйков, А.А. Зори, В.М. Спивак, В.В. Багрий ? СПб.: БХВ-Петербург, 2004.-512 с.

2. Браммер, Ю.А. Цифровые устройства: Учеб. пособие для вузов Ю. А. Браммер, И.Н. Пащук М.: Высш. шк., 2004. ?229 с.

3. Китаев, Ю.В. Основы цифровой техники. Учебное пособие: Ю.В. Китаев. ? СПб: СПбГУ ИТМО, 2007, 87 с.

4. Мурашко, И.А. ЭВМ и периферийные устройства: Курс лекций по одноименной дисциплине для студентов специальности «Информационные системы и технологии» И.А. Мурашко. – Гомель: ГГТУ имени П.О. Сухого, 2011. – 101 с.

5. Нефёдов А.В. Интегральные микросхемы и их зарубежные аналоги: Справочник Т. 10. А.В. Нефёдов – М.: ИП РадиоСофт, 2001. – 544 с.

6. Петровский И.И. Логические ИС КР1533, КР1554. Справочник. И.И. Петровский, А.В. Прибыльский, А.А. Троян, В.С. Чувелев ? М: “БИНОМ”, 1998.

7. Угрюмов, Е.П. Цифровая схемотехника Е.П. Угрюмов. ? СПб.: БХВ-Петербург, 2004.-528с

0 комментариев